# CX77304-15

# PA Module for Dual-band GSM850 PCS1900 / GPRS Applications

The CX77304-15 Power Amplifier Module(PAM) is designed in a compact form factor for dual-band cellular handsets comprising GSM850 and PCS1900 operation. It also supports Class 10 General Packet Radio Service (GPRS) multislot operation.

The module consists of separate Heterojunction Bipolar Transistor (HBT) PA blocks for the GSM850 and PCS1900 bands, interface circuitry, and RF input and output ports internally matched for 50  $\Omega$  impedance to reduce the number of external components. The PA blocks are fabricated on a single Gallium Arsenide (GaAs) die and share common power supply pins for current distribution. Extremely low leakage current (2  $\mu$ A, typical) of the dual PA module maximizes handset standby time.

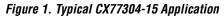

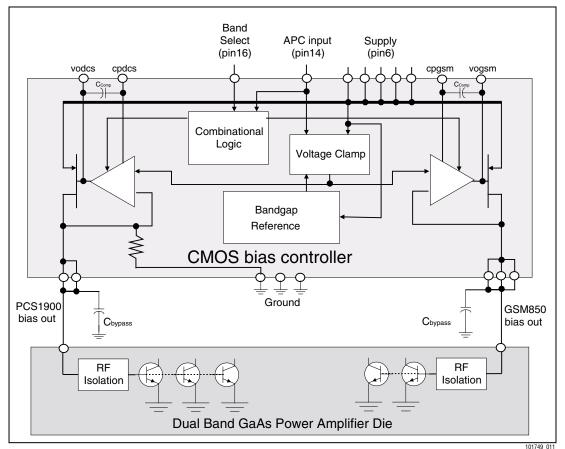

The CX77304-15 also contains band-select switching circuitry to select GSM (logic 0) and PCS (logic 1) as determined from the Band Select (BS) signal. In the block diagram shown below, the BS pin selects the PA output (PCS OUT or GSM OUT) while the Analog Power Control (APC) controls the level of output power.

A custom CMOS IC provides the internal interface circuitry including a current amplifier that minimizes the required power control current ( $I_{APC}$ ) to 10  $\mu$ A, typical. The GaAs die, the Silicon (Si) die, and passive components are mounted on a multi-layer laminate substrate and the assembly encapsulated with plastic overmold.

#### **Distinguishing Features**

- High efficiency

- GSM 55%

- PCS 45%

- Input/output internally matched to 50  $\Omega$

- Small outline 9.1 mm × 11.6 mm

- Low profile

1.5 mm maximum

- Low APC current 10 μA, typical

- · Gold plated, lead-free contacts

#### Applications

Dual-band cellular handsets encompassing Class 4 GSM850 PCS1900, and up to Class 10 GPRS multislot operation

### Functional Block Diagram

# **Electrical Specifications**

The following tables list the electrical characteristics of the CX77304-15 Power Amplifier. Table 1 lists the absolute maximum ratings and Table 2 shows the recommended operating conditions. Table 3 shows the electrical characteristics of the CX77304-15 for GSM and PCS modes. A typical CX77304-15 application diagram appears in Figure 1.

The CX77304-15 is a static-sensitive electronic device and should not be stored or operated near strong electrostatic fields. Detailed ESD precautions along with information on device dimensions, pin descriptions, packaging and handling can be found in later sections of this data sheet.

| Parameter                                        | Minimum | Maximum                                               | Unit |

|--------------------------------------------------|---------|-------------------------------------------------------|------|

| Input Power (P <sub>IN</sub> )                   | —       | 15                                                    | dBm  |

| Supply Voltage (Vcc), Standby, VAPC $\leq$ 0.3 V | —       | 7                                                     | V    |

| Control Voltage (VAPC)                           | -0.5    | V <sub>CC<sub>MAX</sub> – 0.2<br/>(See Table 3)</sub> | V    |

| Storage Temperature                              | -55     | +100                                                  | ٥°   |

#### Table 1. Absolute Maximum Ratings

| Parameter                                                                                                                                                        | Minimum                  | Typical      | Maximum               | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------|-----------------------|------|

| Supply Voltage (Vcc)                                                                                                                                             | 2.8                      | 3.2          | 4.6V <sup>(1)</sup>   | V    |

| Supply Current (Icc)                                                                                                                                             | 0                        | _            | 2.5 <sup>(1)</sup>    | А    |

| Operating Case Temperature (T <sub>CASE</sub> )<br>1-Slot (12.5% duty cycle)<br>2-Slot (25% duty cycle)<br>3-Slot (37.5% duty cycle)<br>4-Slot ( 50% duty cycle) | -20<br>-20<br>-20<br>-20 |              | 100<br>90<br>75<br>60 | °C   |

| <b>NOTE(S):</b><br>(1) For charging conditions with $V_{CC} > 4.6$ V, derate                                                                                     |                          | max at Voc – |                       |      |

#### Table 2. Recommended Operating Conditions

## Table 3. CX77304-15 Electrical Specifications<sup>(1)</sup> (1 of 3)

| Parameter                                     | Symbol                           | Test Condition                                                                                                                                                                                                                                                         | Min  | Typical | Max   | Units |

|-----------------------------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|-------|-------|

|                                               |                                  | General                                                                                                                                                                                                                                                                |      |         |       |       |

| Supply voltage                                | Vcc                              | _                                                                                                                                                                                                                                                                      | 2.8  | 3.2     | 4.6   | V     |

| Power Control Current                         | Iapc                             | _                                                                                                                                                                                                                                                                      |      | 10      | 100   | μA    |

| Leakage Current                               | Iq                               | $V_{CC} = 4.5 V$ $V_{APC} = 0.3 V$ $T_{CASE} = +25 \ ^{\circ}C$ $P_{IN} \leq -60 \ dBm$                                                                                                                                                                                | —    | _       | 5     | μA    |

| APC Enable Threshold                          | Vapc <sub>th</sub>               | _                                                                                                                                                                                                                                                                      | 200  | _       | 600   | mV    |

| APC Enable Switching Delay                    | tsw                              | $\begin{array}{l} \mbox{Time from } V_{\text{APC}} \geq V_{\text{APC}_{\text{TH}}} \mbox{ until } \\ \mbox{Pout} \leq (P_{\text{OUT}\_\text{FINAL}} - 3 \mbox{ dB}) \end{array}$                                                                                       | 5    |         | 8     | μs    |

|                                               | GSM Mode (f =                    | $= 824 \text{ to } 849 \text{ MHz} \text{ and } P_{IN} = 6 \text{ to } 10$                                                                                                                                                                                             | dBm) |         |       |       |

| Frequency range                               | f                                | —                                                                                                                                                                                                                                                                      | 824  | _       | 849   | MHz   |

| Input power                                   | Pin                              | _                                                                                                                                                                                                                                                                      | 6    | —       | 10    | dBm   |

| Analog power control voltage                  | Vapc                             | Роит = 32 dBm                                                                                                                                                                                                                                                          | 1.2  | 1.7     | 2.1   | V     |

| Power Added Efficiency                        | PAE                              | $\label{eq:Vcc} \begin{array}{l} V_{\text{Cc}} = 3.2 \ V \\ P_{\text{OUT}} \geq 34.0 \ dBm \\ V_{\text{APC}} \approx 2.0 \ V, \\ \texttt{pulse width 577 } \texttt{\mu}\texttt{s}, \\ \texttt{duty cycle 1:8} \\ T_{\text{CASE}} = +25 \ ^{\circ}\text{C} \end{array}$ | 50   | 55      | _     | %     |

| 2 <sup>nd</sup> to 13 <sup>th</sup> harmonics | 2fo to 13fo                      | BW = 3 MHz<br>5 dBm ≤ Pout ≤ 35 dBm                                                                                                                                                                                                                                    | —    |         | -7    | dBm   |

| Output power                                  | Роит                             | $\label{eq:Vcc} \begin{array}{l} V_{CC} = 3.2 \ V \\ V_{APC} \approx 2.0 \ V \\ T_{CASE} = +25 \ ^{\circ}C \end{array}$                                                                                                                                                | 34.0 | 34.5    | —     | dBm   |

|                                               | POUTMAX LOW VOLTAGE              | $V_{CC} = 2.8 V$ $V_{APC} \le 2.6 V$ $T_{CASE} = -20 \text{ °C to +100 °C}$ (See Table 2 for multislot) $P_{IN} = 6 \text{ dBm}$                                                                                                                                       | 32   | 33      | _     | dBm   |

|                                               | POUT <sub>MAX</sub> HIGH VOLTAGE | $V_{CC} = 4.6 V$ $V_{APC} \le 2.6 V$ $T_{CASE} = -20 \text{ °C to +100 °C}$ (See Table 2 for multislot) $P_{IN} = 6 \text{ dBm}$                                                                                                                                       | 32   | 33      | _     | dBm   |

| Input VSWR                                    | Γın                              | Pout = 5 to 35 dBm,<br>controlled by VAPC                                                                                                                                                                                                                              | -    | 1.5:1   | 2.2:1 | _     |

| Forward isolation                             | POUTSTANDBY                      | $P_{IN} = 10 \text{ dBm}$ $V_{APC} = 0.3 \text{ V}$                                                                                                                                                                                                                    | —    | -35     | -30   | dBm   |

| Parameter                                    | Symbol        | Test Condition                                                                                                                                                                                                             | Min             | Typical              | Max       | Units |

|----------------------------------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------------|-----------|-------|

| Spurious                                     | Spur          | No parasitic oscillation with all<br>combinations of the following<br>parameters:<br>$V_{APC} = controlled^{(2)}$<br>$P_{IN} = 10.0 \text{ dBm}$<br>$V_{CC} = 2.8 \text{ V to 4.6 V}$<br>Load VSWR = 6:1, all phase angles | _               |                      | -36       | dBm   |

| Output Power Switching Speed                 |               | $\pm$ step input of V_{APC} to RF output power within 1 dB of final value starting state: V_{APC} = 0.6 V                                                                                                                  | —               | _                    | 3 µs      | dBm   |

| Load mismatch                                | Load          | All combinations of the following<br>parameters:<br>$V_{APC} = controlled^{(2)}$<br>$P_{IN} = 10 \text{ dBm}$<br>$V_{CC} = 2.8 \text{ V to 4.6 V}$<br>Load VSWR = 10:1, all phase<br>angles                                | No mo<br>degrad | dule damage<br>ation | e or perm | anent |

| Noise power                                  | PNOISE        | At $f_0 + 20 \text{ MHz}$<br>T = 25  °C<br>RBW = 100 kHz<br>Vcc = 3.2 V<br>$P_{IN} = 6 \text{ dBm}$<br>$P_{OUT} = 34.0 \text{ dBm}$                                                                                        | _               | _                    | -84       | dBm   |

|                                              |               | At $f_0 + 10 \text{ MHz}$<br>$T = 25 ^{\circ}\text{C}$<br>RBW = 100  kHz<br>$V_{\text{CC}} = 3.2 \text{ V}$<br>$P_{\text{IN}} = 6 \text{ dBm}$<br>$P_{\text{OUT}} = 34.0 \text{ dBm}$                                      | _               | _                    | -76       | dBm   |

|                                              |               | At 1930 to 1990 MHz<br>RBW = 100 kHz<br>Vcc = 3.2 V<br>Pout = 34.0 dBm                                                                                                                                                     | _               | _                    | -90       | dBm   |

|                                              | PCS Mode (f : | = 1850 to 1910 MHz and P <sub>IN</sub> = 6 to 10                                                                                                                                                                           | dBm)            |                      |           |       |

| Frequency range                              | f             | —                                                                                                                                                                                                                          | 1850            | _                    | 1910      | MHz   |

| Input power                                  | Pin           | _                                                                                                                                                                                                                          | 6               | _                    | 10        | dBm   |

| Analog power control voltage                 | Vapc          | Роит = 29.5 dBm                                                                                                                                                                                                            | 1.35            | 1.7                  | 2.1       | V     |

| Power Added Efficiency                       | PAE           | $\label{eq:Vcc} \begin{array}{l} V_{CC} = 3.2 \ V \\ P_{OUT} \geq 32 \ dBm \\ V_{APC} \approx 2.0 \ V, \\ pulse \ width \ 577 \ \mu s, \\ duty \ cycle \ 1:8 \\ T_{CASE} = +25 \ ^{\circ}C \end{array}$                    | 42              | 45                   |           | %     |

| 2 <sup>nd</sup> to 7 <sup>th</sup> harmonics | 2fo to 7fo    | $\begin{array}{l} BW=3\;MHz\\ 5\;dBm\leqP_{OUT}\leq32\;dBm \end{array}$                                                                                                                                                    | —               | _                    | -7        | dBm   |

### Table 3. CX77304-15 Electrical Specifications<sup>(1)</sup> (2 of 3)

### Table 3. CX77304-15 Electrical Specifications<sup>(1)</sup> (3 of 3)

| Parameter         | Symbol                                  | Test Condition                                                                                                                                                                                                             | Min                                         | Typical | Мах   | Units |

|-------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|---------|-------|-------|

| Output power      | Роит                                    | $V_{CC} = 3.2 V$ $V_{APC} \approx 2.0 V$ $T_{CASE} = +25 \text{ °C}$                                                                                                                                                       | 32                                          | 32.5    | —     | dBm   |

|                   | POUT <sub>MAX LOW VOLTAGE</sub>         | $V_{CC} = 2.8 V$ $V_{APC} \le 2.6 V$ $T = 25 °C$ (See Table 2 for multislot) $P_{IN} = 6 \text{ dBm}$                                                                                                                      | 30.0                                        | 30.5    | _     | dBm   |

|                   | POUT <sub>MAX HIGH VOLTAGE</sub>        | $V_{CC} = 2.8 V$ $V_{APC} \le 2.6 V$ $T_{CASE} = -20 \text{ °C to +100 °C (See}$ $Table 2 \text{ for multislot)}$ $P_{IN} = 6 \text{ dBm}$                                                                                 | 29.0                                        | 30.5    | _     | dBm   |

| Input VSWR        | Γin                                     | Pout = 0 to 32 dBm<br>controlled by V <sub>APC</sub>                                                                                                                                                                       | —                                           | —       | 2:1   | _     |

| Forward isolation |                                         | $P_{IN} = 10 \text{ dBm}, V_{APC} = 0.3 \text{ V}$                                                                                                                                                                         | —                                           | -40     | -35   | dBm   |

| Switching time    | $\tau_{\text{rise}},\tau_{\text{fall}}$ | $\pm$ step input of V <sub>APC</sub> to RF output<br>power within 1 dB of final value<br>starting state: V <sub>APC</sub> = 0.6 V                                                                                          | —                                           | —       | 3 µs  | dBm   |

| Spurious          | Spur                                    | No parasitic oscillation with all<br>combinations of the following<br>parameters:<br>$V_{APC} = controlled^{(3)}$<br>$P_{IN} = 10.0 \text{ dBm}$<br>$V_{CC} = 2.8 \text{ V to 4.6 V}$<br>Load VSWR = 6:1, all phase angles | _                                           | _       | -36   | dBm   |

| Load mismatch     | Load                                    | All combinations of the following<br>parameters:<br>$V_{APC} = controlled^{(3)}$<br>$P_{IN} = 10 dBm$<br>$V_{CC} = 2.8 V to 4.6 V$<br>Load VSWR = 10:1, all phase<br>angles                                                | No module damage or permanen<br>degradation |         | anent |       |

| Noise power       | PNOISE                                  | At $f_0$ + 20 MHz<br>T = +25 °C<br>RBW = 100 kHz<br>Vcc = 3.2 V<br>Pout = 32 dBm                                                                                                                                           | _                                           | _       | -77   | dBm   |

|                   |                                         | At 869 to 894 MHz<br>RBW = 100 kHz<br>Vcc = 3.2 V<br>Pout = 32 dBm                                                                                                                                                         | —                                           | —       | -84   | dBm   |

#### NOTE(S):

<sup>(1)</sup> Unless specified otherwise:  $T_{CASE} = -20$  to max. operating temperature (see Table 2), RL = 50 $\Omega$ , pulsed operation with pulse width  $\leq 2308 \ \mu s$  and duty cycle  $\leq 4:8$ , Vcc = 2.8 V to 4.6 V.

<sup>(2)</sup> Icc = 0A to xA, where x = current at Pout = 34.0 dBm, 50  $\Omega$  load, and Vcc = 3.2 V.

(3) Icc = 0A to xA, where x = current at Pout = 32.0 dBm, 50  $\Omega$  load, and Vcc = 3.2 V.

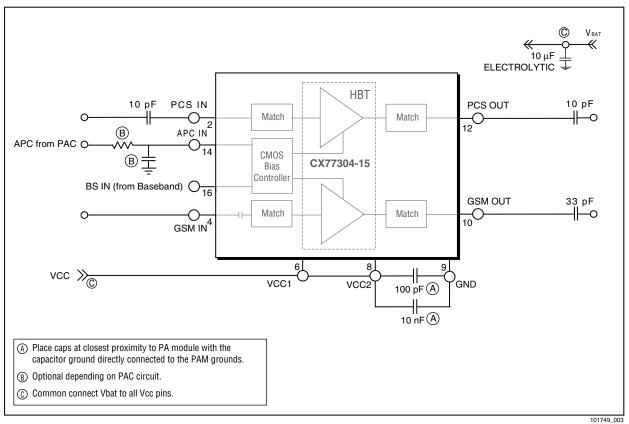

# **Package Dimensions and Pin Descriptions**

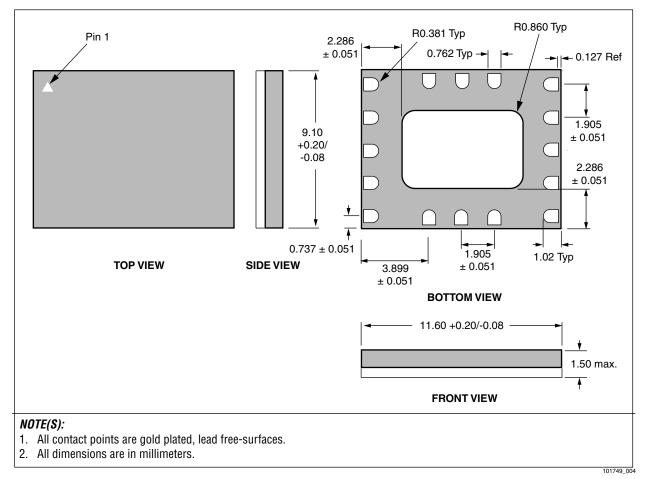

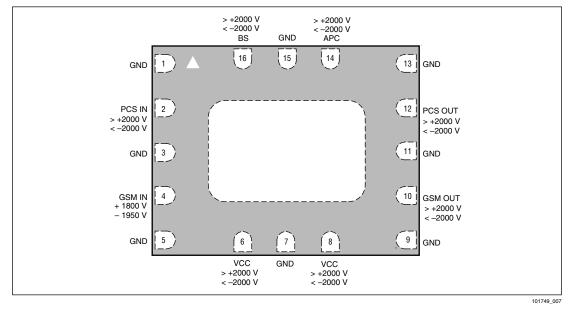

Figure 2 is a mechanical diagram of the pad layout for the 16-pin leadless CX77304-15 dual-band PA module. Figure 3 provides a recommended phone board layout footprint for the PAM to help the designer attain optimum thermal conductivity, good grounding, and minimum RF discontinuity for the 50 ohm terminals.

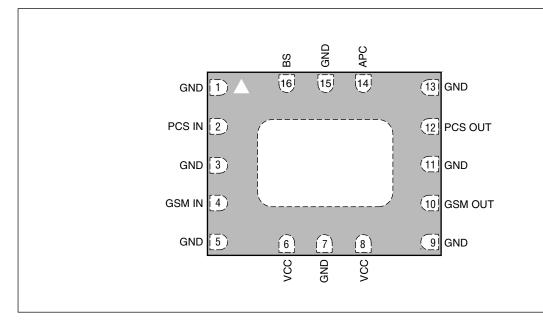

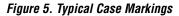

Figure 4 shows the pin configuration and pin numbering convention, which starts with pin 1 in the upper left, as indicated, and increments counter-clockwise around the package. Table 4 lists the pin names and descriptions. Figure 5 interprets typical case markings.

Figure 2. CX77304-15 Package Dimensions-16-pin Module (All Views)

Figure 3. Phone Board Layout Footprint for 9.1 mm x 11.6 mm Package

Figure 4. CX77304-15 Pin Configuration—16-Pin Leadless Module (Top View)

#### Table 4. CX77304-15 Signal Description

| Pin | Name    | Description                       |

|-----|---------|-----------------------------------|

| 1   | GND     | Ground                            |

| 2   | PCS IN  | RF input to PCS PA (DC coupled)   |

| 3   | GND     | Ground                            |

| 4   | GSM IN  | RF input to GSM PA                |

| 5   | GND     | Ground                            |

| 6   | Vcc     | Power supply for PA driver stages |

| 7   | GND     | Ground                            |

| 8   | Vcc     | Power supply for PA output stages |

| 9   | GND     | Ground                            |

| 10  | GSM OUT | GSM RF output (DC coupled)        |

| 11  | GND     | Ground                            |

| 12  | PCS OUT | PCS RF output (DC coupled)        |

| 13  | GND     | Ground                            |

| 14  | APC     | Analog Power Control              |

| 15  | GND     | Ground                            |

| 16  | BS      | Band Select                       |

101749\_008

# Package and Handling Information

Because of its sensitivity to moisture absorption, this device package is baked and vacuum packed prior to shipment. Instructions on the shipping container label must be followed regarding exposure to moisture after the container seal is broken, otherwise, problems related to moisture absorption may occur when the part is subjected to high temperature during solder assembly.

The SKY77304-15 is capable of withstanding an MSL 3/240 °C solder reflow. Care must be taken when attaching this product, whether it is done manually or in a production solder reflow environment. If the part is attached in a reflow oven, the temperature ramp rate should not exceed 5 °C per second; maximum temperature should not exceed 240 °C. If the part is manually attached, precaution should be taken to insure that the part is not subjected to temperatures exceeding 240 °C for more than 10 seconds. For details on attachment techniques, precautions, and handling procedures recommended by Skyworks, please refer to *Application Note: PCB Design and SMT Assembly/Rework, Document Number 101752*. Additional information on standard SMT reflow profiles can also be found in the *JEDEC Standard J-STD-020B*.

Production quantities of this product are shipped in the standard tape-and-reel format. For packaging details, refer to *Application Note: Tape and Reel, Document Number 101568*.

# **Electrostatic Discharge Sensitivity**

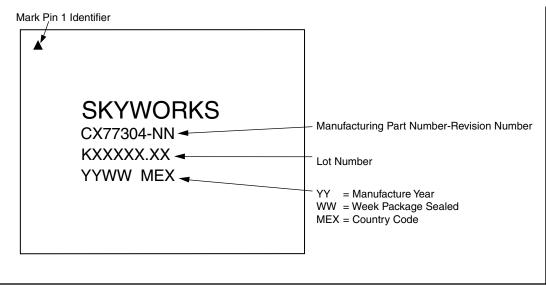

The CX77304-15 is a Class I device. Figure 6 lists the Electrostatic Discharge (ESD) immunity level for each pin of the CX77304-15 product. The numbers in Figure 6 specify the ESD threshold levels for each pin where the I-V curve between the pin and ground starts to show degradation. The ESD testing was performed in compliance with MIL-STD-883E Method 3015.7 using the Human Body Model. If ESD damage threshold magnitude is found to consistently exceed 2000 volts on a given pin, this so is indicated. If ESD damage threshold below 2000 volts is measured for either polarity, numbers are indicated that represent worst case values observed in product characterization.

Various failure criteria can be utilized when performing ESD testing. Many vendors employ relaxed ESD failure standards which fail devices only after "the pin fails the electrical specification limits" or "the pin becomes completely non-functional". Skyworks employs most stringent criteria, fails devices as soon as the pin begins to show any degradation on a curve tracer.

To avoid ESD damage, both latent and visible, it is very important that the product assembly and test areas follow the Class-1 ESD handling precautions listed in Table 5.

Table 5. Precautions for Handling GaAs IC-based Products to Avoid Induced Damage

| Personnel Grounding                                               | <u>Facility</u>                                     |

|-------------------------------------------------------------------|-----------------------------------------------------|

| Wrist Straps                                                      | Relative Humidity Control and Air Ionizers          |

| Conductive Smocks, Gloves and Finger Cots<br>Antistatic ID Badges | Dissipative Floors (less than $10^9 \Omega$ to GND) |

| Protective Workstation                                            | Protective Packaging & Transportation               |

| Dissipative Table Tops                                            | Bags and Pouches (Faraday Shield)                   |

| Protective Test Equipment (Properly Grounded)                     | Protective Tote Boxes (Conductive Static Shielding) |

| Grounded Tip Soldering Irons                                      | Protective Trays                                    |

| Conductive Solder Suckers                                         | Grounded Carts                                      |

| Static Sensors                                                    | Protective Work Order Holders                       |

# **Technical Information**

### **CMOS Bias Controller Characteristics**

The CMOS die within the PAM performs several functions that are important to the overall module performance. Some of these functions must be considered for development of the power ramping features in a 3GPP compliant transmitter power control loop<sup>1</sup>. Power ramping considerations will be discussed later in this section.

The four main functions that will be described in this section are Standby Mode Control, Band Select, Voltage Clamp, and Current Buffer. The functional block diagram is shown in Figure 7.

Figure 7. Functional Block Diagram

Please refer to 3GPP TS 05.05, Digital Cellular Communications System (Phase 2+); Radio Transmission and Reception. All GSM specifications are now the responsibility of 3GPP. The standards are available at http://www.3GPP.org/specs/specs.htm

#### **Standby Mode Control**

The Combinational Logic cell includes enable circuitry that monitors the APC ramping voltage from the power amplifier controller (PAC) circuit in the GSM transmitter. Typical handset designs directly connect the PA V<sub>cc</sub> to the battery at all times, and for some PA manufacturers this requires a control signal to set the device in or out of standby mode. The Skyworks PAM does not require a Transmit Enable input because it contains a standby detection circuit that senses the V<sub>APC</sub> to enable or disable the PA. This feature helps minimize battery discharge when the PA is in standby mode. When V<sub>APC</sub> is below the enable threshold voltage, the PA goes into a standby mode, which reduces battery current (I<sub>CC</sub>) to 6  $\mu$ A, typical, under nominal conditions.

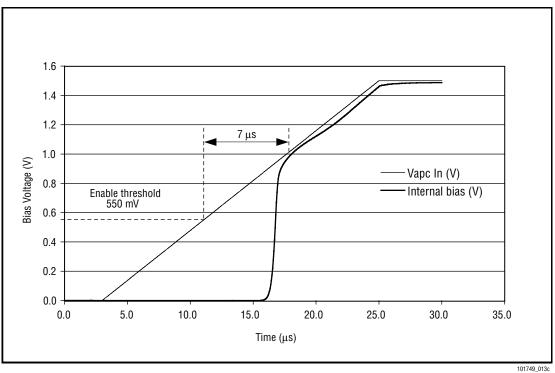

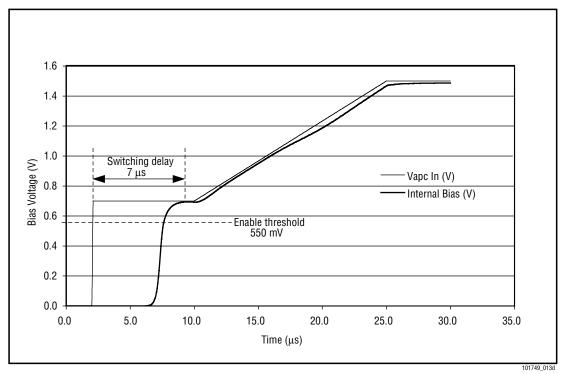

For voltages less than 700 mV at the APC input (pin 14), the PA bias is held at ground. As the APC input exceeds the enable threshold, the bias will activate. After an 8 µs delay, the amplifier internal bias will ramp quickly to match the ramp voltage applied to the APC input. In order for the internal bias to precisely follow the APC ramping voltage, it is critical that a ramp pedestal is set to the APC input at or above the enable threshold level with a timing at least 8 µs prior to ramp-up. This will be discussed in more detail in the following section, "Power Ramping Considerations for 3GPP Compliance".

#### Band Select

The Combinational Logic cell also includes a simple gate arrangement that selects the desired operational band by activating the appropriate current buffer. The voltage threshold level at the Band Select input (pin 16) will determine the active path of the bias output to the GaAs die.

#### Voltage Clamp

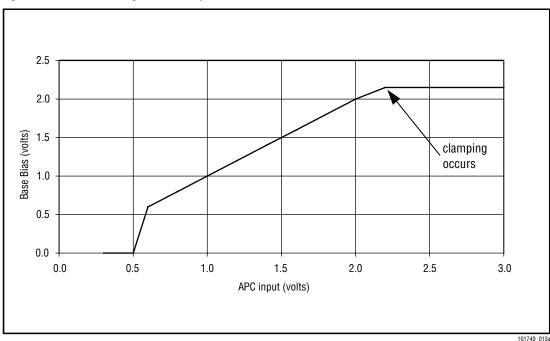

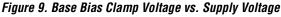

The Voltage Clamp circuit will limit the maximum bias voltage output applied to the bases of the HBT devices on the GaAs die. This provides protection against electrical overstress (EOS) of the active devices during high voltage and/or load mismatch conditions. Figure 8 shows the typical transfer function of the APC input to buffer output under resistively loaded conditions. Notice the enable function near 600 mV, and the clamp acting at 2.15 V, corresponding to a supply voltage of 4.0 V.

Figure 8. Base Bias Voltage vs. APC Input, Vcc = 4.0 V

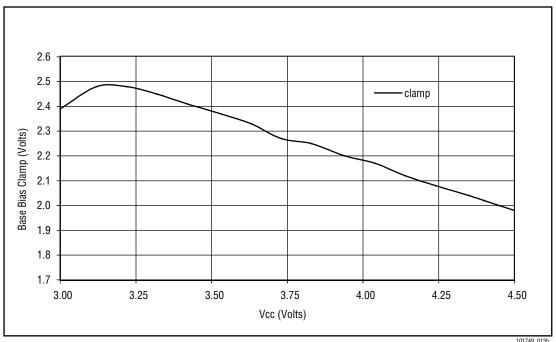

Due to output impedance effects, the bias of the GaAs devices increases as the supply voltage increases. The Voltage Clamp is designed to gradually decrease in level as the battery voltage increases. The performance of the clamp circuit is enhanced by the band gap reference that provides a supply-, process-, and temperature-independent reference voltage. The transfer function relative to V<sub>BAT</sub> is shown in Figure 9. For battery voltages below 3.4 V, the base bias voltage is limited by the common mode range of the buffer amplifier. For battery voltages above 3.4 V, the clamp limits the base bias.

#### **Current Buffer**

The output buffer amplifier performs a vital function in the CMOS device by transferring the APC input voltage ramp to the base of the GaAs power devices. This allows the APC input to be a high impedance port, sinking only 10  $\mu$ A, typical, assuring no loading effects on the PAC circuit. The buffers are designed to source the high GaAs base currents required, while allowing a settling time of less than 8  $\mu$ s for a 1.5 V ramp.

### **Power Ramping Considerations for 3GPP Compliance**

These are the primary variables in the power control loop that the system designer must control:

- software control of the DSP / DAC

- software control of the transmitter timing signals

- ramp profile attributes pedestal, number of steps, duration of steps

- layout of circuit / parasitics

- RC time constants within the PAC circuit design

All of these variables will directly influence the ability of a GSM transmitter power control loop to comply with 3GPP specifications.

Although there is a specific time mask template in which the transmitter power is allowed to ramp up, the method is very critical. The 3GPP system specification for switching transients results in a requirement to limit the edge rate of output power transitions of the mobile. Switching transients are caused by the transition from minimum output power to the desired output power, and vice versa. The spectrum generated by this transition is due to the ramping waveform amplitude modulation imposed on the carrier. Sharper transitions tend to produce more spectral "splatter" than smooth transitions. If the transmit output power is ramped up too slowly, the radio will violate the time mask specification. In this condition, the radio may not successfully initiate or maintain a phone call. If the transmit output power is ramped up too quickly, this will cause RF "splatter" at certain frequency offsets from the carrier as dictated by the 3GPP specification. This splatter, known as Output RF Spectrum (ORFS) due to Switching Transients, will increase the system noise level, which may knock out other users on the system. The main difficulty with TDMA power control is allowing the transmitter to ramp the output power up and down gradually so switching transients are not compromised while meeting the time mask template at all output power levels in all operational bands. The transmitter has 28 µs to ramp up power from an off state to the desired power level.

The GSM transmitter power control loop generally involves feedback around the GaAs PA, which limits the bandwidth of signals that can be applied to the PA bias input. Since the PA is within the feedback loop, its own small-signal frequency response must exhibit a bandwidth 5 to 10 times that of the power control loop. As discussed in the previous section, the PA bias is held at ground for inputs less than 700mV. As the APC input exceeds the enable threshold, the bias will activate. After an 8  $\mu$ s delay, the amplifier internal bias will quickly ramp to match the ramp voltage applied to the V<sub>APC</sub> input. Since the bias must be wide band relative to the power control loop, the ramp will exhibit a fast edge rate. If the APC input increases beyond 1V before the 8  $\mu$ s switching delay is allowed to occur after the bias. During this ramp, the internal power control is running "open loop" and the edge rates are defined by the frequency response of the PA bias rather than that of the power control loop. This open loop condition will result in switching transients that are directly correlated to the PA bias bandwidth.

Application of an initial APC voltage, which enables the bias at least 8  $\mu$ s before the V<sub>APC</sub> voltage is ramped, will ensure that the internal bias of the PAM will directly follow the applied V<sub>APC</sub>. As a result, the power control loop will define all edge transitions rather than the PA internal bandwidth defining the transition. Figures 10 and 11 show the relationship of the internal bias relative to the applied APC in two cases. One case has ramping starting from ground; the other case has ramping starting with an initial enable pedestal of 700 mV. It is evident that the pedestal level is critical to ensure a predictable and well behaved power control loop.

To enable the CMOS driver in the PAM prior to ramp-up, a PAC output pedestal level to the APC input of the PAM (pin 14) should be set to about 700 mV. This pedestal level should have a duration of at least 8  $\mu$ s directly prior to the start of ramp up.

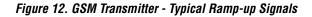

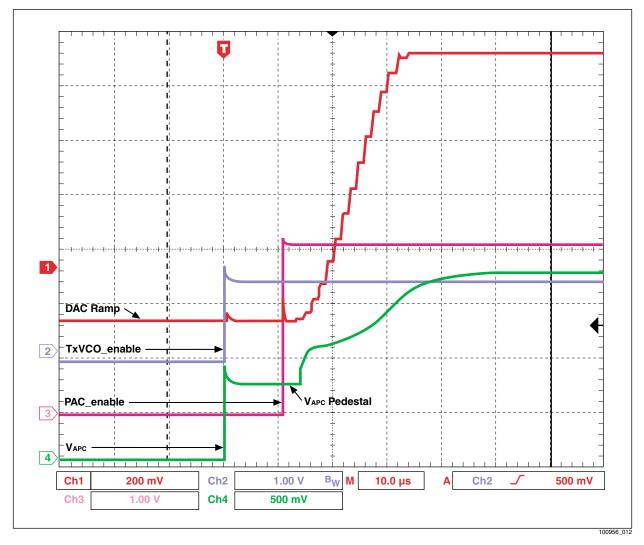

Figure 12 shows typical signals and timings measured in a GSM transmitter power control loop. This particular example is at GSM Power Level 5, Channel 62. The oscilloscope traces are TxVCO\_enable, PAC\_enable, DAC Ramp, and V<sub>APC</sub> (pin 14).

**NOTE:** When the TxVCO is enabled, the pedestal becomes set at the APC input of the PAM, then the PAC is enabled, and finally the DAC ramp begins.

The device specifications for enable threshold level and switching delay are shown in Table 3.

Figure 10. PAM Internal Bias Performance – No Pedestal Applied

Figure 11. PAM Internal Bias Performance – Pedestal Applied

# **Ordering Information**

| Model Number | Manufacturing<br>Part Number | Package             | Operating Temperature |

|--------------|------------------------------|---------------------|-----------------------|

| CX77304-15   | CX77304-15                   | 9.1 x 11.6 x 1.5 mm | –20 °C to +100 °C     |

# **Revision History**

| Revision | Level | Date               | Description     |

|----------|-------|--------------------|-----------------|

| А        |       | September 19, 2003 | Initial Release |

## References

Application Note: Tape and Reel, Document Number 101568 Application Note: PCB Design and SMT Assembly/Rework, Document Number 101752 JEDEC Standard J-STD-020B

© 2001–2003, Skyworks Solutions, Inc. All Rights Reserved.

Information in this document is provided in connection with Skyworks Solutions, Inc. ("Skyworks") products. These materials are provided by Skyworks as a service to its customers and may be used for informational purposes only. Skyworks assumes no responsibility for errors or omissions in these materials. Skyworks may make changes to its products, specifications and product descriptions at any time, without notice. Skyworks makes no commitment to update the information and shall have no responsibility whatsoever for conflicts, incompatibilities, or other difficulties arising from future changes to its products and product descriptions.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as may be provided in Skyworks' Terms and Conditions of Sale for such products, Skyworks assumes no liability whatsoever.

THESE MATERIALS ARE PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, RELATING TO SALE AND/OR USE OF SKYWORKS™ PRODUCTS INCLUDING WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, PERFORMANCE, QUALITY OR NON-INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. SKYWORKS FURTHER DOES NOT WARRANT THE ACCURACY OR COMPLETENESS OF THE INFORMATION, TEXT, GRAPHICS OR OTHER ITEMS CONTAINED WITHIN THESE MATERIALS. SKYWORKS SHALL NOT BE LIABLE FOR ANY SPECIAL, INDIRECT, INCIDENTAL, OR CONSEQUENTIAL DAMAGES, INCLUDING WITHOUT LIMITATION, LOST REVENUES OR LOST PROFITS THAT MAY RESULT FROM THE USE OF THESE MATERIALS.

Skyworks<sup>™</sup> products are not intended for use in medical, lifesaving or life-sustaining applications. Skyworks' customers using or selling Skyworks<sup>™</sup> products for use in such applications do so at their own risk and agree to fully indemnify Skyworks for any damages resulting from such improper use or sale.

The following are trademarks of Skyworks Solutions, Inc.: Skyworks<sup>™</sup>, the Skyworks symbol, and "Breakthrough Simplicity"<sup>™</sup>. Product names or services listed in this publication are for identification purposes only, and may be trademarks of third parties. Thirdparty brands and names are the property of their respective owners.

Additional information, posted at www.skyworksinc.com, is incorporated by reference.

General Information: Skyworks Solutions, Inc. 20 Sylvan Rd. Woburn, MA. 01801

www.skyworksinc.com