### AMD Athlon™ VID/FID INTERFACE

### **Features**

- 5-bit voltage identification (VID) interface logic for Athlon™ processor VDD CORE circuitry

- Selectable 'Sleep' and 'On' VID code inputs

- 4-bit frequency identification (FID) interface logic with level shifter (2.5V to 3.3V)

- North Bridge-compatible open-drain FID outputs

- Built-in 2.5V/50mA voltage regulator with enable

- Voltage regulator designed specifically for power-conscious battery-powered devices

## **Applications**

- AMD Athlon™ processor-based products

- Motherboards

- Notebook computers

## **Product Description**

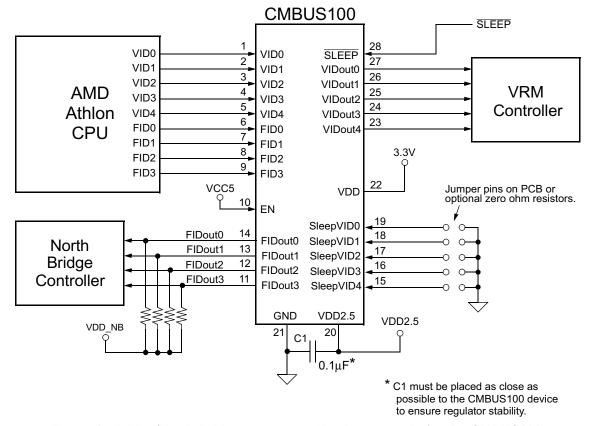

The CMBUS100 VID/FID Interface is designed for use in microprocessor systems based on the AMD Athlon™ processors. The CMBUS100 provides the voltage identification (VID) interface logic required between an Athlon CPU and its associated VDD CORE voltage regulator, as well as the frequency identification (FID) interface logic necessary between the CPU and the North Bridge controller.

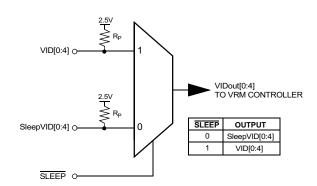

For the five VID code bit lines, the CMBUS100 provides a level-shifting function from the CPU's 2.5V output to the 3.3V that the VDD CORE voltage regulator requires. Furthermore, there is an onboard multiplexer which enables selecting between the full-speed VID code of the CPU and a user-selectable 'Sleep' or 'Soft' VID code (the desktop system processor requires a 'Sleep' VID code whereas the mobile system processor requires a 'Soft' VID input).

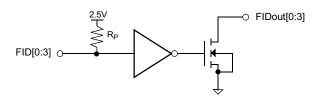

For the 4 FID code bit lines, the CMBUS100 provides a level shifting function from the CPU's 2.5V output to the open-drain outputs that the North Bridge requires.

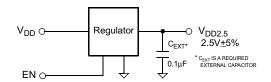

The CMBUS100 also features a 2.5V voltage regulator, which serves as the supply for the internal 2.5V pull-up resistors on the VID and FID inputs as well as providing a minimum of 50mA current for external loads. This is a series regulator which uses much less current than a shunt regulator, resulting in power savings and a longer battery life in notebook computers.

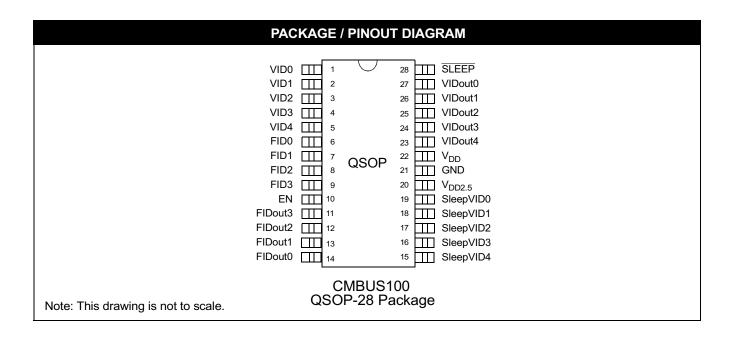

The CMBUS100 IC is available in a space-saving QSOP-28 package, and is fabricated with California Micro Devices' CMOS process.

### **Electrical Schematic**

Voltage Identification (VID) Logic

Frequency Identification (FID) Logic

Voltage Regulator Circuit

| PIN DESCRIPTIONS |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PIN(s)           | NAME                    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 1-5              | VID0-VID4               | Bits 0 through 4 of the VCC_CORE ID input from processor, respectively. Each input has an internal 27K $\Omega$ pull-up resistor to 2.5V.                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 6-9              | FID0-FID3               | Bits 0 through 3 of the VID input from processor, respectively. Each input has an intern $27K\Omega$ pull-up resistor to 2.5V.                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| 10               | EN                      | Regulator enable pin. This is an active high, 5.5V tolerant input which can be connected directly to $V_{CC5}$ (5V), thus shutting down the regulator when $V_{CC5}$ is turned off.                                                                                                                                                                                                                                                                                  |  |  |  |

| 11-14            | FIDout3–FIDout0         | Bits 3 to 0 of the level-shifted FID output, respectively. These are open-drain outputs and are 5.5V tolerant.                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| 15-19            | SleepVID4-<br>SleepVID0 | Bits 4 through 0 of the SleepVID or SoftVID input, respectively. Each input has an internal 27K $\Omega$ pull-up resistor to 2.5V.                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 20               | $V_{\mathrm{DD2.5}}$    | 2.5V output from the voltage regulator. Can be used to power external pull-up resistors. This pin requires a $0.1\mu F$ decoupling capacitor to be connected as close as possible to it (see Note1).                                                                                                                                                                                                                                                                 |  |  |  |

| 21               | GND                     | Device ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| 22               | V <sub>DD</sub>         | 3.3V supply input.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 23-27            | VIDout4–VIDout0         | Bits 4 to 0 of the level-shifted VID output, respectively. These are 3.3V CMOS logic outputs.                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 28               | SLEEP                   | 3.3V logic input to select between VID(0:4) inputs and SleepVID(0:4) inputs. When SLEEP is asserted low, the SleepVID(0:4) inputs are selected. When SLEEP is asserted high, the VID(0:4) inputs are selected. For systems based on the Athlon desktop processor, it is intended that this input be driven by the Power Management S1 state logic. For systems based on the mobile processor, it is intended that this input will be driven by the Power Good logic. |  |  |  |

Note 1: It is essential that a  $0.1\mu F$  decoupling capacitor be placed between  $V_{DD2.5}$  and GND as close as possible to these pins. This capacitor is required to ensure the stability of the 2.5V regulator.

© 2002 California Micro Devices Corp. All rights reserved.

## **Ordering Information**

| PART NUMBERING INFORMATION |         |                                   |              |  |  |

|----------------------------|---------|-----------------------------------|--------------|--|--|

| Pins                       | Package | Ordering Part Number <sup>1</sup> | Part Marking |  |  |

| 28                         | QSOP-28 | CMBUS100Q                         | CMBUS100Q    |  |  |

Note 1: Parts are shipped in Tape & Reel form unless otherwise specified.

# **Specifications**

| ABSOLUTE MAXIMUM RATINGS                                    |             |       |  |  |

|-------------------------------------------------------------|-------------|-------|--|--|

| PARAMETER                                                   | RATING      | UNITS |  |  |

| Supply Voltage, V <sub>DD</sub>                             | 5.5         | V     |  |  |

| Regulator Current                                           | 150         | mA    |  |  |

| Load current at open-drain FID outputs and CMOS VID outputs | 6           | mA    |  |  |

| Storage Temperature Range                                   | -65 to +150 | °C    |  |  |

| DC Package Power Rating                                     | 1000        | mW    |  |  |

| STANDARD OPERATING CONDITIONS   |                            |       |  |  |

|---------------------------------|----------------------------|-------|--|--|

| PARAMETER                       | RATING                     | UNITS |  |  |

| Supply Voltage, V <sub>DD</sub> | $3.15 \le V_{DD} \le 3.45$ | V     |  |  |

| Operating Temperature Range     | 0 to +70                   | °C    |  |  |

| ELECTRICAL OPERATING CHARACTERISTICS <sup>1</sup> |                                                                      |                                                                                              |                      |      |                      |             |

|---------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------|----------------------|------|----------------------|-------------|

| SYMBOL                                            | PARAMETER                                                            | CONDITIONS                                                                                   | MIN                  | TYP  | MAX                  | UNITS       |

| V <sub>IH</sub>                                   | Logic "1" input voltage EN VID(0:4), SleepVID(0:4), FID(0:3) SLEEP   | V <sub>DD</sub> =3.3V                                                                        | 1.75<br>1.75<br>1.75 |      | 5.5<br>2.9<br>3.7    | V<br>V<br>V |

| V <sub>IL</sub>                                   | Logic "0" input voltage EN VID(0:4), SleepVID(0:4), FID(0:3) SLEEP   | V <sub>DD</sub> =3.3V                                                                        | -0.4<br>-0.4<br>-0.4 |      | 0.75<br>0.75<br>0.75 | V<br>V<br>V |

| V <sub>FIDout</sub>                               | Open-drain output voltage<br>FIDout(0:3) outputs                     |                                                                                              | 0                    |      | 5.5                  | V           |

| I <sub>LOAD</sub>                                 | Load current FIDout(0:3) outputs VIDout(0:4) outputs                 |                                                                                              |                      |      | 6.0<br>6.0           | mA<br>mA    |

| I <sub>DD</sub>                                   | Supply Current                                                       | V <sub>DD</sub> =3.3V;<br>VID(0:4), SleepVID(0:4)<br>and FID(0:3) inputs all at<br>logic "1" |                      | 0.5  | 1.0                  | mA          |

| V <sub>VDD2.5</sub>                               | Regulator Output Voltage (at Pin 20)                                 | $3.15 \le V_{DD} \le 3.45;$<br>$I_L = 50 \text{mA}$                                          | 2.375                | 2.5  | 2.625                | V           |

| I <sub>VDD2.5</sub>                               | Regulator Output Current (at Pin 20)                                 | $3.15 \le V_{DD} \le 3.45$                                                                   | 50                   | 100  |                      | mA          |

| R <sub>ON</sub>                                   | "On" resistance of FID open-drain output (N-FET)                     |                                                                                              | 50                   | 100  | 200                  | Ω           |

| R <sub>P</sub>                                    | Pull-up resistance value                                             | V <sub>P</sub> = 2.5V                                                                        | 13.5                 | 27.0 | 40.5                 | kΩ          |

| V <sub>ESD</sub>                                  | ESD Withstand Voltage, Human Body<br>Model, MIL-STD-883, Method 3015 | Note 2,3                                                                                     | <u>+</u> 2           |      |                      | kV          |

Note 1:  $T_A = 0$  to +70°C.

Note 2: ESD applied to input and output pins with respect to GND, one at a time.

Note 3: These parameters are guaranteed by design and characterization.

## **Application Information**

The CMBUS100 provides an easy way to interface the FID and VID signals from the AMD Athlon CPU to the North Bridge controller and the VRM controller/regulator. It also requires the least amount of board space.

Internal pull-up resistors (27k $\Omega$  nom.) are present at all inputs to the CMBUS100. External pull-up resistors may be added in parallel if lower resistances are required.

For the sleepVID(0:4) inputs, which set the VID code for the sleep and reset states, we suggest using either terminal pins or optional zero ohm resistors to short the individual sleepVID(0:4) inputs to ground.

The VIDout(0:4) outputs are 3.3V CMOS outputs. These outputs do not require pull-up resistors.

The FIDout(0:3) outputs are open-drain outputs. These require pull-up resistors. Consult your North Bridge design documentation for the possible range of values. Note that the current must not exceed 6mA, so for a 3.3V North Bridge the pull-up resistors cannot be less than 550 $\Omega$ . We recommend using a much higher value, for example,  $10k\Omega$ , to minimize power consumption. The FIDout signals are tolerant of voltages up to 5.5V.

The 2.5V regulator is a series regulator, so the DC current consumption will be much less than a shunt type regulator, contributing to extended battery life in notebook computers. The regulated 2.5V output is used internally in the CMBUS100 for the Rp pull-up resistors, and is also available for external loads (50mA guaranteed, 100mA typical). A 0.1µF capacitor must be connected to the 2.5V output pin (pin 20) to ensure the stability of the regulator.

This regulator can be disabled by a logic LOW on the 'EN' pin (pin 10). Pin 10 is a 5.5V-tolerant input, so it can be connected to any signal which goes LOW during the system 'suspend to RAM' state. We suggest VCC5 because it is probably the easiest to route to.

Figure 1. Athlon/North Bridge system application example for the CMBUS100.

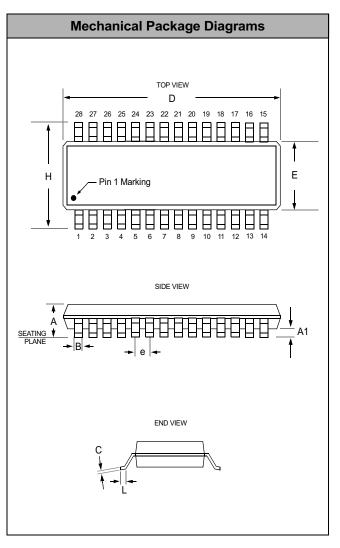

## **Mechanical Details**

#### **QSOP Mechanical Specifications:**

CMBUS100 devices are packaged in 28-pin QSOP packages. Dimensions are presented below.

For complete information on the QSOP-28 package, see the California Micro Devices QSOP Package Information document.

| PACKAGE DIMENSIONS             |                           |      |           |       |  |

|--------------------------------|---------------------------|------|-----------|-------|--|

| Package                        | QSOP (JEDEC name is SSOP) |      |           |       |  |

| Pins                           | 28                        |      |           |       |  |

| Dimensions                     | Millimeters               |      | Inches    |       |  |

| Difficusions                   | Min                       | Max  | Min       | Max   |  |

| Α                              | 1.35                      | 1.75 | 0.053     | 0.069 |  |

| A1                             | 0.10                      | 0.25 | 0.004     | 0.010 |  |

| В                              | 0.20                      | 0.30 | 0.008     | 0.012 |  |

| С                              | 0.18                      | 0.25 | 0.007     | 0.010 |  |

| D                              | 9.80                      | 9.98 | 0.386     | 0.393 |  |

| Е                              | 3.81                      | 3.98 | 0.150     | 0.157 |  |

| е                              | 0.64 BSC                  |      | 0.025 BSC |       |  |

| Н                              | 5.79                      | 6.20 | 0.228     | 0.244 |  |

| L                              | 0.40                      | 1.27 | 0.016     | 0.050 |  |

| # per tube                     | 50 pieces*                |      |           |       |  |

| # per tape<br>and reel         | 2500 pieces               |      |           |       |  |

| Controlling Dimensions: inches |                           |      |           |       |  |

<sup>\*</sup> This is an approximate amount which may vary.

Package Dimensions for QSOP-28