ISSUE 2

SONET/SDH 155Mbit/s ADM Reference Design

# PM5543 ADM155\_REF

# SONET/SDH 155 Mbit/s ADD/DROP MULTIPLEXOR WITH SINGLE MODE OPTICAL INTERFACE REFERENCE DESIGN (SARD)

Issue 2: July, 1996

SONET/SDH 155Mbit/s ADM Reference Design

# TABLE OF CONTENTS

| FEATURES 1                                                   |

|--------------------------------------------------------------|

| OVERVIEW                                                     |

| FUNCTIONAL DESCRIPTION 4                                     |

| PM5101 Motherboard Interface5                                |

| Optical Interface 5                                          |

| CY7B951 5                                                    |

| Reference Clock 6                                            |

| System Clock6                                                |

| STXC 6                                                       |

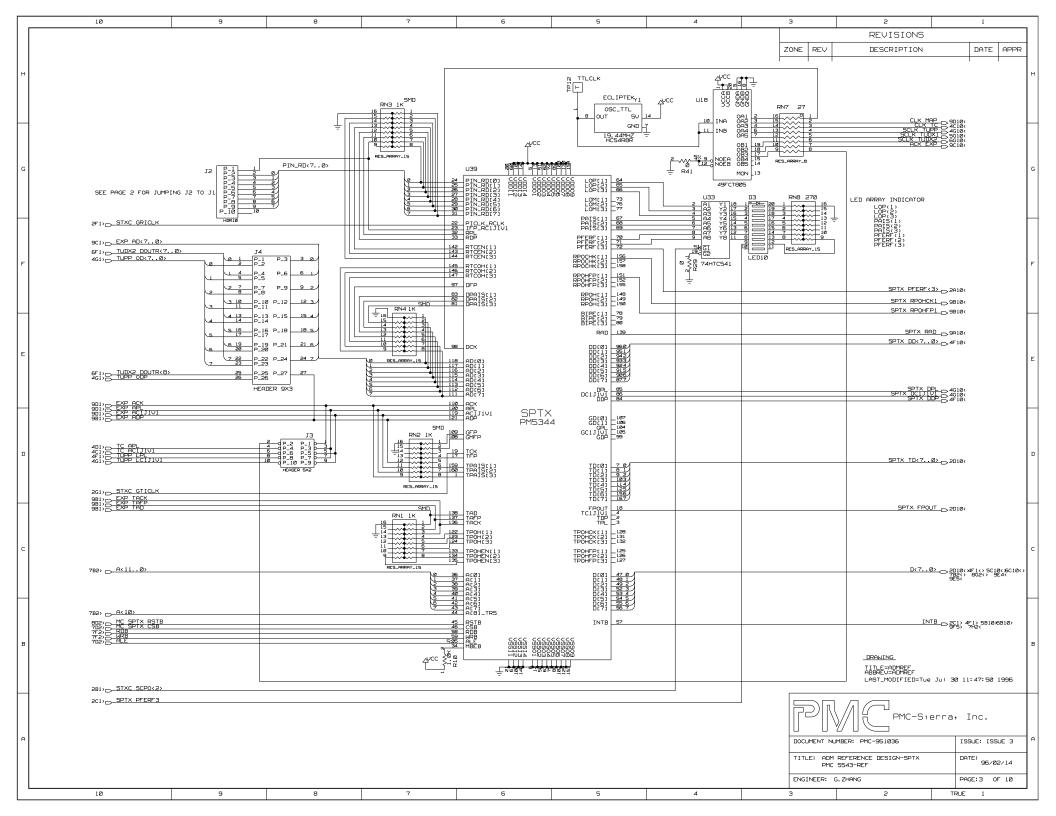

| SPTX7                                                        |

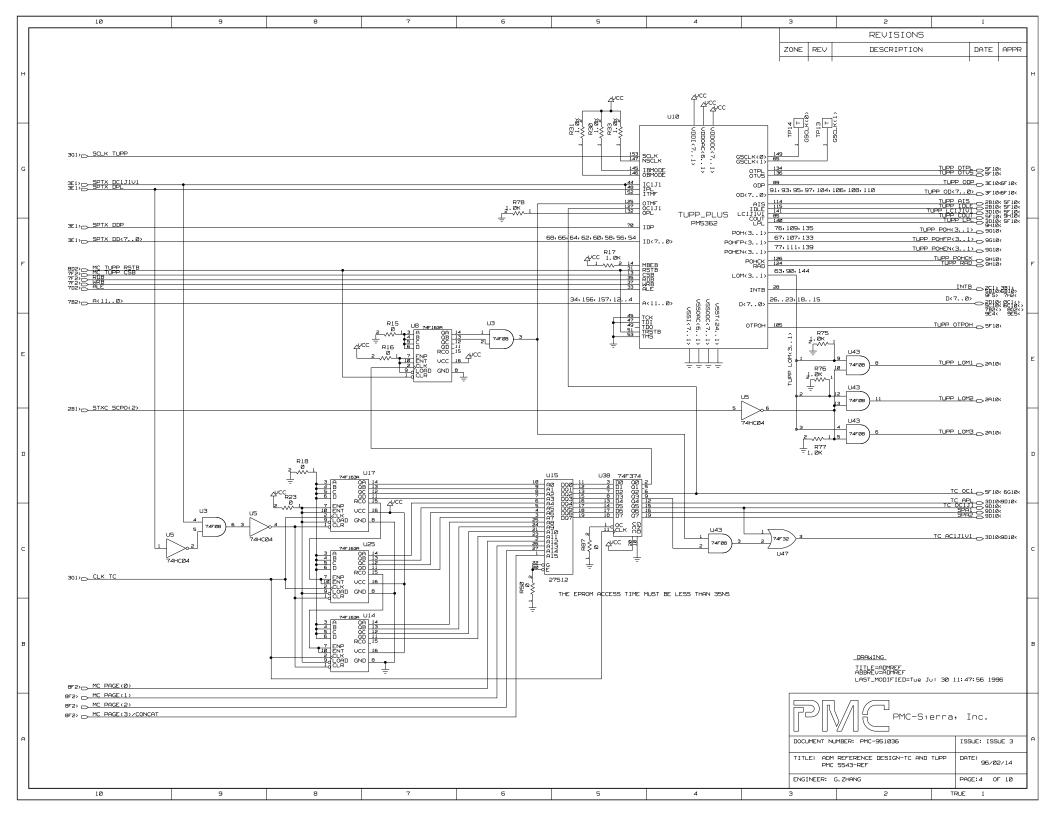

| TUPP & TUPP-Plus 8                                           |

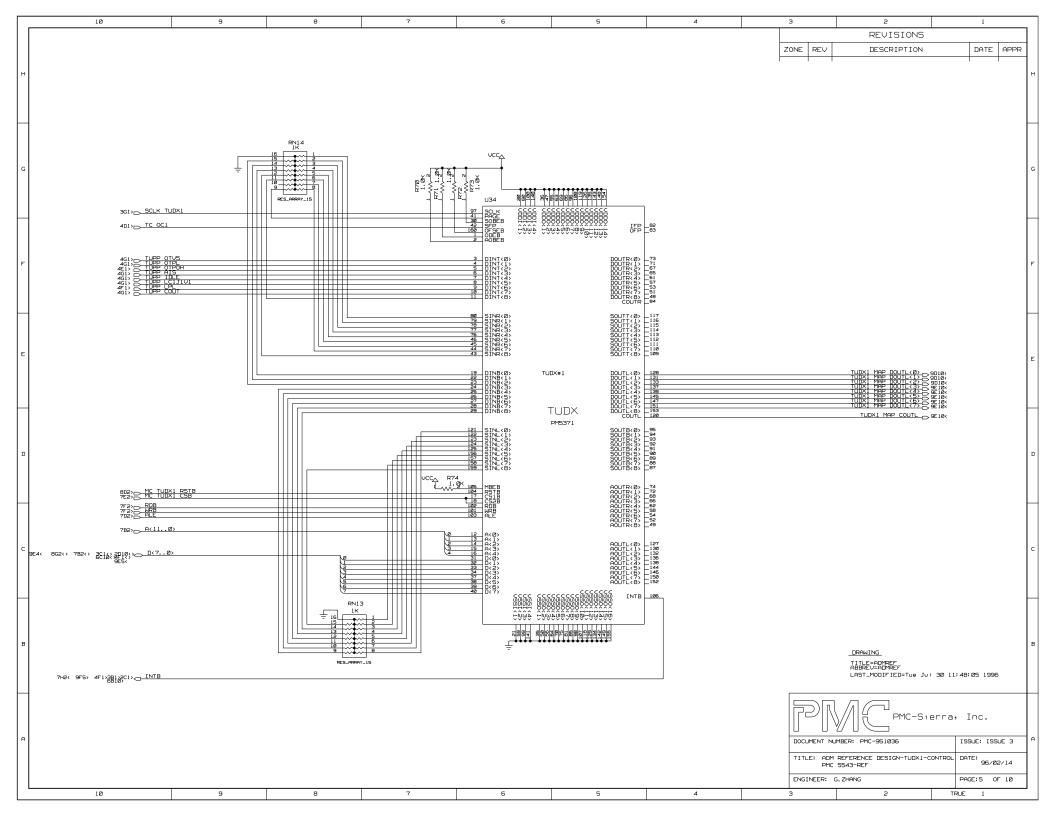

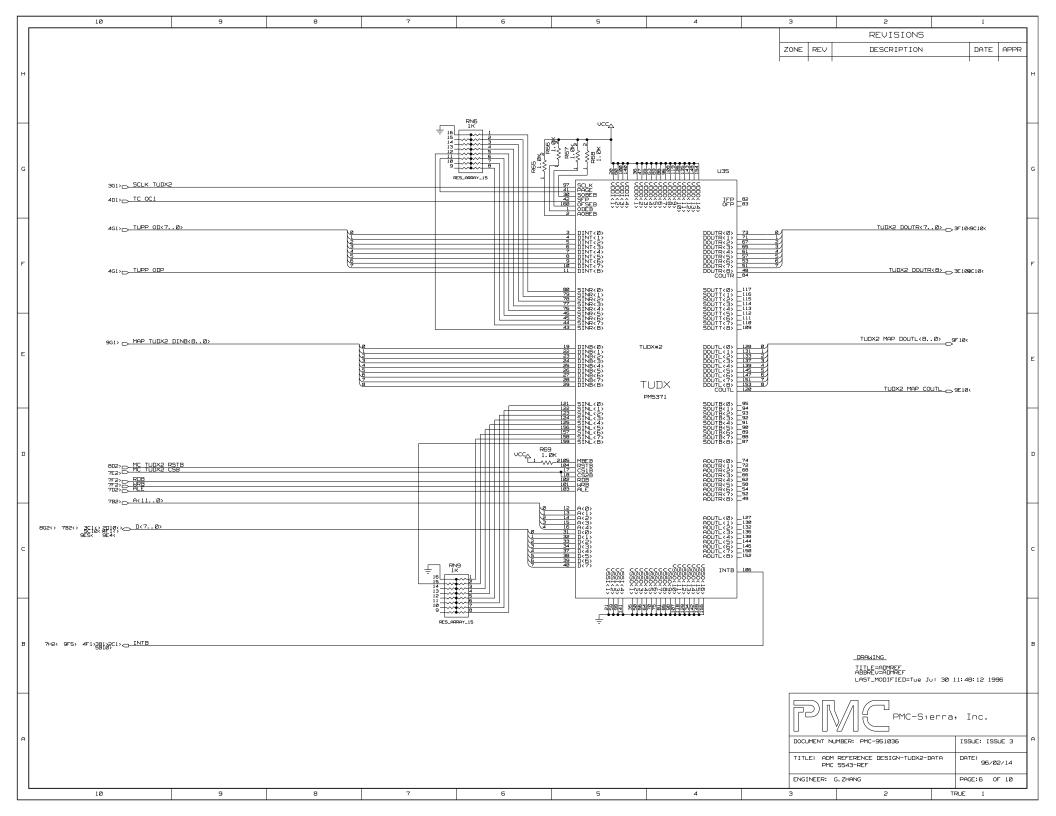

| TUDX                                                         |

| Timing Control11                                             |

| Ring Expansion Interface12                                   |

| Mapper Interface12                                           |

| LED Displays                                                 |

| Configuration Headers/Jumpers13                              |

| INTERFACE SIGNAL DESCRIPTION14                               |

| Microprocessor Interface (Connector P1)14                    |

| Microprocessor Interface Signal Description.                 |

| Decoded Microprocessor Signal to Stel/ar chipset Interface15 |

| Prototyping Jumper Interface17                               |

| SPTX ADD Bus Clock & Signal Select Interface                 |

| HP SDX1155 Optics to/from Cypress CY7B951 Interface19        |

| Cypress CY7B951 to/from STXC Interface20                     |

| STXC to/from SPTX Interface20                                |

| SPTX to/from TUPP/TUPP-Plus Interface21                      |

| SPTX to/from TIMING CONTROL(TC) block Interface21            |

| TUPP/TUPP-Plus to/from TUDX1 Interface21                     |

| TUPP/TUPP-Plus to/from TUDX2 Interface                       |

| TUPP from TIMING CONTROL(TC) Interface                       |

#### SONET/SDH 155Mbit/s ADM Reference Design

|      | TUDX1 from TIMING CONTROL(TC) Interface      |    |

|------|----------------------------------------------|----|

|      | TUDX2 from TIMING CONTROL(TC) Interface      |    |

|      | 19.44MHz System Clock Distribution Interface |    |

|      | TIMING CONTROL(TC) Interface                 |    |

|      | Ring Expansion Interface                     |    |

|      | Mapper Interface                             |    |

|      | STXC and TUPP-Plus Status LED Display        |    |

|      | SPTX status LED Display                      |    |

| SOF  | TWARE INTERFACE DESCRIPTION                  |    |

|      | SARD General Registers                       |    |

|      | STXC Registers                               |    |

|      | SPTX Registers                               |    |

|      | TUPP & TUPP-Plus Registers                   |    |

|      | TUDX1 Registers<br>TUDX2 Registers           |    |

|      |                                              |    |

| On E | Board PROM                                   | 40 |

| D.C. | CHARACTERISTICS                              | 53 |

| REF  | ERENCES                                      | 54 |

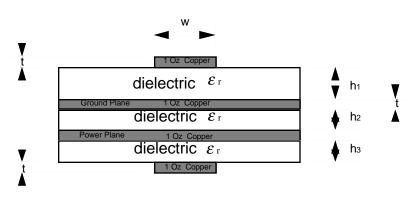

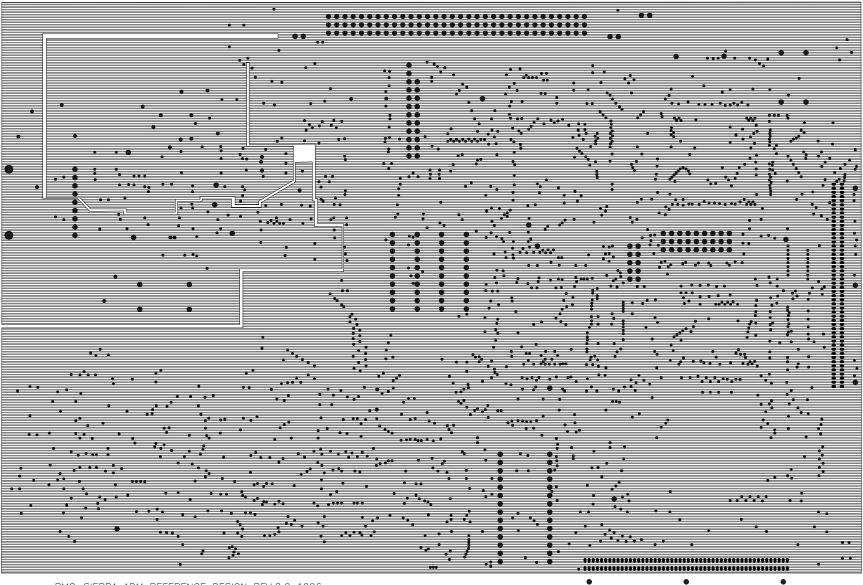

| APP  | ENDIX 1: SPECIAL LAYOUT CONSIDERATIONS       | 55 |

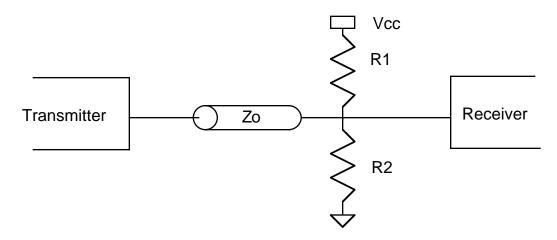

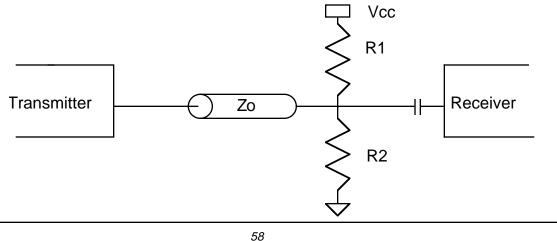

|      | High Speed Signal Termination                | 55 |

|      | Trace Impedance Control                      | 55 |

|      | Routing                                      |    |

|      | Termination                                  |    |

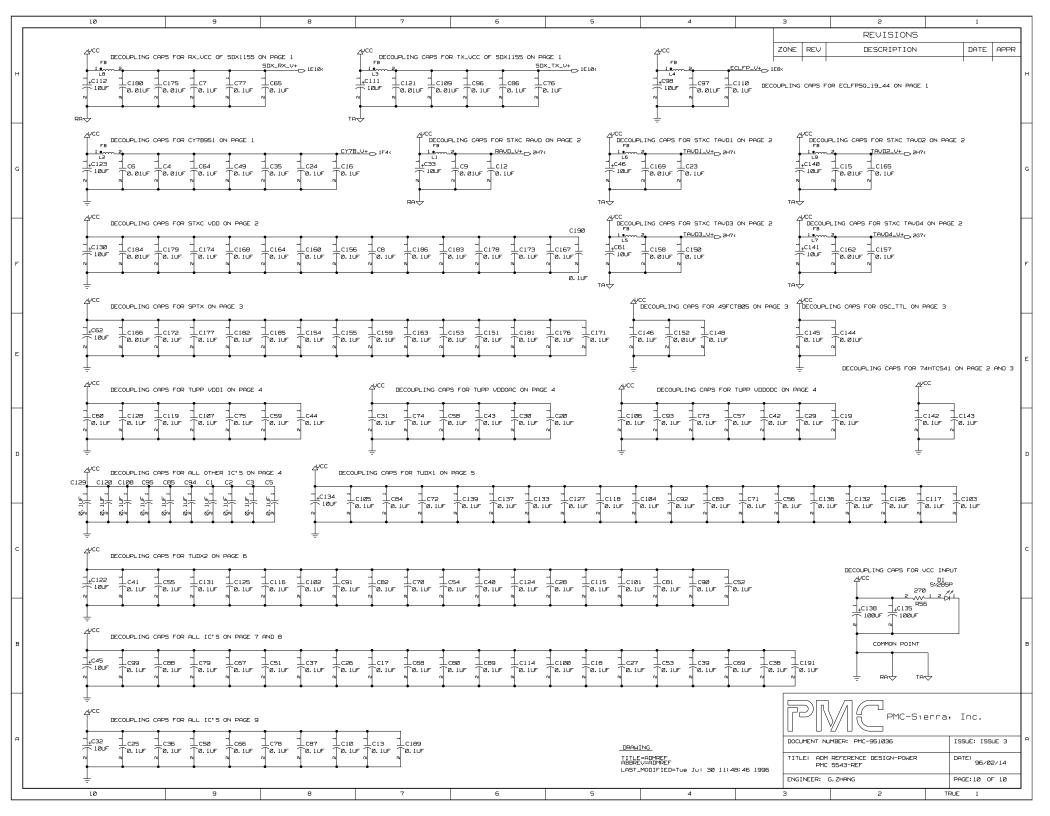

|      | Power and Ground Plane Noise Decoupling      | 59 |

| APP  | ENDIX 2: BILL OF MATERIAL                    | 61 |

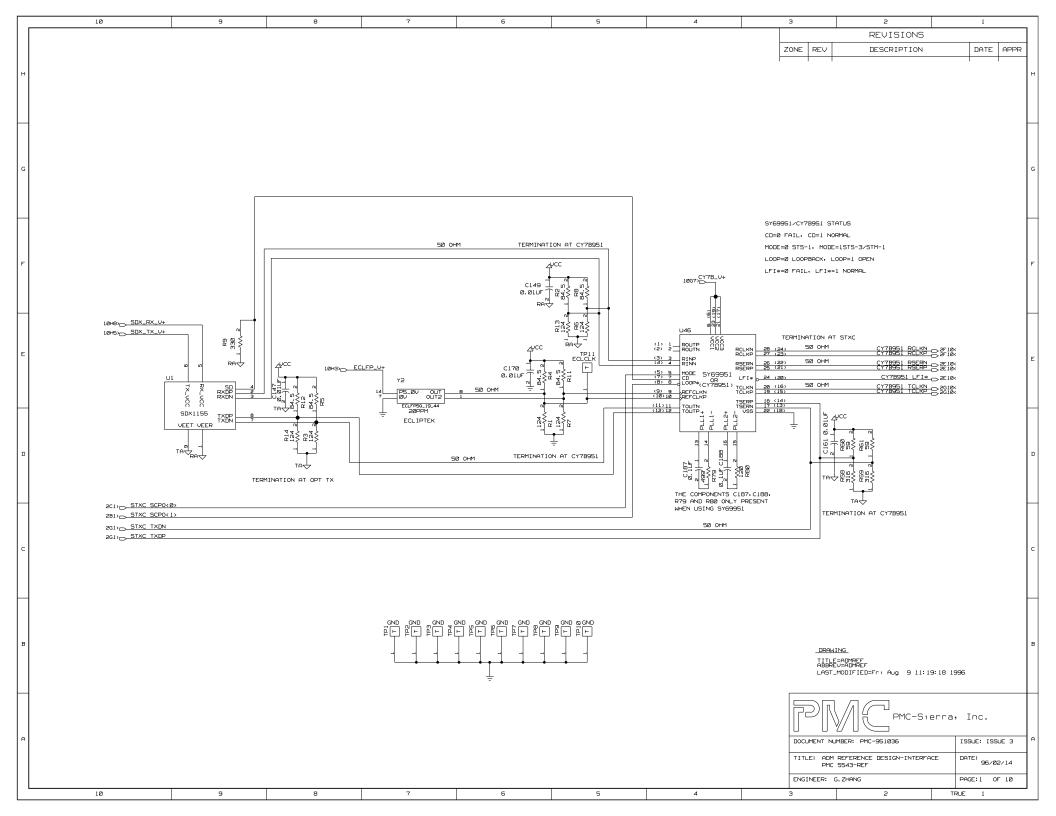

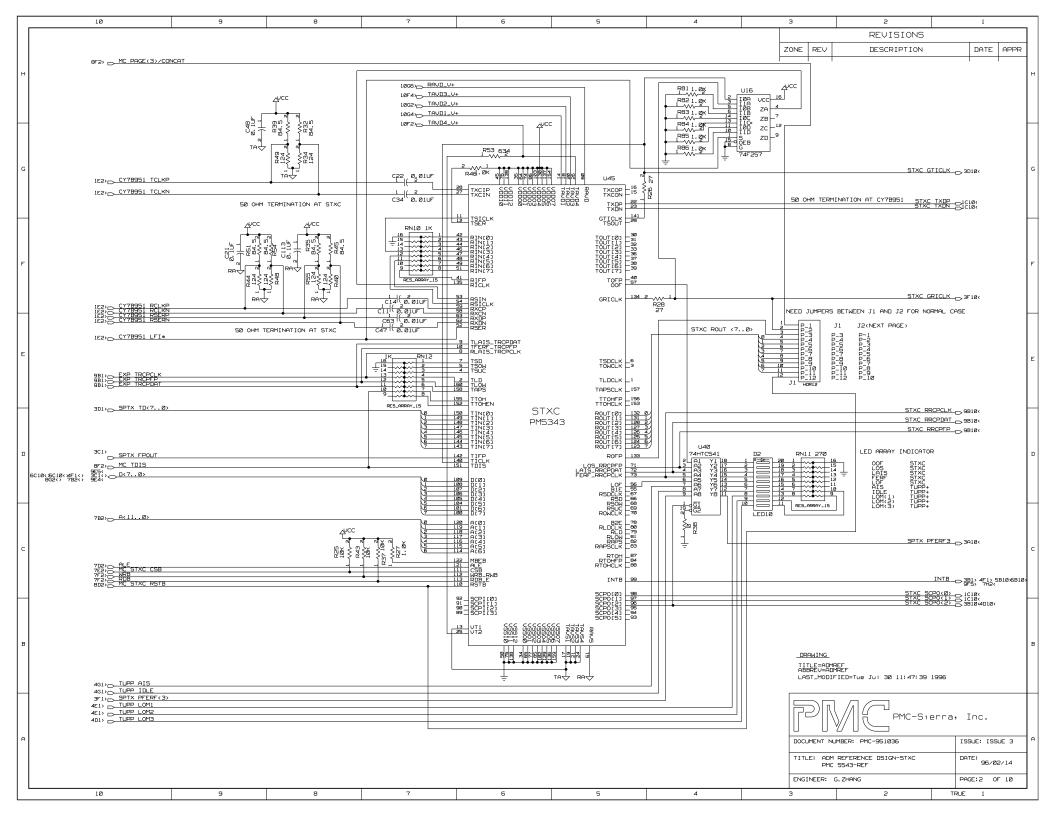

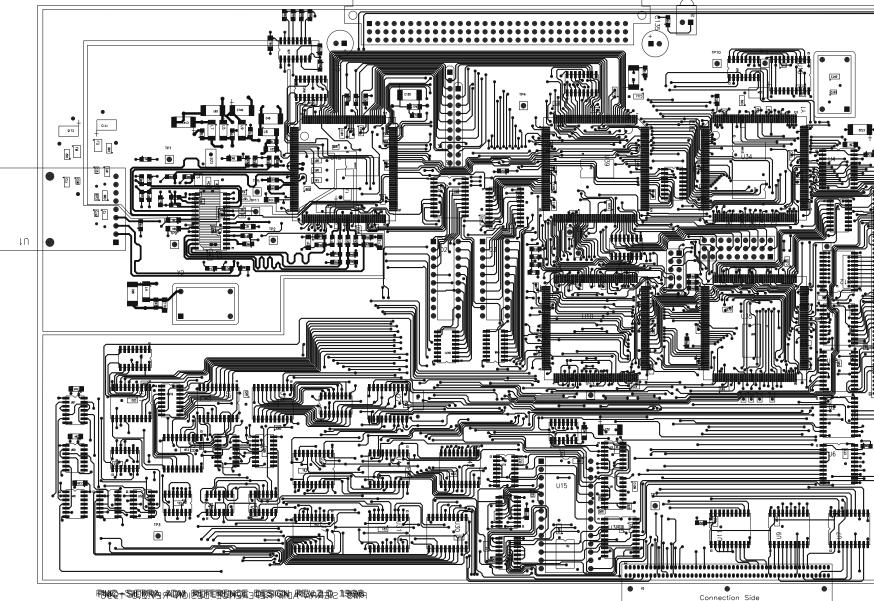

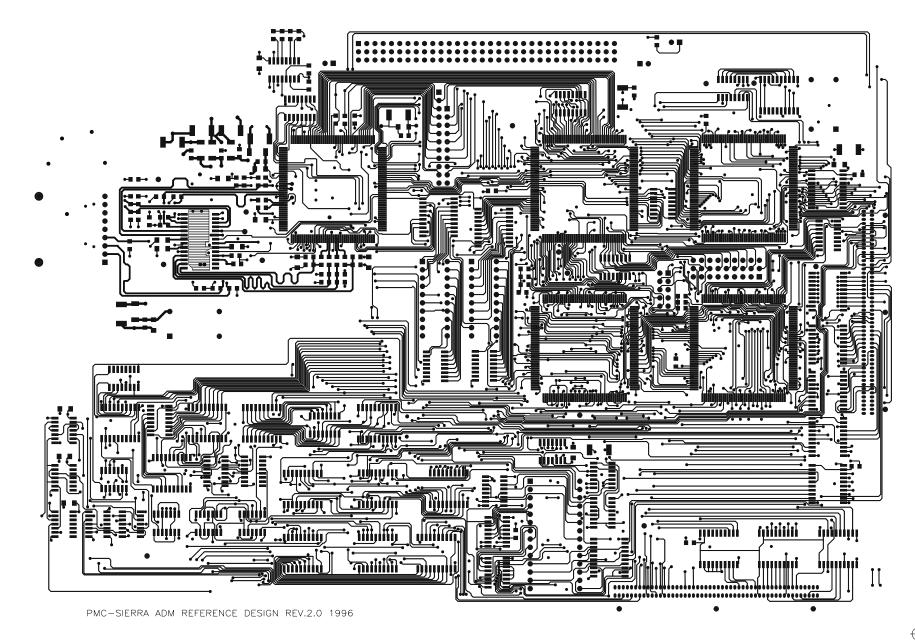

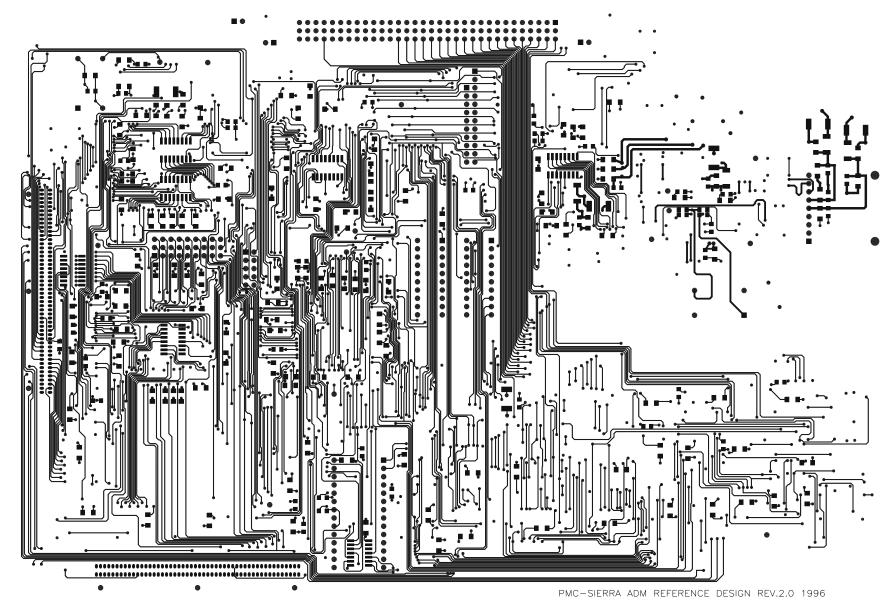

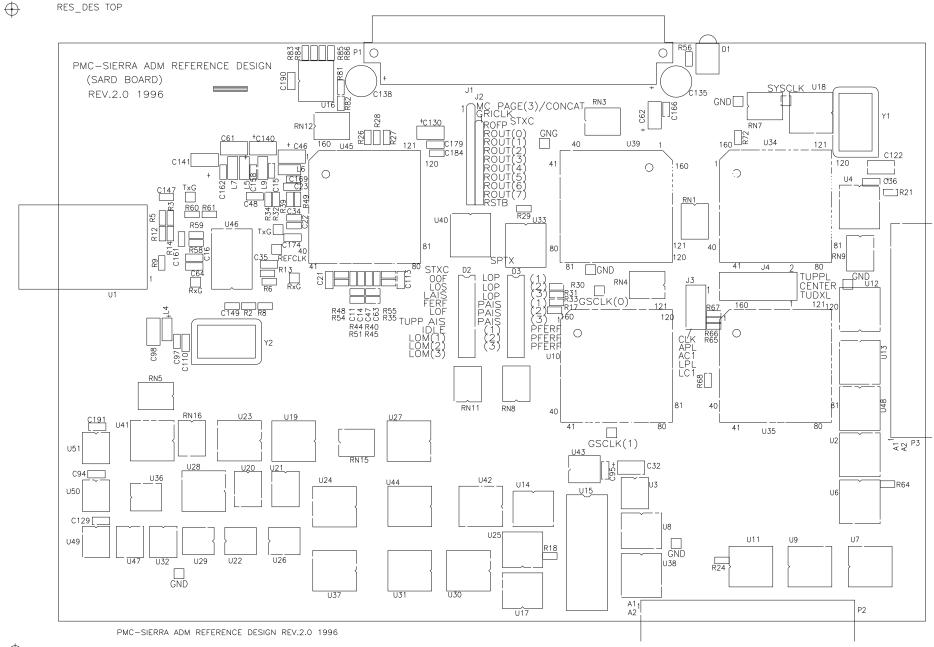

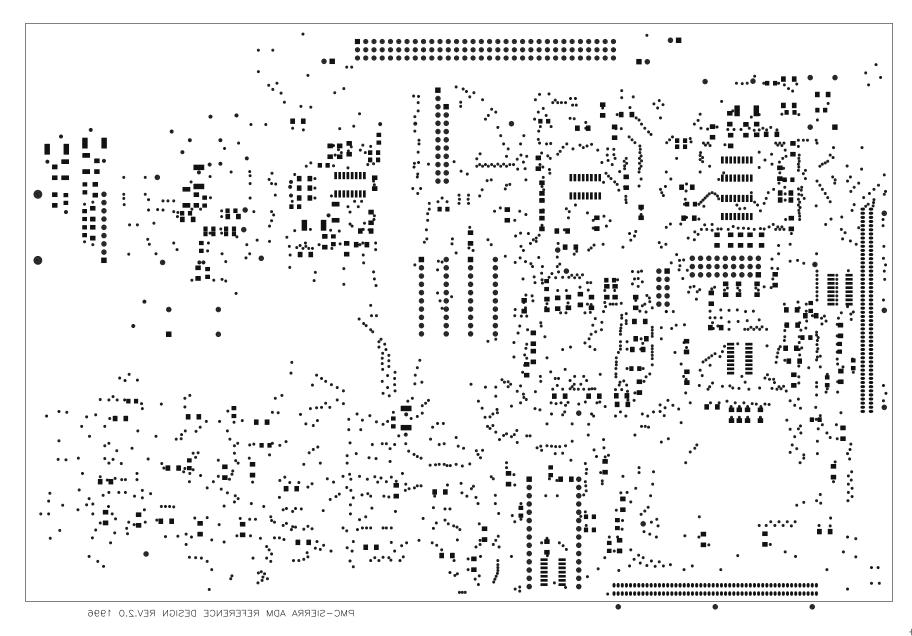

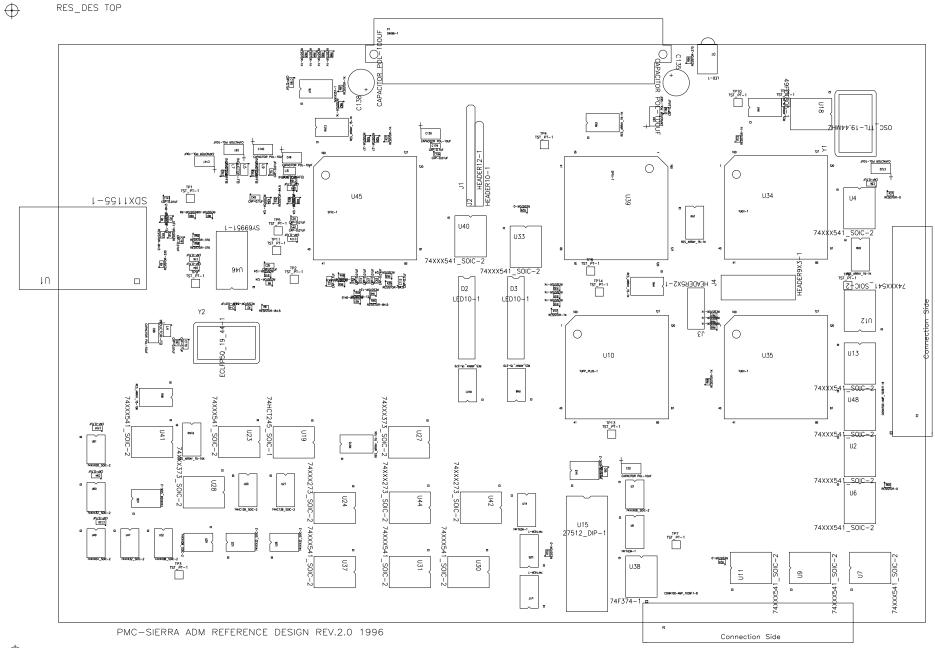

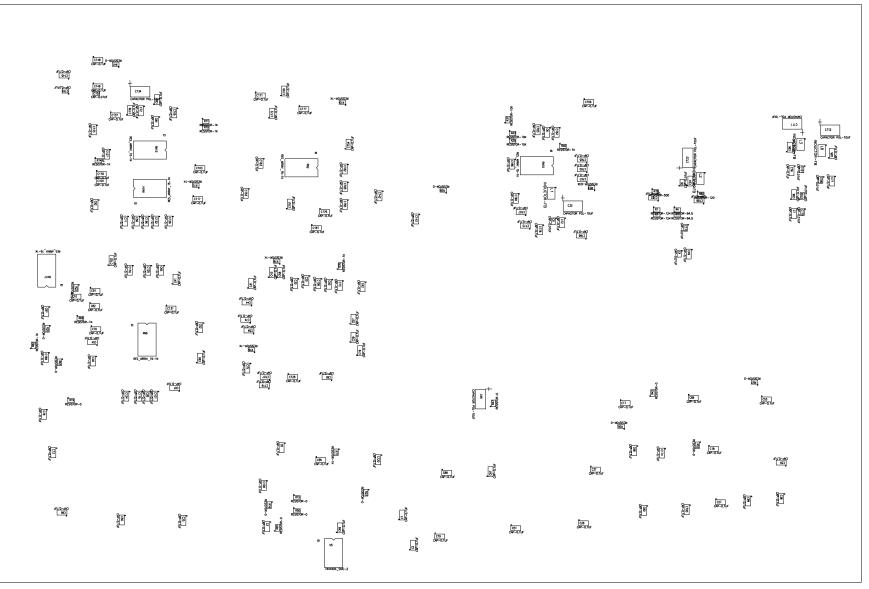

| APP  | ENDIX 3: SCHEMATICS                          | 65 |

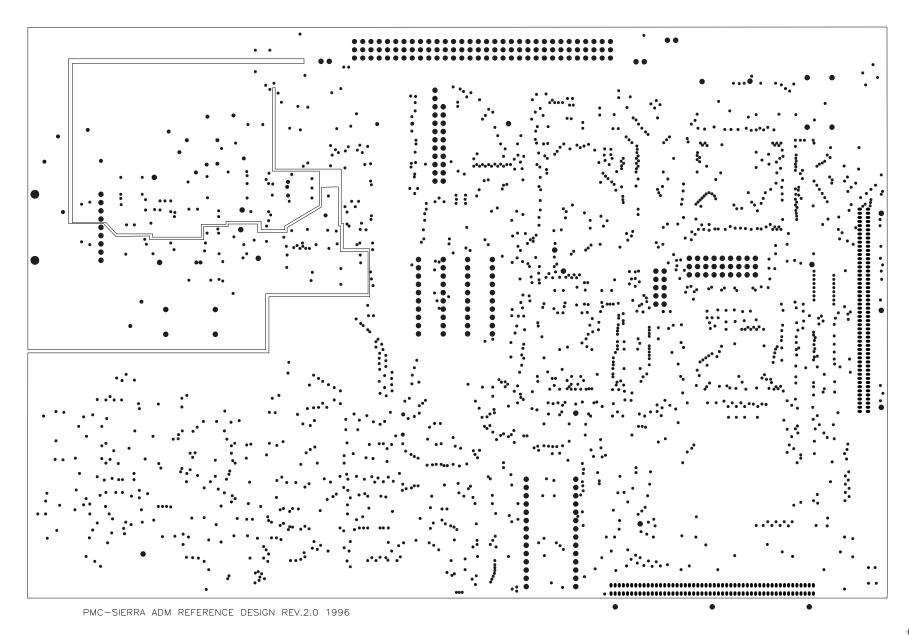

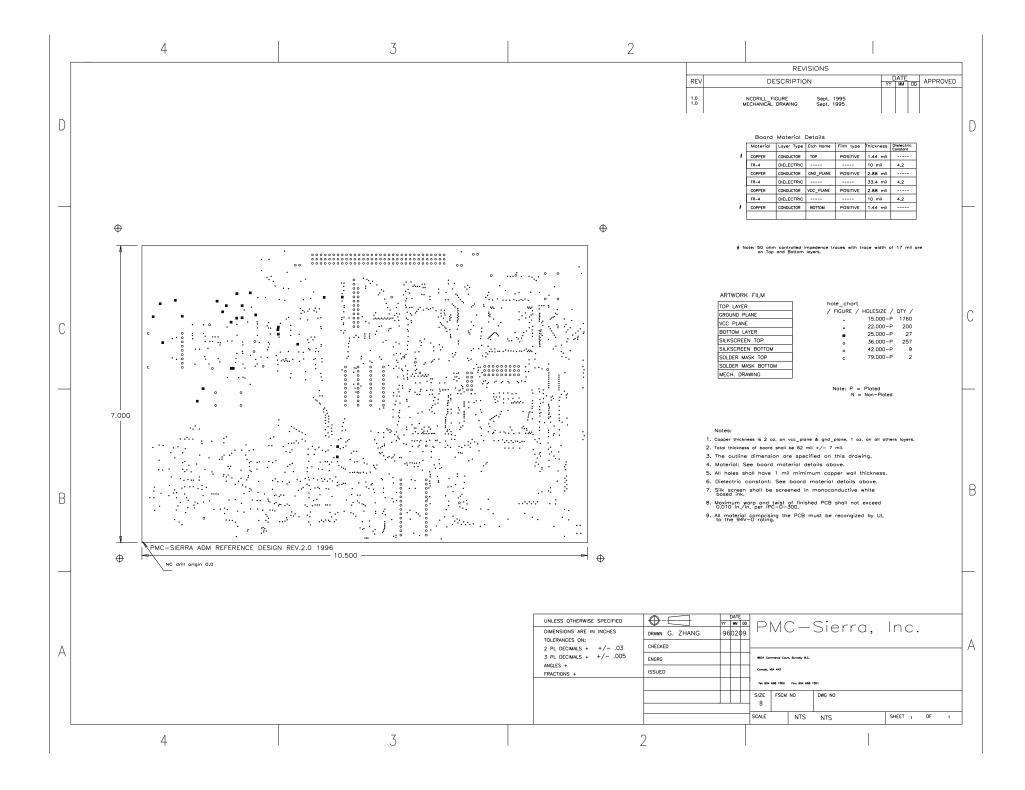

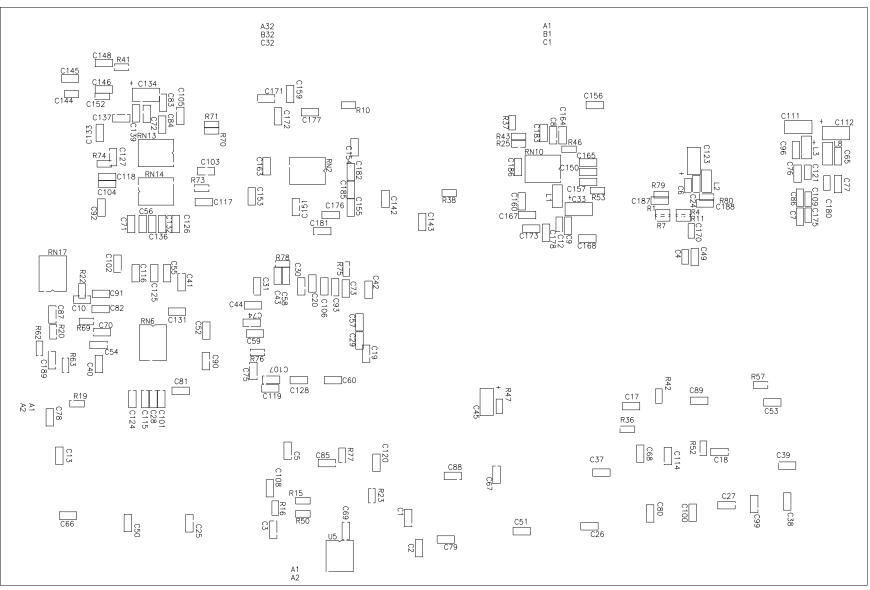

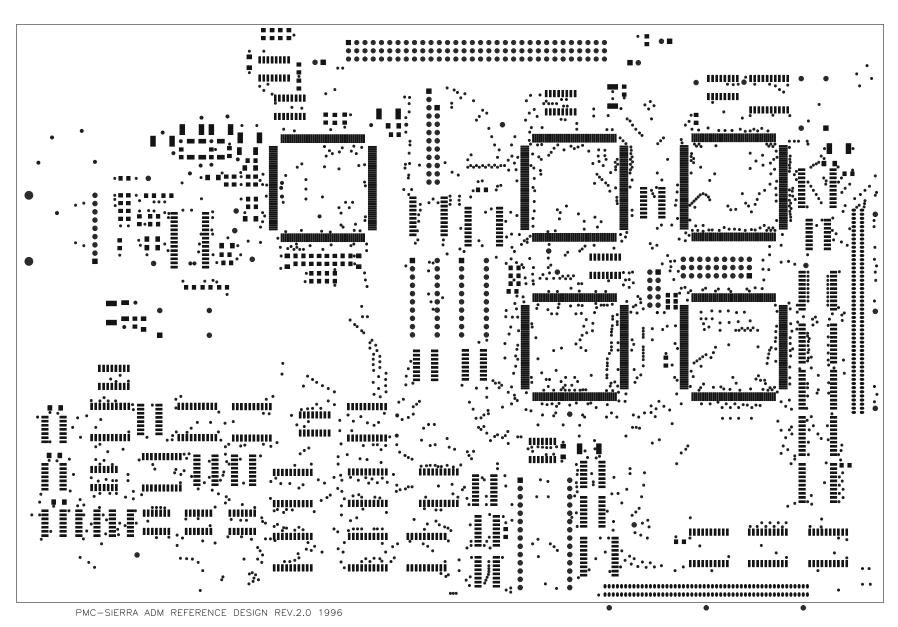

| APP  | ENDIX 4: OTHER LAYOUT DRAWINGS               | 66 |

# **FEATURES**

- Receives an OC-1/OC-3 optical signal and processes section, line and path SONET overhead.

- Performs arbitrary tributary cross-connection to produce a byte serial STS-1, STS-3 (STM-1, AU3), STS-3c (STM-1, AU4) signal.

- Transmits an OC-1/OC-3 [STS-1/STS-3 (STM-1)] stream with an option to overwrite all section, line and path overhead.

- Provides for loop back of both line-side and drop-side signals.

- Recovers line-side receive signal clock.

- Drop-side receive clock may be pleisiochronous to the line-side receive clock.

- Provides on board line-side transmit clock synthesis.

- Drop-side transmit clock may be pleisiochronous to the line-side transmit clock.

- Optionally translates received pointer justification events at the SPE level to tributary pointer justifications, thus locking the SONET SPE to accomplish tributary switching.

- Optionally cross-connects tributaries mapped in the receive stream to any arbitrary time slots in the drop-side stream.

- Allows broadcasting of tributaries over multiple tributaries.

- Provides line side OC-1/OC-3 transmit and receive signals on SC type optical single mode connectors.

- Provides an interface to a proprietary external mapping-demapping function via a 100-pin connector.

- Provides a 100-pin connector for ring expansion and ring control for connection to another PM5543 SARD board.

- Provides a 132-pin connector for microprocessor interface to a PM1501 EVMB motherboard.

SONET/SDH 155Mbit/s ADM Reference Design

# **OVERVIEW**

The SONET/SDH 155 Mbit/s Add-Drop Multiplexor Single Mode Optical Reference Design allows for the evaluation, and demonstration of the PMC SONET/SDH adddrop multiplexor chipset. This reference design illustrates how to implement the front end optics and clock/ data recovery using the CY97B951 and the HP SDX1155 single mode transceiver. This design has been especially designed to mate with itself, the PMC PM1501 EVMB evaluation motherboard and an asynchronous system mapper/demapper daughter board (as yet unspecified) to form a complete add drop node for use in an ADM ring network. This document describes the function of this reference design and also provides complete layout information so that it can be easily duplicated or used as a part of another proprietary design.

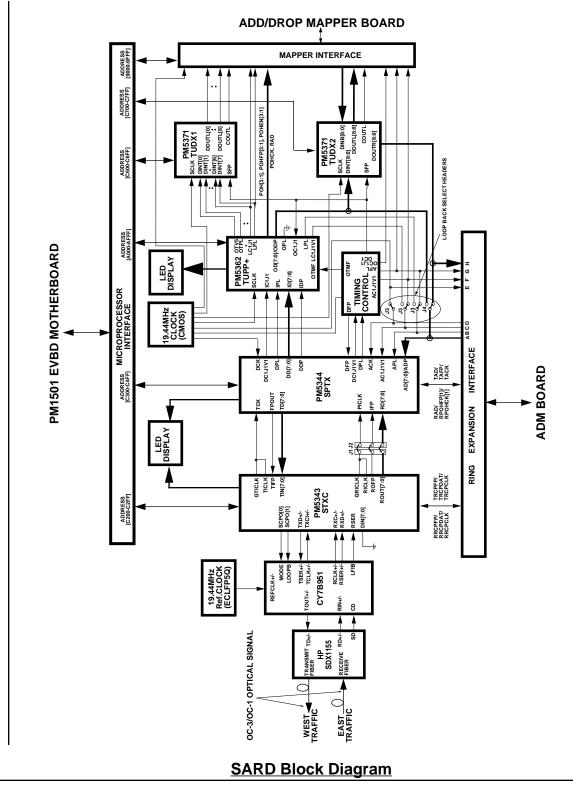

This board utilizes four of the five PMC's Stel/ar (SONET Telecom Architecture) chipset together with the commercially available HP optical transceiver and the Cypress CY7B951 to make up a complete ADM ring node element. The SONET/SDH transport overhead, pointer processing (at the SONET/SDH SPE and VT/TU level) and tributary cross connection are completely handled by the Stel/ar chipset; the section and line is handled by the SONET/SDH Transport Overhead Transceiver (STXC), the path overhead and SPE pointer interpretation is handled by the SONET/SDH Path Overhead Terminating Transceiver (SPTX), the SPE pointer justifications are translated to VT/TU level justifications by the SONET/SDH Tributary Unit Payload Processor (TUPP or TUPP-Plus) and the tributary cross connection is handled by the SONET/SDH Tributary Unit Cross-Connect (TUDX1 and TUDX2).

In the receive direction, the HP optical transceiver receives the OC-1 (or OC-3) optical signal and performs optical to electrical conversion to a differential serial STS-1 (or STS-3) stream. This serial stream is processed by the CY7B951 to extract clock and data before they are passed on to the inputs of the STXC. The STXC performs serial to parallel conversion and terminates the section and line transport overhead and passes the byte serial data to the SPTX. Besides termination of the path overhead, the SPTX supports decoupling of the line side synchronous timing to the system side synchronous timing, the differing rates (19.44MHz ± 20ppm) being adapted by SPE pointer justifications. Received pointer justifications at the system side are compensated by tributary pointer justifications while allowing the SPE envelope to be locked at offset 522 using the TUPP device or at an offset of 0 or 522 using the TUPP-Plus. The data outputs from the TUPP/TUPP-Plus are directly connected to the data inputs of the tributary cross-connect device, TUDX2. The TUPP/TUPP-Plus tributary SPE and tributary V5 position signals, OTSPE and OTV5 respectively, are sent to another TUDX, TUDX1 and TUPP-Plus OTPOH, AIS, IDLE, LC1J1V1, LPL and COUT signals also to be sent to TUDX1. These tributary and frame signals are cross-connected to arbitrary time slots by the two TUDX devices and the cross connected frame is presented to the ADD/DROP Mapper I/F or the Ring Expansion I/F for possible processing by an external mapper or second ADM function.

#### ISSUE 2

SONET/SDH 155Mbit/s ADM Reference Design

In the transmit direction, the reverse process to the receive direction is implemented. The SPTX receives an STS-3 (STM-1) or STS-1 byte serial stream from either the on board TUDX cross connect or the Ring Expansion Interface and inserts the path overhead. The STXC serializes the data to STS-1 or STS-3 rate and transfers the data to the HP optics via the cypress CY7B951. The OC-1/OC-3 signal is then transmitted out to the line.

The SARD board requires an external evaluation motherboard (PM1501 EVMB) for configuration and control. The PM1501 EVMB Evaluation Motherboard, based on a 68HC11 microcontroller, provides processing and communication capability with the daughterboard. The SARD board is connected with the microprocessor motherboard through a 96-pin edge connector. The microcontroller can be connected to a VT100-type terminal through an RS-232 interface.

For details on the operation of the Stel/ar chips or the PM1501 microprocessor motherboard, please consult their respective data sheets as listed in the reference section at the end of this document.

ISSUE 2

SONET/SDH 155Mbit/s ADM Reference Design

### **FUNCTIONAL DESCRIPTION**

SONET/SDH 155Mbit/s ADM Reference Design

### PM5101 Motherboard Interface

The micro control Interface includes all the interface logic required to connect to a standard PMC PM1501 EVMB evaluation motherboard. Bus buffers and transceivers are provided at the interface to reduce loading on the PM1501 EVBD's 68HC11 microprocessor and to increase the drive capability of the interface.

Decode logic provides memory mapped access to all of the on board PMC-Sierra Stel/ar devices (STXC, SPTX, TUPP/TUPP-Plus TUDX1 and TUDX2) and all board level registers. Three read/write registers are provided to control the STXC, SPTX, TUPP/TUPP-Plus, TUDX1 and TUDX2 devices. One of these registers is reserved for future use. The second one is dedicated to the STXC and TIMING CONTROL blocks and is used to control the configuration of these blocks. The third one is a general software reset register used for resetting any device on an individual basis.

### **Optical Interface**

The optical interface consists of the HP SDX1155 intermediate reach (approximately 16 dB per link loss at 1.3  $\mu$ m wavelength) single mode optical transceiver. This device is interchangeable with any multisourced 1X9 pin (lower or higher power) transceiver, or multimode LED transceiver for short haul applications. This reference design is not designed for the long reach separate optical receiver and transmitter modules available today. For long reach designs the layout must be changed to accompany the different footprints of the separate optics pair. However, it is expected that a long reach optical transceiver compatible with the footprint on this board will be available in the near future.

In the receive direction, the HP SDX1155 converts the OC-1 or OC-3 optical signal to a two-level (NRZ) bit serial electrical data stream at the STS-1 or STS-3(STM-1) rate.

In the transmit direction, the HP SDX1155 takes the bit serial STS-1 or STS-3 signal and modulates the laser output as an OC-1 or OC-3 optical data stream.

The optical transceiver uses dual SC/PC type connector.

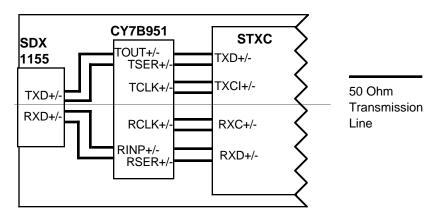

### <u>CY7B951</u>

The Cypress SONET/SDH Serial Transceiver (CY7B951) contains integrated clock and data recovery and clock synthesis. The internal receive PLL recovers a 155.52MHz or a 51.84MHz clock from an incoming NRZ or NRZI data. The differential input data is re-timed by the recovered clock and is presented as a differential PECL bit serial data output. The receive PLL requires a 19.44MHz reference clock to provide a 155.52MHz or 51.84MHz clock in the absence of input data. The reference clock is also used to improve the PLL lock time by training to the approximate frequency of the incoming data stream during optical LOS.

ISSUE 2

SONET/SDH 155Mbit/s ADM Reference Design

The transmit section of the Cypress (CY7B951) SONET/SDH Serial Transceiver contains a PLL that takes a reference clock and multiplies it by 8 to produce a 155.52MHz or 51.84MHz PECL differential output clock. This clock is used by the STXC to transmit PECL differential data. The PECL data from the STXC is then buffered by the CY7B951 before interfacing to the optics.

# Reference Clock

The 19.44MHz reference is an ECL oscillator required for clock and data recovery by the CY7B951. The receive PLL of the CY7B951 utilizes this clock to generate a 155.52MHz or 51.84MHz clock in the absence of input data. Also, the CY7B951 synthesizes a 155.52MHz or 51.84MHz clock for the timing of the transmit bit serial stream. This clock is used by the STXC's TXCI input to time the output bit serial data stream on its TXD+/- outputs.

The reference clock is also used to improve the PLL lock time inside the CY7B951.

# System Clock

A TTL/CMOS level clock is used as a byte serial system clock to drive the SPTX (drop side), TUPP/TUPP-Plus, TUDX1 and TUDX2 circuitry. This clock also accompanies the data sent out on the Mapper Interface and the Ring Expansion Interface.

# <u>STXC</u>

The PM5343 SONET/SDH Transport Overhead Transceiver (STXC) processes the transport overhead (section and line overhead) of an STS-1 or STS-3 (STM-1) stream. The STXC operates to implement SONET/SDH-compliant line interfaces.

The STXC processes either byte serial data at 6.48 Mbyte/s (STS-1) or 19.44 Mbyte/s (STS-3, STM-1), or bit serial data at 51.84 Mbits/s (STS-1) or 155.52 Mbits/s (STS-3, STM-1) on the line side depending on the mode selected. In this design, the STXC implements the bit serial interface only during normal operation. When the optics and clock recovery front end detect a loss of light condition, the STXC is automatically configured to select the byte serial parallel interface. Because of the parallel interface input is tied to ground, the STXC receives all "0". Then the LOS is claimed. The 19.44 MHz RICLK clock input is also switched from the receive sourced clock GRICLK to the transmit sourced clock GTICLK. This allows the STXC to guarantee the detection of an LOS state. Otherwise the parallel interface is not utilized.

On the system side, the STXC either expects or outputs an STS-1 or an STS-3 (STM-1) byte serial stream as determined by the selected operating mode during Stel/ar device programming.

In the receive direction, the STXC frames to the incoming stream, optionally descrambles the receive stream, calculates and compares the bit interleaved parity

ISSUE 2

SONET/SDH 155Mbit/s ADM Reference Design

error detection codes (B1, B2) and accumulates BIP-8 errors (B1, B2) and retransmits the B2 errors as FEBE indications (Z2). Loss of signal (LOS), out of frame (OOF), loss of frame (LOF), far end receive failure (FERF), line alarm indication signal (AIS), and protection switching byte failure alarms are detected. In addition to extracting the entire transport overhead on a dedicated output port, the STXC also extracts and serializes the order wire channels (E1, E2), the data communication channels (D1-D3, D4-D12), the section user channel (F1) and the APS bytes (K1, K2) on their own dedicated output ports.

In the transmit direction, the STXC internally generates all transport overhead bytes with the exception of the H1, H2 and H3 bytes and inserts them into the outgoing SONET stream. Transport overhead bytes can also be inserted using a dedicated transport overhead insertion port or dedicated orderwire or data communication channel ports. In addition, the STXC provides FERF and AIS alarm insertion, loss of signal insertion, framing pattern error insertion, and coding violation insertion (B1 and B2) for diagnostic purposes.

A transmit and receive ring control port which allows alarm and maintenance signal control and status to be passed between mate STXCs is also provided. This feature is useful for ring-based add-drop multiplex applications and is taken advantage of in this design through the Ring Expansion Interface. When the Ring Expansion Interface is not used, the same STXC is used for both the receive and transmit sides of a ring connection.

# <u>SPTX</u>

The SPTX device provides receive path termination for a SONET STS-1, STS-3 or STS-3c stream, or an SDH STM-1 stream carrying three AU3s or one AU4. SPTX interprets the received payload pointers (H1, H2) and extracts the synchronous payload envelope (virtual container). The extracted SPE (VC) is placed on a TeleCombus DROP bus. Frequency offsets (e.g., due to pleisiochronous network boundaries, or the loss of a primary reference timing source) and phase differences (due to normal network operation) between the received data stream and the DROP bus are accommodated by pointer adjustments in the DROP bus. In addition to its basic processing of the received SONET/SDH overhead, the SPTX provides convenient access to all path overhead bytes, which are extracted and serialized on lower rate interfaces, allowing additional external processing of overhead, if desired.

The SPTX device provides transmit path origination for a SONET STS-1, STS-3 or STS-3c stream or an SDH STM-1 stream carrying three AU3s or one AU4. SPTX generates the transmit payload pointers (H1, H2) and inserts the synchronous payload envelope (virtual container) from a TeleCombus ADD bus into the transmit stream. Frequency offsets (e.g., due to pleisiochronous network boundaries, or the loss of a primary reference timing source) and phase differences (due to normal network operation) between the transmit data stream and the ADD buses are accommodated by pointer adjustments in the transmit stream. In addition to its basic processing of the transmit SONET/SDH overhead, the SPTX provides convenient

ISSUE 2

SONET/SDH 155Mbit/s ADM Reference Design

access to all overhead bytes, which are inserted serially on lower rate interfaces, allowing additional external sourcing of overhead, if desired. The SPTX also supports the insertion of a large variety of errors into the transmit stream, such as bit interleaved parity errors and inverted NDF flags, which are useful for system diagnostics and tester applications.

The SPTX device supports in-band error reporting where the path status byte (G1) inserted in the DROP bus reflects the number of BIP-8 errors (B3) detected and the path FERF status. The SPTX can be programmed to pass the path status byte on the ADD bus through unmodified. This feature allows the transmit path processor to be located remotely to the receive processor without having to incur the cost of routing an alarm port.

The SPTX device supports tandem connection termination applications where the tandem connection maintenance byte (Z5) carries the incoming B3 BIP-8 error count, a tandem data link, and a path AIS code. The B3 byte is passed through to the DROP bus after being compensated for the differing Z5 byte, otherwise the B3 byte is unaffected. The incoming error count is accumulated and the receive data link is serialized for external processing. A new data link can be inserted from a low speed serial input. An incoming signal failure alarm (ISF code with IEC field set to 'b1111) is used to convey path AIS in place of all-ones in the pointer (H1, H2).

The SPTX device maintains a large number of statistics for performance monitoring purposes. BIP-8 errors (B3) and tandem path incoming error counts (Z5 IEC) are accumulated. In addition, the SPTX is selectable to accumulate positive and negative pointer justifications that it receives or justifications that it generates on the DROP bus. It also accumulates positive and negative pointer justifications in the transmit stream. Excessive justifications may be indicative of clock synchronization failures.

# TUPP & TUPP-Plus

Either TUPP or TUPP-Plus can be used in this design. When configured for SONET compatible operation, the TUPP or TUPP-Plus transfers all tributaries in the three STS-1 synchronous payload envelopes of an incoming STS-3 byte serial stream to the three STS-1 synchronous payload envelopes of an outgoing STS-3 byte serial stream. Similarly, when configured for SDH compatible operation, the TUPP transfers all tributaries in the single AU4 or three AU3 administrative units of an incoming STM-1 byte serial stream to a single AU4 or three AU3 administrative units of an outgoing STM-1 byte serial stream. The TUPP or TUPP-Plus compensates for pleisiochronous relationships between incoming and outgoing higher level (STS-1, AU4, AU3) synchronous payload envelope frame rates through processing of the lower level (VT6, VT3, VT2, VT1.5, TU3, TU2, TU12, TU11) tributary pointers.

The TUPP or TUPP-Plus is configurable to process any legal mix of tributaries. Each VT group can be configured to carry any one of the four tributary types (VT1.5, VT2, VT3, or VT6) and each TUG2 can be configured to carry any one of three tributary

ISSUE 2

SONET/SDH 155Mbit/s ADM Reference Design

types (TU11, TU12, or TU2). TUG2s can be multiplexed into a VC3 or a TUG3. Alternatively, each TUG3 can be configured to carry a TU3.

The TUPP and TUPP-Plus provides useful maintenance functions. They include detection of loss of pointer and pointer re-acquisition for each tributary, and optional generation of interrupts. The TUPP also allows insertion of tributary path AIS or tributary idle (unequipped). The TUPP can also insert inverted new data flag fields that can be used to diagnose downstream pointer processing elements. The TUPP-Plus implements a superset of the TUPP functionality.

The TUPP-Plus contains tributary performance monitoring and tributary path overhead processing. These functions are not supported by the TUPP. The following functions are exclusive to the TUPP-Plus.

- The TUPP-Plus is configurable to process 16-byte or 64-byte format tributary path trace messages (tributary trail trace identifiers).

- Extracts and serializes the entire tributary path overhead for each tributary into lower speed serial streams.

• Extracts tributary size (SS) bits for each tributary into internal registers. Extracts tributary path trace message (trail trace identifier) for each tributary into internal buffers.

• Provides individual tributary path trace message buffer that holds the expected message and detects tributary path trace mismatch (trail trace identifier mismatch) alarms (TIM) and return to matched state for each tributary and optionally generates interrupts.

• Detects tributary path trace unstable (trail trace identifier unstable) alarms (TIU) and return to stable state for each tributary and optionally generates interrupts.

• Extracts tributary path signal label for each tributary into internal registers and detects change of tributary path signal label events (COPSL) for each tributary and optionally generates interrupts.

• Provides individual tributary path signal label register that hold the expected label and detects tributary path signal label mismatch alarms (PSLM) and return to matched state for each tributary and optionally generates interrupts.

• Detects tributary path signal label unstable alarms (PSLU) and return to stable state for each tributary and optionally generates interrupts.

• Detects tributary unequipped defect (UNEQ) and tributary path defect indication (PDI-V).

ISSUE 2

- Detects assertion and removal of tributary extended remote defect indications (RDI) for each tributary and optionally generates interrupts.

- Calculates and compares the tributary path BIP-2 error detection code for each tributary and configurable to accumulate the BIP-2 errors, on block or bit basis, in internal registers.

• Calculates and compares the TU3 path BIP-8 error detection code for each TU3 stream and accumulates the BIP-8 errors, on block or bit basis, in internal registers.

- Accumulates TU3 tributary far end block errors (FEBE) on a bit or a block basis, in internal registers.

- Allows insertion of all-zeros or all-ones tributary idle code with unequipped indication and valid pointer into any tributary under software control. Idle tributaries are identified by an output signal. Identifies outgoing tributaries that are in AIS state by an output signal.

- Allows software to force the AIS insertion on a per tributary basis.

• Inserts valid H4 byte and all-zeros fixed stuff bytes on the outgoing stream. Remaining path overhead bytes (J1, B3, C2, G1, F2, Z3, Z4, and Z5) can be configured to be set to all-zeros or to reflect the value of the corresponding POH bytes in the incoming stream.

• Inserts valid pointers, and all-zeros transport overhead bytes on the outgoing stream with valid "TeleCombus" control signals when configured to operate in locked mode.

- Supports in-band error reporting by updating the FEBE, RDI and auxiliary RDI bits in the V5 byte (G1 in TU3) with the status of the incoming stream.

- Provides low maximum tributary processing delay of 33  $\mu s$  for VT1.5, 25  $\mu s$  for VT2, 17  $\mu s$  for VT3, and 9  $\mu s$  for VT6 streams.

- provides independently configurable incoming and outgoing interfaces that operate in byte interface mode from a single 19.44 MHz clock or in nibble interface mode from a single 38.88 MHz clock.

- Provides a standard 5 signal IEEE P1149.1 JTAG test port for boundary scan test purposes.

# <u>TUDX</u>

The PM5371 TUDX SONET/SDH Tributary Unit Cross-Connect is a monolithic integrated circuit that allows non-blocking switching of tributaries within two SONET STS-3 or SDH STM-1 streams. Any tributary entering on either stream can be

ISSUE 2

SONET/SDH 155Mbit/s ADM Reference Design

connected to any same size tributary within either outgoing stream. The TUDX can be programmed to cross-connect a mix of SONET VT1.5, VT2, VT3, VT6, or STS-1 channels or SDH TU11, TU12, TU2, or TU3 channels. Programmable idle code can also be inserted into any of these channels. The TUDX allows cross-connection of up to 168 VT1.5 or TU11 streams, up to 126 VT2 or TU12 streams, or up to 42 VT6 or TU2 streams or any legal mix as permitted by the SONET or SDH mappings. In this reference design one stream is provided from the upstream TUPP/TUPP-Plus device whilst the other is provided from an external mapper daughterboard through the Mapper Interface connector. Two TUDXs are used in this design, TUDX1 and TUDX2. The TUDX2 device provides the main data interconnect between the external mapper function and the SARD board. The other TUDX, TUDX1, provides the accompanying control signals that indicate the data condition transported through TUDX2. These control signals are used by the external mapper to decode the presence of tributary payload bytes and tributary V5 bytes.

# Timing Control

The Timing Control circuit contains a 4096 free running counter, a 64K PROM and some other miscellaneous glue logic. The counter starts counting from zero and is initialized to zero after every occurrence of the C1 pulse or a reset. The counter continues to count until the initialization occurs again at the next C1 pulse. The 12 outputs of the counter are used to address an on board PROM that acts as a lookup The lookup values are programmed to account for delays through the table. TUPP/TUPP-Plus and TUDX's. Because these delays are constant, the time when the C1 byte (say) appears on the output of the TUDX2 is predictable. The value of this delay is equal to 280 (5 clock cycles of TUPP/TUPP-Plus and 275 clock cycles of TUDX in STS-3/STS-3c mode) or 100 (5 clock cycles of TUPP/TUPP-Plus and 95 clock cycles of TUDX in STS-1 mode) bytes after the C1 byte appears on the output of the SPTX. These values are equivalent to a count value of 280 or 100 (again, depending on the mode of operation). Therefore, by programming a logic one at this specified location in the PROM a C1 pulse is generated for the data on the output of By programming a series of such locations the AC1J1V1 and APL the TUDX2. signals can be constructed and the outputs of the PROM can be used to control the ADD bus control signals of the SPTX.

The four page control bits (PAGE[0] to PAGE[3) from the board level programmable register(C080H) are used to address higher address's of the PROM and effectively segment the PROM into 16 pages, with each page being 4K deep. Page one is programmed to control the SARD board in STS-3 or STM-1(AU3) mode when the TUPP/TUPP-Plus output is locked with J1 at location 522. Page two is programmed to control the SARD board in STS-3c or STM-1(AU4) mode when the TUPP/TUPP-Plus J1 output is locked at location 522. Page three is programmed to control the SARD board in STS-3c or STM-1(AU4) mode when the TUPP/TUPP-Plus J1 output is locked at location 522. Page three is programmed to control the SARD board in STS-1 mode with J1 output from TUPP/TUPP-Plus locked at location 522. Page four to six are similar to page one to three except this time the TUPP-Plus output is locked with J1 at location 0. Page seven to Page sixteen are reserved for future use.

SONET/SDH 155Mbit/s ADM Reference Design

#### ISSUE 2

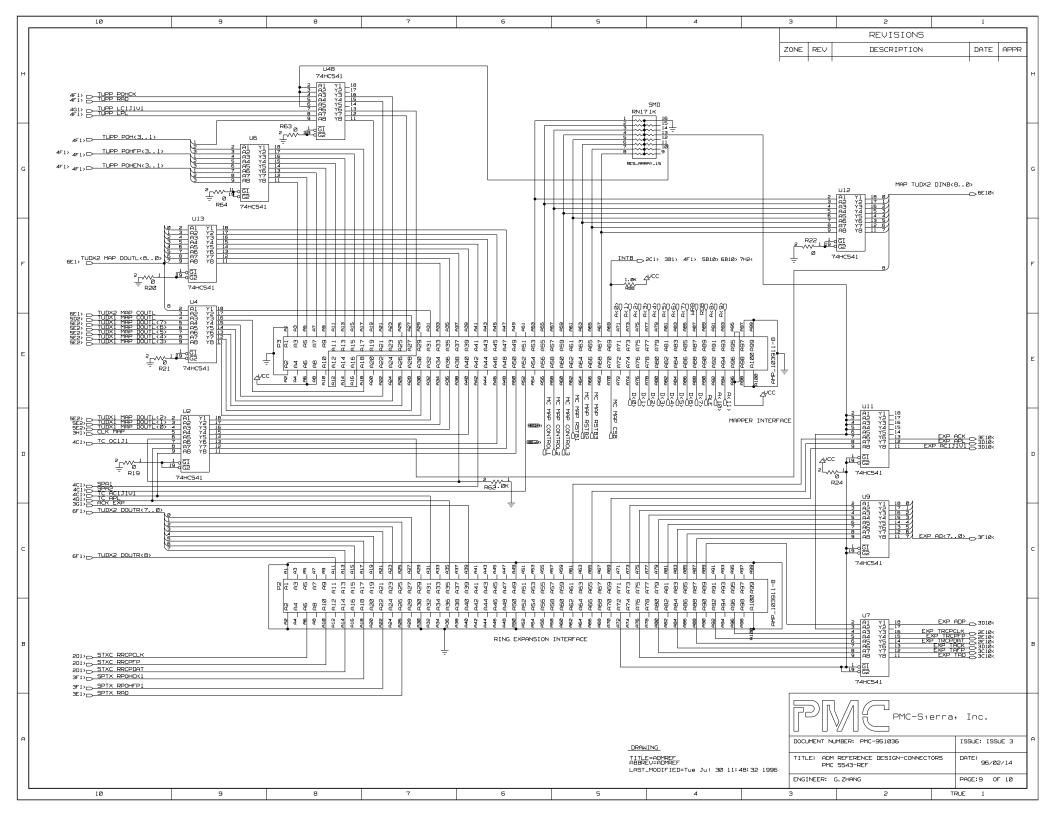

# **Ring Expansion Interface**

This interface contains all the necessary signals to interconnect to a second SARD A single SARD board is equivalent to a single ring network element. To board. construct a duel ring network element (NE), a second board is required to act as the counter rotating protection path. When one SARD board is dedicated to one ring whilst the other board is dedicated to the counter rotating ring, there is no need to interconnect the two boards via the Ring expansion Interface. The Ring Expansion Interface is required when one of the rings of a dual ring network utilizes half the circuitry on one board (for traffic being received by the NE) and half the circuitry on an adjoining board (for traffic being transmitted by the NE). These two configurations require that the Stel/ar devices must be programmed in two different ways. In the first configuration, where the clockwise ring is constructed utilizing board 1 and the counter-clockwise ring is constructed utilizing board 2. the Stel/ar devices must be configured such that they can receive traffic from the East and transmit traffic to the west. This will be referred to as the "East/West Cut" configuration. In the second configuration, where the clockwise ring is constructed by utilizing half of each Stel/ar device on board 1 and the other half of each Stel/ar device on board 2, the Stel/ar devices must be configured such that its receive circuitry handles traffic from the east (on one ring) and its transmit circuitry handles traffic to the east (on the second ring). This will be referred to as the "North/South Cut" configuration.

The Ring Expansion Interface is only useful when implementing the North/South Cut, otherwise there is no need to mate the two boards together. In this configuration, the receive clockwise ring utilizes half the circuitry whilst the transmit counter-clockwise ring utilizes the remaining half. Consequently, the circuitry on the adjoining SARD board must be linked to form a complete NE.

The Ring Expansion Interface contains all the control signals and data signals required to interconnect the traffic from one SARD board to the adjoining SARD board. This includes ring control signals that allow communication between the two remote half's of each Stel/ar device from one board to the other. Ring Expansion interface is activated by appropriately configuring the on board jumpers.

# Mapper Interface

The Mapper Interface allows interfacing to an external asynchronous transport system, such as an E1, T1, E3 or DS3 system. Therefore, this interface includes the complete SONET/SHD frame data and control signals as well as the lower level tributary control signals.

The SONET/SDH drop traffic is interfaced via the DOUTL[8:0] outputs of the TUDX device and the AC1J1V1 and APL control signals from the TIMING CONTROL. The DOUTL[8:0] outputs of TUDX2 contain the SONET/SDH data and the DOUTL[1:0] outputs of TUDX1 contain the lower level tributary control signals OTSPE (or OTPL when TUPP\_Plus is used), OTV5, OTPOH, AIS, IDLE, LC1J1V1, LPL and COUT. The 19.44MHz system clock is also passed through to the Mapper Interface.

#### ISSUE 2

SONET/SDH 155Mbit/s ADM Reference Design

The SONET/SDH add traffic is interfaced via the DINB[8:0] inputs of TUDX2 and the OC1J1 output of the TIMING CONTROL block. The OC1J1 indicates the frame alignment and pointer value that must be applied to the byte serial data inputs on the DINB[8:0] stream. As an option to the OC1J1 control signal, the control signals LC1J1V1 and LPL are also directly connected to the mapper interface to allow generation of SONET/SDH frames aligned to the same alignment as the frames generated by the TUPP-Plus.

The TUPP-Plus tributary overhead signals POH[3:1], POHFP[3:1], POHEN[3:1], POHCK and RAD are connected to the Mapper Interface to provide external tributary path overhead monitoring. Normally this is monitored in the TUPP-Plus and is not required to be done externally.

### LED Displays

Two LED displays are provided to indicate the status of the STXC, SPTX and TUPP devices. When the LED's are lit they indicate the active condition on the STXC's OOF, LOF, LOS, LAIS and FERF outputs, the active condition on the SPTX's PFERF[3:1], PAIS[3:1] and LOP[3:1] outputs and the active condition on the TUPP's IDLE, AIS and LOM[3:1] outputs.

### **Configuration Headers/Jumpers**

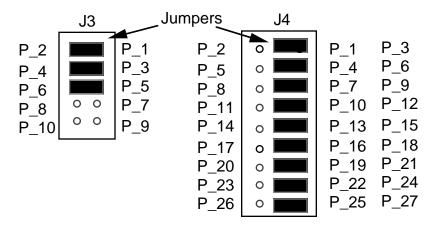

The SARD board contain four configuration headers/jumpers, J1, J2, J3 and J4.

Jumpers J1 and J2 are provided to allow prototype boards to be interconnected between the STXC to SPTX interface. Jumper J1 is a 12 by 1 strip and jumper J2 is a 10 by 1 strip. Normally all pins of jumper J2 are connected to the adjacent pins of jumper J1. The remaining pins of J1 are left unconnected and are for observation only.

The jumpers J3 and J4 provide SPTX an option to select ADD bus signal (ACK, APL, AC1J1V1 and AD[n]) from on board TUPP/TUPP-Plus, TUDX2 or from expansion board. When the Ring Expansion Interface is not used, jumpers J3 and J4 allows the SPTX to select traffic from the TUDX outputs or the TUPP outputs. When a second SARD board is connected to the Ring Expansion Interface, these jumpers must all be disconnected. See the SPTX ADD Bus Clock & Signal Selection Interface section for more information.

SONET/SDH 155Mbit/s ADM Reference Design

# **INTERFACE SIGNAL DESCRIPTION**

### Microprocessor Interface (Connector P1)

This interface consists of a 96 pin male connector that interfaces to the PM1501 EVBD motherboard. Signals on this interface are CMOS/TTL compatible and are used to read and write to on board registers and the memory mapped Stel/ar on chip registers. This interface also provides power and ground connections to the SARD board.

### Microprocessor Interface Signal Description.

| Signal<br>Name | Туре | P1<br>Pin | Function                                                                      |  |

|----------------|------|-----------|-------------------------------------------------------------------------------|--|

| ALE            | I    | C1        | Address latch enable. When high, identifies that address is valid on AD[7:0]. |  |

| E              | I    | C2        | External Data Access Indication. Active high.                                 |  |

| RWB            | I    | СЗ        | Active low write, active high read enable.                                    |  |

| RSTB           | I    | C4        | Active low H/W reset.                                                         |  |

| A[15]          | I    | C5        | Address bus bit 7.                                                            |  |

| A[14]          | I    | C6        | Address bus bit 6.                                                            |  |

| A[13]          | I    | C7        | Address bus bit 5.                                                            |  |

| A[12]          | I    | C8        | Address bus bit 4.                                                            |  |

| A[11]          | I    | C9        | Address bus bit 3.                                                            |  |

| A[10]          | I    | C10       | Address bus bit 2.                                                            |  |

| A[9]           | I    | C11       | Address bus bit 1.                                                            |  |

| A[8]           | I    | C12       | Address bus bit 0.                                                            |  |

| AD[7]          | I/O  | C13       | Multiplexed address/data bus bit 7.                                           |  |

| AD[6]          | I/O  | C14       | Multiplexed address/data bus bit 6.                                           |  |

| AD[5]          | I/O  | C15       | Multiplexed address/data bus bit 5.                                           |  |

| AD[4]          | I/O  | C16       | Multiplexed address/data bus bit 4.                                           |  |

| AD[3]          | I/O  | C17       | Multiplexed address/data bus bit 3.                                           |  |

| AD[2]          | I/O  | C18       | Multiplexed address/data bus bit 2.                                           |  |

| AD[1]          | I/O  | C19       | Multiplexed address/data bus bit 1.                                           |  |

| AD[0]          | I/O  | C20       | Multiplexed address/data bus bit 0.                                           |  |

| PA3            | I    | C21       | 68HC11 Processor Port A bit 3.                                                |  |

| PA4            | I    | C22       | 68HC11 Processor Port A bit 4.                                                |  |

#### ISSUE 2

#### SONET/SDH 155Mbit/s ADM Reference Design

| PA5  | I | C23         | 68HC11 Processor Port A bit 5.                                                                                                  |  |

|------|---|-------------|---------------------------------------------------------------------------------------------------------------------------------|--|

| PA6  | I | C24         | 68HC11 Processor Port A bit 6.                                                                                                  |  |

| PD2  | 0 | C25         | MISO. Master In Slave Out of Port D acting as SPI. Pulled up on motherboard.                                                    |  |

| PD3  | I | C26         | MOSI. Master Out Slave In of Port D acting as SPI. Pulled up on motherboard.                                                    |  |

| PD4  | I | C27         | SCK. Serial clock of Port D acting as SPI. Pulled up on motherboard.                                                            |  |

| PD5  | I | C28         | SS. Slave Select of Port D acting as SPI active low. Pulled up on motherboard.                                                  |  |

| IRQ  | 0 | C29         | Maskable interrupt.                                                                                                             |  |

| XIRQ | 0 | C30         | Non Maskable Interrupt. Not connected.                                                                                          |  |

| DISB | 0 | C31         | EVMB memory disable. Pulling this signal low will disable<br>MPU access to the EVMB's on-board RAM and EPROM.<br>Not connected. |  |

| SP   | 0 | C32         | SPARE.                                                                                                                          |  |

| GND  | 0 | A1-<br>A28  | Ground.                                                                                                                         |  |

| +5V  | 0 | A29-<br>A32 | Power Supply.                                                                                                                   |  |

### **Decoded Microprocessor Signal to Stel/ar chipset Interface**

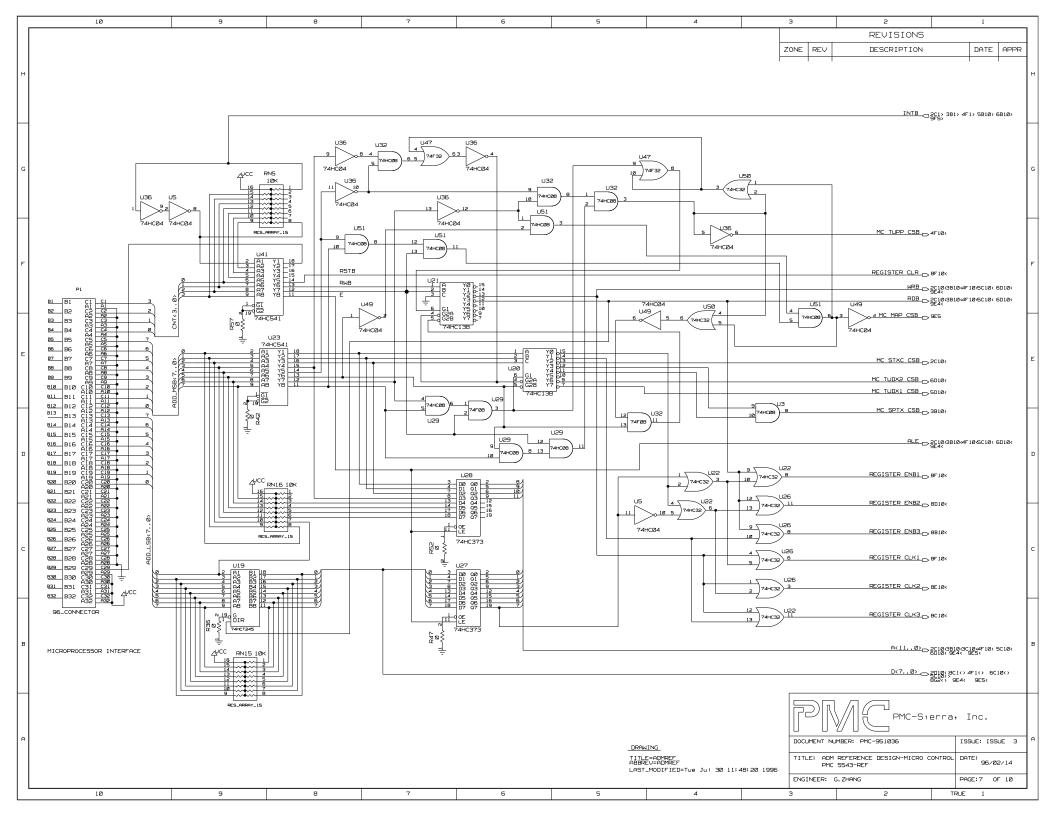

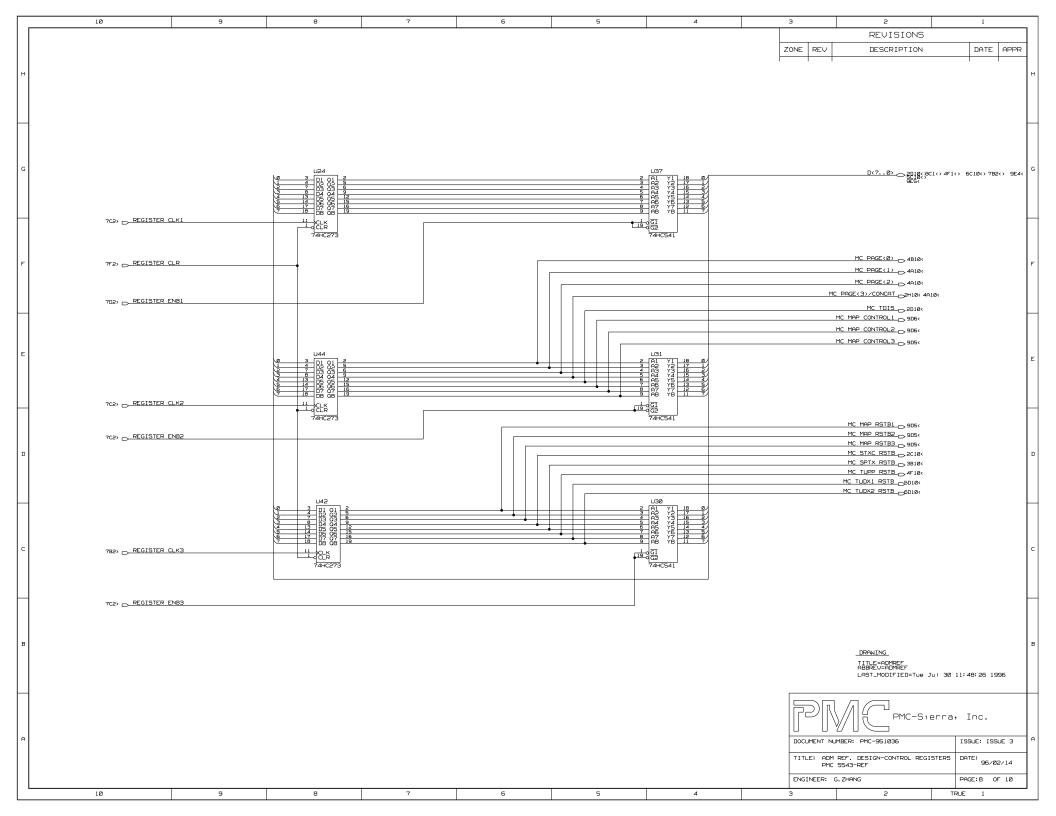

The following table describes the interface between the TUDX, STXC, SPTX and TUPP/TUPP\_Plus, the Mapper Interface with the decoded outputs of the on board microprocessor interface logic. These signals are the inputs and outputs of sheet 7 and 8.

| Signal       | I/O | To/From                                                          | Description                                                                   |

|--------------|-----|------------------------------------------------------------------|-------------------------------------------------------------------------------|

| ALE          | 0   | All Stel/ar Devices<br>and P3                                    | Address latch enable. When high, identifies that address is valid on A[11:0]. |

| INTB         | Ι   | All Stel/ar Devices Interrupt require signal. Active low. and P3 |                                                                               |

| WRB          | 0   | All Stel/ar Devices Active low write strobe signal.<br>and P3    |                                                                               |

| RDB          | 0   | All Stel/ar Devices Active low Read enable select sign and P3    |                                                                               |

| MC STXC RSTB | 0   | STXC                                                             | Active low H/W reset.                                                         |

| MC SPTX RSTB | 0   | SPTX Active low H/W reset.                                       |                                                                               |

| MC TUPP RSTB | 0   | TUPP/TUPP-Plus Active low H/W reset.                             |                                                                               |

SONET/SDH 155Mbit/s ADM Reference Design

| MC TUDX1 RSTB   | 0   | TUDX1                          | Active low H/W reset.               |

|-----------------|-----|--------------------------------|-------------------------------------|

| MC TUDX2 RSTB   | 0   | TUDX2                          | Active low H/W reset.               |

| MC MAP RSTB 1   | 0   | P3                             | Active low H/W reset.               |

| MC MAP RSTB 2   | 0   | P3                             | Active low H/W reset.               |

| MC MAP RSTB 3   | 0   | P3                             | Active low H/W reset.               |

| MC STXC CSB     | 0   | STXC                           | Active low chip select.             |

| MC SPTX CSB     | 0   | SPTX                           | Active low chip select.             |

| MC TUPP CSB     | 0   | TUPP                           | Active low chip select.             |

| MC TUDX1 CSB    | 0   | TUDX1                          | Active low chip select.             |

| MC TUDX2 CSB    | 0   | TUDX2                          | Active low chip select.             |

| MC MAP CSB      | 0   | P3                             | Active low chip select.             |

| A[11]           | 0   | TUPP-Plus P3                   | Address bus bit 11.                 |

| A[10]           | 0   | TUPP-Plus P3                   | Address bus bit 10.                 |

| A[9]            | 0   | TUPP-Plus & P3                 | Address bus bit 9.                  |

| A[8]            | 0   | SPTX TUPP-Plus P3              | Address bus bit 8.                  |

| A[7]            | 0   | SPTX TUPP TUPP-<br>Plus P3     | Address bus bit 7.                  |

| A[6]            | 0   | STXC SPTX TUPP<br>TUPP-Plus P3 | Address bus bit 6.                  |

| A[5]            | 0   | STXC SPTX TUPP<br>TUPP-Plus P3 | Address bus bit 5.                  |

| A[4]            | 0   | All Stel/ar Devices P3         | Address bus bit 4.                  |

| A[3]            | 0   | All Stel/ar Devices P3         | Address bus bit 3.                  |

| A[2]            | 0   | All Stel/ar Devices P3         | Address bus bit 2.                  |

| A[1]            | 0   | All Stel/ar Devices P3         | Address bus bit 1.                  |

| A[0]            | 0   | All Stel/ar Devices P3         | Address bus bit 0.                  |

| D[7]            | I/O | All Stel/ar Devices P3         | Data bus bit 7.                     |

| D[6]            | I/O | All Stel/ar Devices P3         | Data bus bit 6.                     |

| D[5]            | I/O | All Stel/ar Devices P3         | Data bus bit 5.                     |

| D[4]            | I/O | All Stel/ar Devices P3         | Data bus bit 4.                     |

| D[3]            | I/O | All Stel/ar Devices P3         | Data bus bit 3.                     |

| D[2]            | I/O | All Stel/ar Devices P3         | Data bus bit 2.                     |

| D[1]            | I/O | All Stel/ar Devices P3         | Data bus bit 1.                     |

| D[0]            | I/O | All Stel/ar Devices P3         | Data bus bit 0.                     |

| MC MAP CONTROL1 | 0   | P3                             | Control bit reserved for future use |

SONET/SDH 155Mbit/s ADM Reference Design

| MC MAP CONTROL2   | 0 | P3             | Control bit reserved for future use  |

|-------------------|---|----------------|--------------------------------------|

| MC MAP CONTROL3   | 0 | P3             | Control bit reserved for future use  |

| MC TDIS           | 0 | STXC           | Active high transmit disable signal. |

| MC PAGE[0]        | 0 | TIMING CONTROL | PROM address bit 12.                 |

| MC PAGE[1]        | 0 | TIMING CONTROL | PROM address bit 13.                 |

| MC PAGE[2]        | 0 | TIMING CONTROL | PROM address bit 14.                 |

| MC PAGE[3]/CONCAT | 0 | TIMING CONTROL | PROM address bit 15.                 |

### **Prototyping Jumper Interface**

The SARD board provides access to the receive interface between the STXC and the SPTX. This interface can be used to manipulate the SPTX's RECEIVE bus interface. In normal operation the jumpers J1 and J2 are connected as shown below.

| J1  | J2  | J2 Pin Description | J1 Pin Description           |

|-----|-----|--------------------|------------------------------|

|     |     | to                 |                              |

| P_1 |     |                    | MICRO_CONTROL PAGE[3]/CONCAT |

| P_2 |     |                    | STXC GRICLK                  |

| P_3 | P_1 | SPTX IFP           | STXC ROFP                    |

| P_4 | P_2 | SPTX PIN[0]        | STXC ROUT[0]                 |

| P_5 | P_3 | SPTX PIN[1]        | STXC ROUT[1]                 |

| P_6 | P_4 | SPTX PIN[2]        | STXC ROUT[2]                 |

| P_7 | P_5 | SPTX PIN[3]        | STXC ROUT[3]                 |

| P_8 | P_6 | SPTX PIN[4]        | STXC ROUT[4]                 |

SONET/SDH 155Mbit/s ADM Reference Design

| P_9  | P_7  | SPTX PIN[5] | STXC ROUT[5]            |

|------|------|-------------|-------------------------|

| P_10 | P_8  | SPTX PIN[6] | STXC ROUT[6]            |

| P_11 | P_9  | SPTX PIN[7] | STXC ROUT[7]            |

| P_12 | P_10 |             | MICRO_CONTROL STXC RSTB |

# SPTX ADD Bus Clock & Signal Select Interface

When the Ring Expansion Interface is not used, jumpers J3 and J4 allows the SPTX to select traffic from the TUDX outputs or the TUPP outputs. When a second SARD board is connected to the Ring Expansion Interface, these jumpers must all be disconnected. The configuration shown below depicts the case where the TUDX is looped back to the SPTX's ADD bus.

The configuration shown below depicts the case where the TUPP/TUPP\_Plus is looped back to the SPTX's ADD bus.

|                                  | J3 | Ju                              | mpers                                                             | J4 |                   |                                                                   |                                                                           |

|----------------------------------|----|---------------------------------|-------------------------------------------------------------------|----|-------------------|-------------------------------------------------------------------|---------------------------------------------------------------------------|

| P_2<br>P_4<br>P_6<br>P_8<br>P_10 |    | P_1<br>P_3<br>P_5<br>P_7<br>P_9 | P_2<br>P_5<br>P_8<br>P_11<br>P_14<br>P_17<br>P_20<br>P_23<br>P_26 |    | 0 0 0 0 0 0 0 0 0 | P_1<br>P_4<br>P_7<br>P_10<br>P_13<br>P_16<br>P_19<br>P_22<br>P_25 | P_3<br>P_6<br>P_9<br>P_12<br>P_15<br>P_15<br>P_18<br>P_21<br>P_24<br>P_27 |

ISSUE 2

ISSUE 2

#### SONET/SDH 155Mbit/s ADM Reference Design

| J3              | Description                                                  |  |  |

|-----------------|--------------------------------------------------------------|--|--|

| PIN 1-2 CLOSE   | Selects the on board 19.44 MHz crystal as the DROP bus clock |  |  |

| PIN 3-4 CLOSE   | Selects APL from TIMING CONTROL                              |  |  |

| PIN 5-6 CLOSE   | Selects AC1J1V1 from TIMING CONTROL                          |  |  |

| PIN 7-8 CLOSE   | Selects LPL from TUPP-Plus                                   |  |  |

| PIN 9-10 CLOSE  | Selects LC1J1V1 from TUPP-Plus                               |  |  |

| ALL PINS OPEN   | Selects the Ring Expansion Interface                         |  |  |

|                 |                                                              |  |  |

| J4              | Description                                                  |  |  |

| PIN 1-3 CLOSE   | Selects the on board TUDX2 DOUTR(0) for loop back            |  |  |

| PIN 4-6 CLOSE   | Selects the on board TUDX2 DOUTR(1) for loop back            |  |  |

| PIN 7-9 CLOSE   | Selects the on board TUDX2 DOUTR(2) for loop back            |  |  |

| PIN 10-12 CLOSE | Selects the on board TUDX2 DOUTR(3) for loop back            |  |  |

| PIN 13-15 CLOSE | Selects the on board TUDX2 DOUTR(4) for loop back            |  |  |

| PIN 16-18 CLOSE | Selects the on board TUDX2 DOUTR(5) for loop back            |  |  |

| PIN 19-21 CLOSE | Selects the on board TUDX2 DOUTR(6) for loop back            |  |  |

| PIN 22-24 CLOSE | Selects the on board TUDX2 DOUTR(7) for loop back            |  |  |

| PIN 25-27 CLOSE | Selects the on board TUDX2 DOUTR(8) for loop back            |  |  |

| PIN 2-3 CLOSE   | Selects the on board TUPP-Plus OD(0) for loop back           |  |  |

| PIN 5-6 CLOSE   | Selects the on board TUPP-Plus OD(1) for loop back           |  |  |

| PIN 8-9 CLOSE   | Selects the on board TUPP-Plus OD(2) for loop back           |  |  |

| PIN 1112 CLOSE  | Selects the on board TUPP-Plus OD(3) for loop back           |  |  |

| PIN 14-15 CLOSE | Selects the on board TUPP-Plus OD(4) for loop back           |  |  |

| PIN 17-18 CLOSE | Selects the on board TUPP-Plus OD(5) for loop back           |  |  |

| PIN 20-21 CLOSE | Selects the on board TUPP-Plus OD(6) for loop back           |  |  |

| PIN 23-24 CLOSE | Selects the on board TUPP-Plus OD(7) for loop back           |  |  |

| PIN 26-27 CLOSE | Selects the on board TUPP-Plus ODP for loop back             |  |  |

| ALL PINS OPEN   | Select the ADD signal from mated ADM board                   |  |  |

|                 |                                                              |  |  |

# HP SDX1155 Optics to/from Cypress CY7B951 Interface

| SDX<br>Signal | SDX<br>Type | СҮ7В-<br>Туре | CY7B-<br>Signal | Description                                |

|---------------|-------------|---------------|-----------------|--------------------------------------------|

| RXDP          | 0           | I             | RINP            | Bit serial line side receive data positive |

| RXDN          | 0           | I             | RINN            | Bit serial line side receive data negative |

ISSUE 2

#### SONET/SDH 155Mbit/s ADM Reference Design

| SD   | 0 | I | CD    | Carrier detect signal, low fail             |

|------|---|---|-------|---------------------------------------------|

| TXDP | I | 0 | TOUTP | Bit serial line side transmit data positive |

| TXDN | I | 0 | TOUTN | Bit serial line side transmit data negative |

# Cypress CY7B951 to/from STXC Interface

| CY7B<br>Signal | CY7B<br>Type | STXC<br>Type | STXC<br>Signal | Description                               |

|----------------|--------------|--------------|----------------|-------------------------------------------|

| RCLKP          | 0            | I            | RXCP           | Receive clock positive                    |

| RCLKN          | 0            | I            | RXCN           | Receive clock negative                    |

| RSERP          | 0            | I            | RXDP           | Bit serial Receive data positive          |

| RSERN          | 0            | I            | RXDN           | Bit serial Receive data negative          |

| MODE           | I            | 0            | SCPO(0)        | Mode control, low STS-1, high STS-3/STM-1 |

| LOOP           | I            | 0            | SCPO(1)        | Loop control, low loopback, high open     |

| LFI*           | 0            | I            | RESR           | Line fault indication, low line fault     |

| TCLKP          | 0            | I            | TXCP           | Transmit clock positive                   |

| TCLKN          | 0            | I            | TXCN           | Transmit clock negative                   |

| TSERP          | I            | 0            | TXDP           | Bit serial transmit data positive         |

| TSERN          | I            | 0            | TXDN           | Bit serial transmit data negative         |

# STXC to/from SPTX Interface

| STXC<br>Signal | STXC<br>Type | SPTX<br>Type | SPTX<br>Signal | Description                |

|----------------|--------------|--------------|----------------|----------------------------|

| GRICLK         | 0            | I            | RCK            | Byte serial receive clock  |

| ROFP           | 0            | I            | IFP            | Receive frame pulse        |

| ROUT[7]        | 0            | I            | RD[7]          | Byte serial data bit 7     |

| ROUT[6]        | 0            | I            | RD[6]          | Byte serial data bit 6     |

| ROUT[5]        | 0            | I            | RD[5]          | Byte serial data bit 5     |

| ROUT[4]        | 0            | I            | RD[4]          | Byte serial data bit 4     |

| ROUT[3]        | 0            | I            | RD[3]          | Byte serial data bit 3     |

| ROUT[2]        | 0            | I            | RD[2]          | Byte serial data bit 2     |

| ROUT[1]        | 0            | I            | RD[1]          | Byte serial data bit 1     |

| ROUT[0]        | 0            | I            | RD[0]          | Byte serial data bit 0     |

| GTICLK         | 0            | I            | TCK            | Byte serial transmit clock |

| TIFP           | I            | 0            | FPOUT          | Transmit frame pulse       |

ISSUE 2

SONET/SDH 155Mbit/s ADM Reference Design

| TIN[7] | I | 0 | TD[7] | Byte serial data bit 7 |

|--------|---|---|-------|------------------------|

| TIN[6] | I | 0 | TD[6] | Byte serial data bit 6 |

| TIN[5] | I | 0 | TD[5] | Byte serial data bit 5 |

| TIN[4] | I | 0 | TD[4] | Byte serial data bit 4 |

| TIN[3] | I | 0 | TD[3] | Byte serial data bit 3 |

| TIN[2] | I | 0 | TD[2] | Byte serial data bit 2 |

| TIN[1] | I | 0 | TD[1] | Byte serial data bit 1 |

| TIN[0] | I | 0 | TD[0] | Byte serial data bit 0 |

# SPTX to/from TUPP/TUPP-Plus Interface

| SPTX<br>Signal | SPTX<br>Type | TUPP<br>Type | TUPP<br>Signal | Description               |

|----------------|--------------|--------------|----------------|---------------------------|

| DD[7]          | 0            | I            | DIN/ID[7]      | Byte serial data bit 7    |

| DD[6]          | 0            | I            | DIN/ID[6]      | Byte serial data bit 6    |

| DD[5]          | 0            | I            | DIN/ID[5]      | Byte serial data bit 5    |

| DD[4]          | 0            | I            | DIN/ID[4]      | Byte serial data bit 4    |

| DD[3]          | 0            | I            | DIN/ID[3]      | Byte serial data bit 3    |

| DD[2]          | 0            | I            | DIN/ID[2]      | Byte serial data bit      |

| DD[1]          | 0            | I            | DIN/ID[1]      | Byte serial data bit 1    |

| DD[0]          | 0            | I            | DIN/ID[0]      | Byte serial data bit 0    |

| DC1J1V1        | 0            | I            | IC1J1          | C1, J1 and V1 frame pulse |

| DDP            | 0            | I            | IPAR/IDP       | Data parity               |

| DPL            | 0            | I            | ISPE/IPL       | Payload active signal     |

# SPTX to/from TIMING CONTROL(TC) block Interface

| SPTX<br>Signal | SPTX<br>Type | ТС<br>Туре | TC<br>Signal | Description               |

|----------------|--------------|------------|--------------|---------------------------|

| DC1J1V1        | 0            | Ι          | DC1J1V1      | C1, J1 and V1 frame pulse |

| DPL            | 0            | I          | DPL          | Payload active signal     |

# **TUPP/TUPP-Plus to/from TUDX1 Interface**

| TUPP<br>Signal | TUPP<br>Type | - | TUDX1<br>Signal | Description                |

|----------------|--------------|---|-----------------|----------------------------|

| OTV5           | 0            | Ι | DINT[0]         | Outgoing tributary V5 byte |

SONET/SDH 155Mbit/s ADM Reference Design

| OTSPE/  | 0 | I | DINT[1] | Outgoing tributary payload envelope     |

|---------|---|---|---------|-----------------------------------------|

| OTPL    |   |   |         |                                         |

| ОТРОН   | 0 | I | DINT[2] | Outgoing tributary path overhead signal |

| AIS     | 0 | I | DINT[3] | Tributary alarm indication signal       |

| IDLE    | 0 | I | DINT[4] | Tributary idle indication signal        |

| LC1J1V1 | 0 | I | DINT[5] | Locked mode composite frame pulse       |

| LPL     | 0 | I | DINT[6] | Locked mode payload active signal       |

| COUT    | 0 | I | DINT[7] | Controlled output signal                |

# TUPP/TUPP-Plus to/from TUDX2 Interface

| TUPP<br>Signal    | TUPP<br>Type | TUDX<br>Type | TUDX2<br>Signal | Description                 |

|-------------------|--------------|--------------|-----------------|-----------------------------|

| OPAR/<br>ODP      | 0            | Ι            | DINT[8]         | Outgoing data parity signal |

| DOUT[7]/<br>OD[7] | 0            | Ι            | DINT[7]         | Byte serial data bit 7      |

| DOUT[6]/<br>OD[6] | 0            | Ι            | DINT[6]         | Byte serial data bit 6      |

| DOUT[5]/<br>OD[5] | 0            | I            | DINT[5]         | Byte serial data bit 5      |

| DOUT[4]/<br>OD[4] | 0            | I            | DINT[4]         | Byte serial data bit 4      |

| DOUT[3]/<br>OD[3] | 0            | I            | DINT[3]         | Byte serial data bit 3      |

| DOUT[2]/<br>OD[2] | 0            | I            | DINT[2]         | Byte serial data bit 2      |

| DOUT[1]/<br>OD[1] | 0            | I            | DINT[1]         | Byte serial data bit 1      |

| DOUT[0]/<br>OD[0] | 0            | Ι            | DINT[0]         | Byte serial data bit 0      |

# TUPP from TIMING CONTROL(TC) Interface

| TUPP<br>Signal | TUPP<br>Type | TC<br>Type | TC<br>Signal | Description                         |

|----------------|--------------|------------|--------------|-------------------------------------|

| OTMF           | Ι            | 0          | OTMF         | Outgoing tributary multiframe pulse |

| OC1J1          | I            | 0          | OC1          | C1 and J1 frame pulse               |

SONET/SDH 155Mbit/s ADM Reference Design

# TUDX1 from TIMING CONTROL(TC) Interface

| TUDX   | TUDX | ТС   | TC     | Description   |

|--------|------|------|--------|---------------|

| Signal | Type | Туре | Signal |               |

| OC1    | I    | 0    | OC1    | C1 framepulse |

# TUDX2 from TIMING CONTROL(TC) Interface

| TUDX   | TUDX | TC   | TC     | Description    |

|--------|------|------|--------|----------------|

| Signal | Type | Type | Signal |                |

| OC1    | I    | 0    | OC1    | C1 frame pulse |

# **19.44MHz System Clock Distribution Interface**

| System<br>Clock (Hz) | То                             | Name at<br>Destination | Description                                  |

|----------------------|--------------------------------|------------------------|----------------------------------------------|

| 19.44MHZ             | MAPPER<br>INTERFACE            | CLK MAP                | Clock to Mapper Interface                    |

| 19.44MHZ             | TIMING<br>CONTROL              | CLK TC                 | 19.44Mbyte/s Clock to TIMING CONTROL         |

| 19.44MHZ             | TUPP                           | SCLK TUPP              | Byte serial down stream data clock           |

| 19.44MHZ             | TUDX1                          | SCLK TUDX1             | Byte serial tributary cross connection clock |

| 19.44MHZ             | TUDX2                          | SCLK TUDX2             | Byte serial tributary cross connection clock |

| 19.44MHZ             | RING<br>EXPANSION<br>INTERFACE | ACK EXP                | Clock to Ring Expansion Interface            |

| 19.44MHZ             | J3                             | ACK                    | Byte serial up stream data loopback clock    |

| 19.44MHZ             | SPTX                           | DCK                    | Byte serial Down stream data clock           |

# TIMING CONTROL(TC) Interface

| Signal  | I/O | To/From                                | Description                          |

|---------|-----|----------------------------------------|--------------------------------------|

| DC1J1V1 | I   | SPTX                                   | Required for counter synchronization |

| DPL     | I   | SPTX                                   | Required for counter synchronization |

| CLK     | I   | тс                                     | 19.44Mbyte/s clock                   |

| OTMF    | 0   | TUPP/ TUPP -<br>Plus                   | Tributary multiframe synchronization |

| OC1     | 0   | TUPP/ TUPP -<br>Plus , TUDX1,<br>TUDX2 | C1 frame pulse                       |

#### SONET/SDH 155Mbit/s ADM Reference Design

| OC1J1   | 0 | Mapper<br>Interface                                        | C1 and J1 synchronization for input data from Mapper Interface                                                |

|---------|---|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| AC1J1V1 | Ο | J3, Ring<br>Expansion<br>Interface,<br>Mapper<br>Interface | C1, J1 and V1 synchronization for input data<br>from TUDX2 output on matted ADM board or<br>Mapper Interface. |

| APL     | 0 | Ring<br>Expansion<br>Interface,<br>Mapper<br>Interface     | Payload active signal for data on TUDX2 outputs.                                                              |

| OC1J1   | 0 | Mapper<br>Interface                                        | Mapper ADD traffic C1 and J1 synchronization                                                                  |

| SPA0    | 0 | Unused                                                     | Unused                                                                                                        |

| SPA1    |   | Mapper                                                     | Spare control bits for mapping interface                                                                      |

| SPA2    |   | Interface                                                  |                                                                                                               |

# **Ring Expansion Interface**

| Signal            | I/O | P2<br>pin | Description                               |  |

|-------------------|-----|-----------|-------------------------------------------|--|

| ACK EXP           | 0   | A39       | 19.44MHz clock                            |  |

| TC APL            | 0   | A35       | ADD bus payload signal                    |  |

| TC AC1J1V1        | 0   | A31       | ADD bus C1, J1, V1 synchronization signal |  |

| EXP ACK           | I   | A61       | 19.44MHz clock                            |  |

| EXP APL           | I   | A65       | ADD bus payload signal                    |  |

| EXP AC1J1V1       | I   | A69       | ADD bus C1, J1, V1 synchronization signal |  |

| TUDX2<br>DOUTR[8] | 0   | A11       | ADD bus data parity signal                |  |

| TUDX2<br>DOUTR[7] | 0   | A13       | ADD bus data bit 7                        |  |

| TUDX2<br>DOUTR[6] | 0   | A15       | ADD bus data bit 6                        |  |

| TUDX2<br>DOUTR[5] | 0   | A17       | ADD bus data bit 5                        |  |

| TUDX2<br>DOUTR[4] | 0   | A19       | ADD bus data bit 4                        |  |

| TUDX2<br>DOUTR[3] | 0   | A21       | ADD bus data bit 3                        |  |

#### ISSUE 2

#### SONET/SDH 155Mbit/s ADM Reference Design

| TUDX2             | 0 | A23 | ADD bus data bit 2                     |

|-------------------|---|-----|----------------------------------------|

| DOUTR[2]          | 0 | AZS | ADD bus data bit 2                     |

| TUDX2<br>DOUTR[1] | 0 | A25 | ADD bus data bit 1                     |

| TUDX2<br>DOUTR[0] | 0 | A27 | ADD bus data bit 0                     |

| EXP ADP           | I | A89 | ADD bus data parity signal             |

| EXP AD[7]         | I | A87 | ADD bus data bit 7                     |

| EXP AD[6]         | I | A85 | ADD bus data bit 6                     |

| EXP AD[5]         | I | A83 | ADD bus data bit 5                     |

| EXP AD[4]         | I | A81 | ADD bus data bit 4                     |

| EXP AD[3]         | I | A79 | ADD bus data bit 3                     |

| EXP AD[2]         | I | A77 | ADD bus data bit 2                     |

| EXP AD[1]         | I | A75 | ADD bus data bit 1                     |

| EXP AD[0]         | I | A73 | ADD bus data bit 0                     |

| STXC<br>RRCPCLK   | 0 | A6  | Receive Ring control port clock        |

| STXC<br>RRCPFP    | 0 | A10 | Receive Ring control port frame pulse  |

| STXC<br>RRCPDAT   | 0 | A14 | Receive Ring control port data         |

| STXC<br>TRCPCLK   | I | A96 | Transmit Ring control port clock       |

| STXC TRCPFP       | I | A92 | Transmit Ring control port frame pulse |

| STXC<br>TRCPDAT   | I | A88 | Transmit Ring control port data        |

| SPTX<br>RPOHCK1   | 0 | A18 | Receive path overhead clock1           |

| SPTX<br>RPOHFP1   | 0 | A22 | Receive path overhead frame pulse 1    |

| SPTX RAD          | 0 | A26 | Receive alarm port data signal         |

| EXP TACK          | I | A84 | Transmit alarm port clock              |

| EXP TAFP          | I | A80 | Transmit alarm port frame signal       |

| EXP TAD           | I | A76 | Transmit alarm port data signal        |

#### ISSUE 2

#### SONET/SDH 155Mbit/s ADM Reference Design

| GND | A1<br>A2<br>A30<br>A49<br>A50<br>A90 | Ground |

|-----|--------------------------------------|--------|

|     | A99<br>A100                          |        |

# **Mapper Interface**

| Signal                | I/O | P3<br>pin | Description                                              |

|-----------------------|-----|-----------|----------------------------------------------------------|

| CLK MAP               | 0   | A40       | 19.44MHz clock                                           |

| TUDX1 MAP<br>DOUTL[0] | 0   | A36       | DROP tributary V5 byte indication                        |

| TUDX1 MAP<br>DOUTL[1] | 0   | A34       | DROP tributary synchronous payload envelope signal marks |

| TUDX1 MAP<br>DOUTL[2] | 0   | A32       | Outgoing tributary path overhead signal                  |

| TUDX1 MAP<br>DOUTL[3] | 0   | A30       | Tributary alarm indication signal                        |

| TUDX1 MAP<br>DOUTL[4] | 0   | A28       | Tributary idle indication signal                         |

| TUDX1 MAP<br>DOUTL[5] | 0   | A26       | Locked mode composite frame pulse                        |

| TUDX1 MAP<br>DOUTL[6] | 0   | A24       | Locked mode payload active signal                        |

| TUDX1 MAP<br>DOUTL[7] | 0   | A22       | Controlled output signal                                 |

| TUDX1 MAP<br>COUTL    | 0   | A18       | Left control output signal                               |

| TUDX2 MAP<br>COUTL    | 0   | A27       | Left control output signal                               |

| TUDX2 MAP<br>DOUTL[8] | 0   | A31       | DROP bus data parity signal                              |

| TUDX2 MAP<br>DOUTL[7] | 0   | A33       | DROP bus data bit 7                                      |

| TUDX2 MAP<br>DOUTL[6] | 0   | A35       | DROP bus data bit 6                                      |

| TUDX2 MAP<br>DOUTL[5] | 0   | A37       | DROP bus data bit 5                                      |

| TUDX2 MAP<br>DOUTL[4] | 0   | A39       | DROP bus data bit 4                                      |

#### ISSUE 2

#### SONET/SDH 155Mbit/s ADM Reference Design

| TUDX2 MAP<br>DOUTL[3] | 0 | A41               | DROP bus data bit 3                         |  |

|-----------------------|---|-------------------|---------------------------------------------|--|

| TUDX2 MAP<br>DOUTL[2] | 0 | A43               | DROP bus data bit 2                         |  |

| TUDX2 MAP<br>DOUTL[1] | 0 | A45               | DROP bus data bit 1                         |  |

| TUDX2 MAP<br>DOUTL[0] | 0 | A47               | DROP bus data bit 0                         |  |

| MAP TUDX2<br>DINB[8]  | I | A38               | ADD bus data parity signal                  |  |

| MAP TUDX2<br>DINB[7]  | I | A67               | ADD bus data bit 7                          |  |

| MAP TUDX2<br>DINB[6]  | I | A65               | ADD bus data bit 6                          |  |

| MAP TUDX2<br>DINB[5]  | I | A63               | ADD bus data bit 5                          |  |

| MAP TUDX2<br>DINB[4]  | I | A61               | ADD bus data bit 4                          |  |

| MAP TUDX2<br>DINB[3]  | I | A59               | ADD bus data bit 3                          |  |

| MAP TUDX2<br>DINB[2]  | I | A57               | ADD bus data bit 2                          |  |

| MAP TUDX2<br>DINB[1]  | I | A55               | ADD bus data bit 1                          |  |

| MAP TUDX2<br>DINB[0]  | I | A53               | ADD bus data bit 0                          |  |

| TC OC1J1              | 0 | A46               | ADD bus C1, J1 frame signal                 |  |

| TC APL                | 0 | A48               | ADD data payload signal                     |  |

| TC AC1J1V1            | 0 | A50               | ADD data C1, J1, V1 frame synchronization   |  |

| TUPP POHEN<br>[3:1]   | 0 | A3<br>A5<br>A7    | Tributary path overhead enable signals      |  |

| TUPP POHFP<br>[3:1]   | 0 | A9<br>A11<br>A13  | Tributary path overhead frame pulse signals |  |

| TUPP POH<br>[3:1]     | 0 | A15<br>A17<br>A19 | Tributary path overhead signals             |  |

| TUPP RAD              | 0 | A21               | Receive alarm port                          |  |

| TUPP POHCK            | 0 | A23               | Tributary path overhead enable signals      |  |

#### ISSUE 2

#### SONET/SDH 155Mbit/s ADM Reference Design

| n                          |     |                                                                                  | 1                                   |

|----------------------------|-----|----------------------------------------------------------------------------------|-------------------------------------|

| MC MAP<br>RSTB[3:1]        | 0   | A66<br>A64<br>A62                                                                | H/W reset bits                      |

| MC MAP<br>CONTROL<br>[3:1] | 0   | A60<br>A58<br>A56                                                                | Reserved for mapper control signals |

| MC MAP CSB                 | 0   | A70                                                                              | Chip select signal                  |

| ALE                        | 0   | A90                                                                              | Address latch enable                |

| WRB                        | 0   | A87                                                                              | write strobe signal                 |

| RDB                        | 0   | A89                                                                              | read enable signal                  |

| D[7:0]                     | I/O | A88<br>A86<br>A84<br>A82<br>A80<br>A78<br>A76<br>A74                             | Data bus                            |

| A[11:0]                    | Ο   | A92<br>A94<br>A93<br>A91<br>A85<br>A83<br>A81<br>A79<br>A77<br>A75<br>A73<br>A71 | Address bus                         |

| INTB                       | I   | A69                                                                              | Interrupt signal from mapper side   |

| SPARE1                     | 0   | A42                                                                              | Reserved for future use             |

| SPARE2                     | 0   | A52                                                                              | Reserved for future use             |

| VCC                        | 0   | A6<br>A8<br>A95<br>A96                                                           | +5 v power                          |

| GND                        |     | A1<br>A2<br>A97<br>A98<br>A99<br>A100                                            | Ground                              |

SONET/SDH 155Mbit/s ADM Reference Design

# STXC and TUPP-Plus Status LED Display

| LED D2 | From           | Signal | Description                                 |

|--------|----------------|--------|---------------------------------------------|

| LED1   | STXC           | OOF    | Out of frame indicator                      |

| LED2   | STXC           | LOS    | Loss of signal indicator                    |

| LED3   | STXC           | LAIS   | Line alarm indication signal indicator      |

| LED4   | STXC           | FERF   | Far end receive failure indicator           |

| LED5   | STXC           | LOF    | Loss of frame indicator                     |

| LED6   | TUPP -<br>Plus | AIS    | Tributary alarm indication signal indicator |

| LED7   | TUPP -<br>Plus | IDLE   | Tributary idle indicator                    |

| LED8   | TUPP -<br>Plus | LOM[1] | Loss of multiframe indicator                |

| LED9   | TUPP -<br>Plus | LOM[2] | Loss of multiframe indicator                |

| LED10  | TUPP -<br>Plus | LOM[3] | Loss of multiframe indicator                |

# SPTX status LED Display

| LED D3 | From | Signal   | Description                               |

|--------|------|----------|-------------------------------------------|

| LED1   | SPTX | LOP[1]   | Loss of pointer indicator                 |

| LED2   | SPTX | LOP[2]   | Loss of pointer indicator                 |

| LED3   | SPTX | LOP[3]   | Loss of pointer indicator                 |

| LED4   | SPTX | PAIS[1]  | Path alarm indication signal<br>indicator |

| LED5   | SPTX | PAIS[2]  | Path alarm indication signal<br>indicator |

| LED6   | SPTX | PAIS[3]  | Path alarm indication signal<br>indicator |

| LED7   | SPTX | PFERF[1] | Path far end receive failure<br>indicator |

| LED8   | SPTX | PFERF[2] | Path far end receive failure<br>indicator |

| LED9   | SPTX | PFERF[3] | Path far end receive failure<br>indicator |