Pulse (Repertory) Dialer CMOS LSI

T-75-07-07

# LR4173 Pulse (Repertory) Dialer CMOS LSI

## Description

The LR4173 is a CMOS LSI for the repertory dialer with ten 16-digit number memory storage. The pulse and mute signal outputs resulting from keyboard input are like those of a pulse dialer. The LR4173 incorporates a 64×10 bit RAM which is used to store the ten telephone numbers.

When used in a Public Branch Exchange (PBX) system, a Pause function is provided. This function suspends dial pulse output upon pause detection (via # key input), and resumes the output after one of the numeric keys is pressed.

#### **Features**

- 1. Make ratio: 30/40% pin-selectable

- 2. Pulse output: "0" true

- 3. Mute output: "0" true

- 4. Stores ten 16-digit telephone numbers

- 5. One temporary memory and permanent memory storage of telephone numbers are possible

- 6. Uses a CR oscillator as a frequency reference

- 7. Line operation Off-Hook, battery operation On-Hook

- 8. Uses either a standard 2-of-7 matrix keyboard or a single contact keyboard

- 9. PBX pause storage

- 10. 16-pin dual-in-line-package

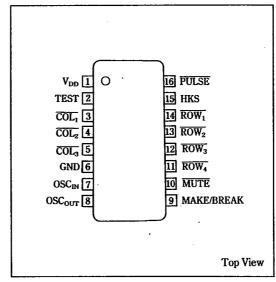

#### **Pin Connections**

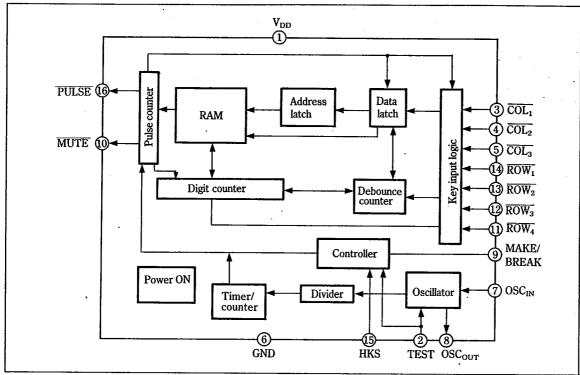

## **Block Diagram**

T-75-07-07

## **Absolute Maximum Ratings**

| <del></del>             | •                |             |      |      |

|-------------------------|------------------|-------------|------|------|

| Parameter               | Symbol           | Rating      | Unit | Note |

| Supply voltage          | $V_{DD}$         | 6.2         | V    | 1    |

| Operating temperature   | Topr             | -30 to +60  | °C   |      |

| Storage temperature     | T <sub>stg</sub> | -55 to +150 | °C   |      |

| Power dissipation       | P <sub>D</sub>   | . 500       | mW   | 2    |

| Maximum pin voltage (1) | V <sub>IN1</sub> | -0.3        | V    | 3    |

| Maximum pin voltage (2) | V <sub>IN2</sub> | +0.3        | V    | 4    |

Note 1: Referenced to GND.

Note 2: Ta=25°C.

Note 3: The maximum applicable voltage on any pin with respect to GND.

Note 4: The maximum applicable voltage on any pin with respect to  $V_{DD}$ .

## **Recommended Operating Conditions**

| Parameter      | Unit            | Rating     | Unit |  |  |  |  |  |

|----------------|-----------------|------------|------|--|--|--|--|--|

| Supply voltage | V <sub>DD</sub> | 2.5 to 6.0 | V    |  |  |  |  |  |

5.0

(-30°C≦Ta≦60°C)

T-75-07-07

kΩ

kΩ

3

## **DC** Characteristics

| Parameter                   | Symbol           | Conditions                                    | MIN.                 | TYP.  | MAX.                 | Unit | Note |

|-----------------------------|------------------|-----------------------------------------------|----------------------|-------|----------------------|------|------|

| Standby current             | I <sub>SB</sub>  | V <sub>DD</sub> =2.5V                         |                      | 1.0   | 5.0                  | μA   | 1    |

| Operating current           | I <sub>OP</sub>  | V <sub>DD</sub> =2.5V                         |                      | 100   | 200                  | μΑ   | 2    |

| MUTE sink current           | I <sub>ML</sub>  | $V_{DD}=2.5V, V_{o}=0.5V$                     | 0.5                  | 2.0   |                      | mA   |      |

| Pulse sink current          | I <sub>PL</sub>  | V <sub>DD</sub> =2.5V, V <sub>o</sub> =0.5V   | 1.0                  | 4.0   |                      | mA   |      |

| MUTE, pulse leakage current | I <sub>LKG</sub> | $V_{DD} = 6.0 \text{V}, \ V_o = 6.0 \text{V}$ |                      | 0.001 | 1.0                  | μA   |      |

| Key contact resistance      | RK <sub>1</sub>  | •                                             |                      |       | 1.0                  | kΩ   |      |

| Keyboard capacitance        | CK <sub>1</sub>  |                                               |                      |       | 3.0                  | pF   |      |

| "0" logic level             | V <sub>IL</sub>  |                                               | GND                  |       | $0.2V_{\mathrm{DD}}$ | V    |      |

| "1" logic level             | V <sub>IH</sub>  |                                               | $0.8V_{\mathrm{DD}}$ |       | $V_{DD}$             | V    |      |

$K_{RU}$

$K_{RD}$

Note 1: All output pins in no-load condition when clock is stopped in Off-Hook mode.

Note 2: All output pins in no-load condition during key input, in either On-Hook or Off-Hook Mode.

Note 3: Resistance when ROW and COL pins are scanned at 125 Hz and at high or low level.

$V_{DD}=4.0V$

$V_{DD}=4.0V$

## **AC Characteristics**

Key pull-up resistance

Key pull-down resistance

| Parameter                | Symbol           | Conditions            | MIN. | TYP. | MAX. | Unit | Note |

|--------------------------|------------------|-----------------------|------|------|------|------|------|

| Oscillator frequency     | fosc             |                       |      | 480  |      | kHz  | 1    |

| Key debounce time        | t <sub>DB</sub>  | •                     | -    | 32   | -    | ms   | 2, 3 |

| Oscillator start-up time | tos              |                       |      |      | 8.0  | ms   |      |

| Pulse rate               | P <sub>R</sub>   |                       |      | 10.0 |      | pps  | 3    |

| Break time               |                  | Pin 9=V <sub>DD</sub> |      | 60   |      | ms   | 3    |

|                          | t <sub>B</sub>   | Pin 9=GND             |      | 68   |      | ms   |      |

| Inter digital pause time | t <sub>IDP</sub> | -                     |      | 840  |      | ms   | 3    |

| Mute overlap time        | t <sub>MOL</sub> |                       |      | 2    |      | ms   | 3    |

Note 1: Use elements with the following characteristics as the ceramic oscillator.  $R < 20\Omega$ ,  $RA \ge 70k\Omega$ ,  $C_0 \le 500pF$ . Note 2: Key input is accepted if it is valid 32msec after the start of oscillation. Note 3: Changes in proportion to the frequency of the oscillator.

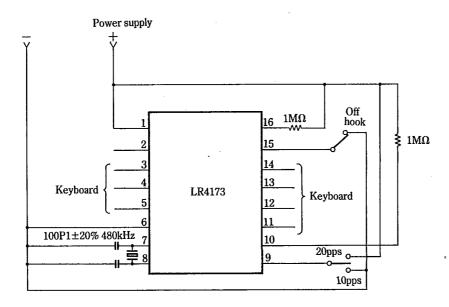

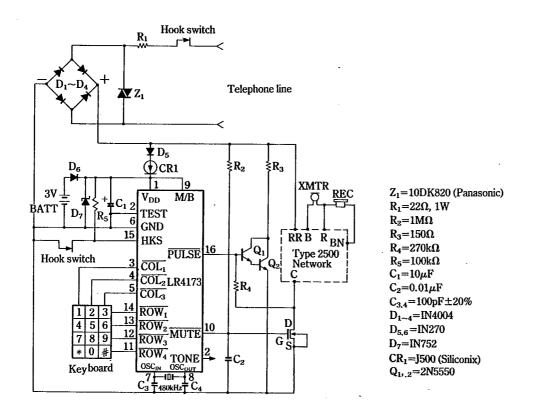

## **Test Circuit**

LR4173

T-75-07-07

### Pin Description

## V<sub>DD</sub> (Pin 1)

The  $V_{DD}$  pin is the positive power supply pin with respect to the GND pin. Maximum input voltage is 6.0 volts.

## Test Input (Pin 2)

The test input pin is used to test the device. It should be connected to GND.

## Keyboard Inputs (Pins 3, 4, 5, 11, 12, 13, 14)

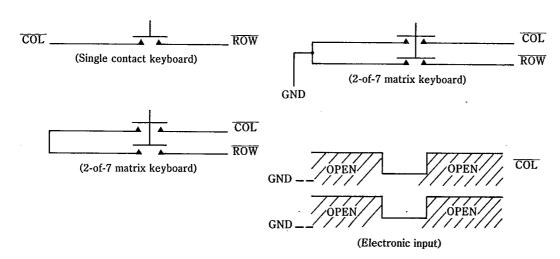

The key entry is defined by either a single ROW being connected to a single COLUMN, or GND level being simultaneously applied to both a ROW and a COLUMN. Consequently, either a single contact or a standard 2-of-7 keyboard with GND common can be used. Fig. 1 shows the possible keyboard configurations.

The LR4173 keyboard input pins are totally static until a valid key input is sensed. The oscillator is then enabled and the rows and columns are alternately scanned (pulled high, then low) to verify that the input is valid. Keyboard bounce is ignored for 32ms after the initial key down is detected. A key input is accepted if it is valid after this initial debounce time. This scheme allows any valid key input to be recognized within 40ms of the initial key closure.

#### GND (Pin 6)

Negative power supply pin.

#### Oscillator (Pins 7 and 8)

The oscillator is formed by using a 480kHz ceramic resonator and two capacitors, as shown in the System Configuration diagram.

#### Make/Break Select (Pin 9)

The Make/Break ratio may be selected by connecting this pin to either  $V_{DD}$  or GND. Table 1 indicates the two popular ratios from which the user can choose.

Table 1

| Level of Pin 9          | MAKE | BREAK |

|-------------------------|------|-------|

| V <sub>DD</sub> (Pin 1) | 40%  | 60%   |

| GND (Pin 6)             | 32%  | 68%   |

#### Mute Output (Pin 10)

Pin 10 is the output of an open-drain N-channel transistor. It provides the logic necessary to mute the network while the telephone line is being pulsed.

#### Hook Switch Input (Pin 15)

The Hook Switch input pin requires an external pull-up resistor to the positive supply. A  $V_{DD}$  input puts the circuit into On-Hook mode, while a GND input puts it into Off-Hook or dialing mode.

#### Pulse Output (Pin 16)

The Pulse Output pin is an N-channel open-drain output for driving an external transistor. This external transistor is used to switch the loop current in a telephone line.

Fig. 1 Keyboard configurations

## Functional Description

#### **Dialed Number Memory**

During normal dialing, each digit is stored in the LND (Last Number Dialed) buffer, location 0. The telephone number dialed can be left in this temporary LND buffer for later use or it can be copied into any of the other nine permanent memory loca-

Telephone numbers to be automatically dialed by the LR4173 may be entered into the LND buffer while either On-Hook or Off-Hook.

However, the LR4173 must be in On-Hook mode for a number to be copied into a permanent memory location. A number may be copied and stored by entering the key sequence \* \*  $\mathbb{N}$  (N=1-9), followed by the address (1-9) of the memory location into which the number is to be stored. This operation requires 300ms before going Off-Hook or reinitiating the store function. Information present in the LND buffer is replaced when new data is entered and cannot be recalled.

#### **Automatic Dialing**

The automatic dialing function is implemented by going Off-Hook and entering a \* N (N=1-9), followed by the address (1-9) of the desired telephone number. Dialing will begin with the valid entry of the address key, and can be interrupted by initiating a new redial command. The LND buffer will contain the information last entered. A key sequence of \* 0 will cause the last number entered to be redialed.

Normal dialing is performed when telephone numbers are input in the Off-Hook mode.

#### **Pause Continue Command**

The LR4173 permits pauses to be programmed within the 1-15 digits of the telephone number. This pause is input and stored in memory with the # key. If a pause code is detected during automatic dialing, the dialing operation is suspended. Any key except the \* key is used to dial in data after the pause, once the inter digital-pause time passes (CONTINUE command).

#### Normal dialing

Normal diling is performed when telephone numbers are input in Off-Hook mode.

## Sample operation

#### (Example 1)

- 1. On-Hook

- 2. Input "621-1221"

- 3. Input "\*\*5"

- 4. Off-Hook

- 5. Input "\*\*5"

"621-1221" is written into the memory buffer "621-1221" is stored in location 5.

"621-1221 is automatically dialed.

# (Example 2)

- 1. Off-Hook

- 2. Input PBX access code "42".

- 3. While waiting for dial tone, enter "#"

- "1-234-621-4. Dial 1221"

- 5. On-Hook.

- 6. Input "\*\*3"

- 7. Off-Hook

- 8. Input "\*3"

- 9. Enter "3" (Continue Command) while waiting for a dial tone.

"42" is written into memory and dialed.

"#" is written into memory.

The number is written into memory and dialed.

"42 #1-234-621-1221" is transmitted to location 3.

"42" is dialed, then a pause occurs.

"1-234-621-1221" is dialed.

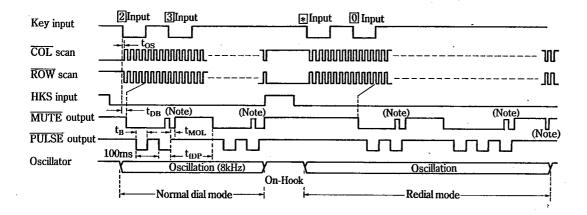

## Timing Diagram

T-75-07-07

Note 1: When PULSE output stops, 250µs-wide pulses are generated, and when redial stops, 2ms-wide mute endpulses are generated in the MUTE output singal.

## System Configuration Example

4