September 1991 Revised November 1999

# 100315 Low Skew Quad Clock Driver

## FAIRCHILD

SEMICONDUCTOR

# 100315 Low Skew Quad Clock Driver

### **General Description**

The 100315 contains four low skew differential drivers, designed for generation of multiple, minimum skew differential clocks from a single differential input. This device also has the capability to select a secondary single-ended clock source for use in lower frequency system level testing. The 100315 is a 300 Series redesign of the 100115 clock driver.

### Features

- Low output-to-output skew (≤50 ps)

- Differential inputs and outputs

- Secondary clock available for system level testing

- 2000V ESD protection

- Voltage compensated operating range: -4.2V to -5.7V

### **Ordering Code:**

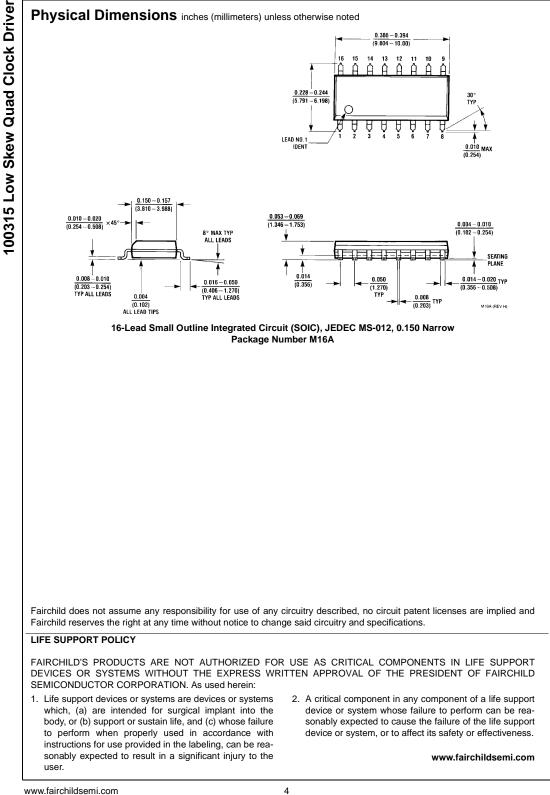

| Order Number                                                                                              | Package Number | Package Descriptions                                                        |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------|----------------|-----------------------------------------------------------------------------|--|--|--|--|

| 100315SC                                                                                                  | M16A           | 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow |  |  |  |  |

| Devices also available in Tape and Reel. Specify by appending the suffix letter "X" to the ordering code. |                |                                                                             |  |  |  |  |

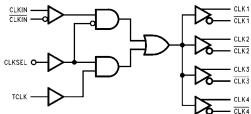

### Logic Diagram

### **Connection Diagram**

|                    |   | $\nabla$ |    |                   |

|--------------------|---|----------|----|-------------------|

| CLKIN -            | 1 | 0        | 16 | CLKIN             |

| V <sub>EE</sub> —  | 2 |          | 15 | - V <sub>EE</sub> |

| CLK1               | 3 |          | 14 | CLK4              |

| CLK1               | 4 |          | 13 | - CLK4            |

| CLK2               | 5 |          | 12 | -CLK3             |

| CLK2               | 6 |          | 11 | — CLK3            |

| V <sub>CCA</sub> - | 7 |          | 10 | −v <sub>cc</sub>  |

| ТСЦК —             | 8 |          | 9  | - CLKSEL          |

|                    |   |          |    |                   |

### **Pin Descriptions**

| Pin Names                                              | Description                 |  |  |  |  |

|--------------------------------------------------------|-----------------------------|--|--|--|--|

| CLKIN, CLKIN                                           | Differential Clock Inputs   |  |  |  |  |

| $CLK_{1-4}, \overline{CLK}_{1-4}$                      | Differential Clock Outputs  |  |  |  |  |

| CLK <sub>1–4</sub> , <u>CLK</u> <sub>1–4</sub><br>TCLK | Test Clock Input (Note 1)   |  |  |  |  |

| CLKSEL                                                 | Clock Input Select (Note 1) |  |  |  |  |

Note 1: TCLK and CLKSEL are single-ended inputs, with internal 50  $\mbox{k}\Omega$  pull-down resistors.

### **Truth Table**

| CLKSEL | CLKIN | CLKIN | TCLK | CLKn | CLKn |

|--------|-------|-------|------|------|------|

| L      | L     | Н     | Х    | L    | Н    |

| L      | н     | L     | Х    | н    | L    |

| н      | Х     | Х     | L    | L    | н    |

| н      | Х     | Х     | н    | н    | L    |

L = LOW Voltage Level H = HIGH Voltage Level

X = Don't Care

100315

### Absolute Maximum Ratings(Note 2)

| Storage Temperature                            | $-65^{\circ}C$ to $+150^{\circ}C$ |

|------------------------------------------------|-----------------------------------|

| Maximum Junction Temperature (T <sub>J</sub> ) | +150°C                            |

| Case Temperature under Bias $(T_C)$            | 0°C to +85°C                      |

| V <sub>EE</sub> Pin Potential to Ground Pin    | -7.0V to +0.5V                    |

| Input Voltage (DC)                             | V <sub>CC</sub> to +0.5V          |

| Output Current (DC Output HIGH)                | –50 mA                            |

| Operating Range (Note 2)                       | -5.7V to -4.2V                    |

| ESD (Note 3)                                   | ≥2000V                            |

|                                                |                                   |

# Recommended Operating Conditions

Case Temperature ( $T_C$ ) Supply Voltage ( $V_{EE}$ ) 0°C to +85°C -5.7V to -4.2V

Note 2: The "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the absolute maximum rating. The "Recommended Operating Conditions" table will define the conditions for actual device operation.

Note 3: ESD testing conforms to MIL-STD-883, Method 3015.

### DC Electrical Characteristics (Note 4)

$V_{EE}=-4.2V$  to  $-5.7V,~V_{CC}=V_{CCA}=GND,~T_{C}=0^{\circ}C$  to  $+85^{\circ}C$

| Symbol            | Parameter                       | Min           | Тур   | Max             | Units | Conditions                                          |  |  |

|-------------------|---------------------------------|---------------|-------|-----------------|-------|-----------------------------------------------------|--|--|

| V <sub>OH</sub>   | Output HIGH Voltage             | -1025         | -955  | -870            | mV    | V <sub>IN</sub> = V <sub>IH(Max)</sub> Loading with |  |  |

| V <sub>OL</sub>   | Output LOW Voltage              | -1830         | -1705 | -1620           |       | or $V_{IL(Min)}$ 50 $\Omega$ to -2.0                |  |  |

| V <sub>онс</sub>  | Output HIGH Voltage             | -1035         |       |                 | mV    | $V_{IN} = V_{IH(Min)}$ Loading with                 |  |  |

| V <sub>OLC</sub>  | Output LOW Voltage              |               |       | -1610           |       | or $V_{IL(Max)}$ 50 $\Omega$ to -2.0                |  |  |

| V <sub>IH</sub>   | Single-Ended Input HIGH Voltage | -1165         |       | -870            | mV    | Guaranteed HIGH Signal for All Inputs               |  |  |

| V <sub>IL</sub>   | Single-Ended Input LOW Voltage  | -1830         |       | -1475           | mV    | Guaranteed LOW Signal for All Inputs                |  |  |

| IIL               | Input LOW Current               | 0.50          |       |                 | μA    | $V_{IN} = V_{IL(Min)}$                              |  |  |

| IIH               | Input HIGH Current              |               |       |                 |       |                                                     |  |  |

|                   | CLKIN, CLKIN                    |               |       | 150             | μΑ    |                                                     |  |  |

|                   | TCLK                            |               |       | 250             | μΑ    | $V_{IN} = V_{IH(Max)}$                              |  |  |

|                   | CLKSEL                          |               |       | 250             | μΑ    |                                                     |  |  |

| V <sub>DIFF</sub> | Input Voltage Differential      | 150           |       |                 | mV    | Required for Full Output Swing                      |  |  |

| V <sub>CM</sub>   | Common Mode Voltage             | $V_{CC} - 2V$ |       | $V_{CC} - 0.5V$ | V     |                                                     |  |  |

| I <sub>CBO</sub>  | Input Leakage Current           | -10           |       |                 | μA    | $V_{IN} = V_{EE}$                                   |  |  |

| I <sub>EE</sub>   | Power Supply Current            | -67           |       | -35             | mA    |                                                     |  |  |

Note 4: The specified limits represent the "worst case" value for the parameter. Since these "worst case" values normally occur at the temperature extrer additional noise immunity and guard banding can be achieved by decreasing the allowable system operating ranges.

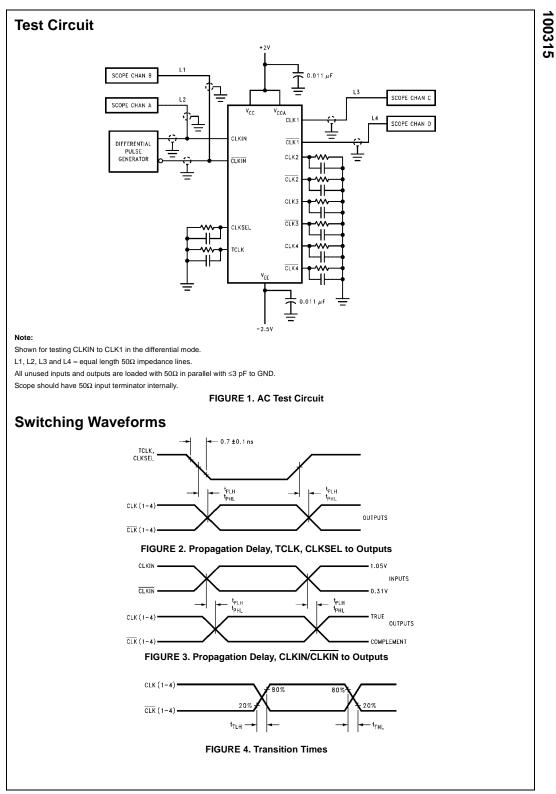

### **AC Electrical Characteristics**

| $V_{EE} = -4.2V$ to $-4.8$ , | $V_{CC} = V_{CCA} = GND$ |

|------------------------------|--------------------------|

| · EE                         | ·UL ·ULA OND             |

| Symbol           | Parameter .                                    | $\mathbf{T}_{\mathbf{C}} = 0^{\circ}\mathbf{C}$ |      | $T_C = +25^{\circ}C$ |      | T <sub>C</sub> = +85°C |      | Units | Conditions   |

|------------------|------------------------------------------------|-------------------------------------------------|------|----------------------|------|------------------------|------|-------|--------------|

|                  |                                                | Min                                             | Max  | Min                  | Max  | Min                    | Max  | 0     | Conditions   |

| f <sub>MAX</sub> | Maximum Clock Frequency                        | 750                                             |      | 750                  |      | 750                    |      | MHz   |              |

| t <sub>PLH</sub> | Propagation Delay CLKIN,                       |                                                 |      |                      |      |                        |      |       |              |

| t <sub>PHL</sub> | CLKIN to CLK(1-4), CLK(1-4)                    |                                                 |      |                      |      |                        |      |       | Figures 1, 3 |

|                  | Differential                                   | 0.59                                            | 0.79 | 0.62                 | 0.82 | 0.67                   | 0.87 | ns    |              |

|                  | Single-Ended                                   | 0.59                                            | 0.99 | 0.62                 | 1.02 | 0.67                   | 1.07 |       |              |

| t <sub>PLH</sub> | Propagation Delay, TCLK                        | 0.50                                            | 1.20 | 0.50                 | 1.20 | 0.50                   | 1.20 | ns    | Figures 1, 2 |

| t <sub>PHL</sub> | to CLK <sub>(1-4)</sub> , CLK <sub>(1-4)</sub> | 0.50                                            | 1.20 | 0.50                 | 1.20 | 0.50                   | 1.20 | 115   | Figures 1, 2 |

| t <sub>PLH</sub> | Propagation Delay, CLKSEL                      | 0.80                                            | 1.60 | 0.80                 | 1.60 | 0.80                   | 1.60 | ns    | Figures 1, 2 |

| t <sub>PHL</sub> | to CLK(1-4), CLK(1-4)                          | 0.00                                            | 1.00 | 0.00                 | 1.00 | 0.00                   | 1.00 | 115   | rigules 1, 2 |

| t <sub>TLH</sub> | Transition Time                                | 0.30                                            | 0.80 | 0.30                 | 0.80 | 0.30                   | 0.80 | ns    | Figures 1, 4 |

| t <sub>THL</sub> | 20% to 80%, 80% to 20%                         | 0.30                                            | 0.60 | 0.30                 | 0.60 | 0.30                   | 0.60 | 115   | Figures 1, 4 |

| t <sub>OST</sub> | Maximum Skew Opposite Edge                     |                                                 |      |                      |      |                        |      |       |              |

| DIFF             | Output-to-Output Variation                     |                                                 | 50   |                      | 50   |                        | 50   | ps    | (Note 5)     |

|                  | Data to Output Path                            |                                                 |      |                      |      |                        |      |       |              |

Note 5: Output-to-Output Skew is defined as the absolute value of the difference between the actual propagation delay for any outputs within the same packaged device. The specifications apply to any outputs switching in the same direction either HIGH-to-LOW ( $t_{OSHL}$ ), or LOW-to-HIGH ( $t_{OSLH}$ ), or in opposite directions both HL and LH ( $t_{OST}$ ). Parameters  $t_{OST}$  and  $t_{PS}$  guaranteed by design.

www.fairchildsemi.com

This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.