## 3-PHASE BRUSHLESS DC MOTOR CONTROLLER/DRIVER WITH BACK-EMF SENSING

#### ABSOLUTE MAXIMUM RATINGS at T<sub>A</sub> = +25°C

Load Supply Voltage, V<sub>BB</sub> . . . . . 14 V Output Current,  $I_{OUT}$ .....  $\pm 1.25$  A Logic Supply Voltage,  $V_{DD}$  . . . . 6.0  $\underline{V}$ Logic Input Voltage Range,

$V_{IN}$  ..... -0.3 V to  $V_{DD}$  + 0.3 V

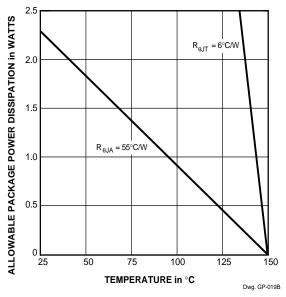

Package Power Dissipation,

See Graph  $P_D$  . . . . . . . . . . . . . . . . Operating Temperature Range,

Junction Temperature, T<sub>J</sub> . . . +150°C† Storage Temperature Range,

$T_S \dots -55^{\circ}C \text{ to } +150^{\circ}C$

† Fault conditions that produce excessive junction temperature will activate device thermal shutdown circuitry. These conditions can be tolerated, but should be avoided.

Output current rating may be restricted to a value determined by system concerns and factors. These include: system duty cycle and timing, ambient temperature, and use of any heatsinking and/or forced cooling. For reliable operation, the specified maximum junction temperature should not be exceeded.

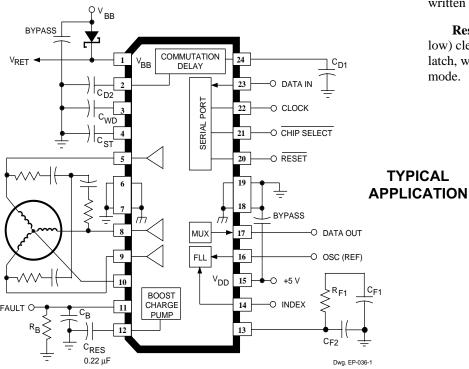

The A8905CLB isw a three-phase brushless dc motor controller/ driver for use with CD-ROM or DVD drives. The three half-bridge outputs are low on-resistance n-channel DMOS devices capable of driving up to 1.25 A. The A8905CLB provides complete, reliable, self-contained back-EMF sensing motor startup and running algorithms. A programmable digital frequency-locked loop speed control circuit together with the linear current control circuitry provides precise motor speed regulation.

A serial port allows the user to program various features and modes of operation, such as the speed control parameters, startup current limit, sleep mode, diagnostic modes, and others.

#### **APPLICATIONS**

- CD-ROMs

- DVDs

#### **FEATURES**

- DMOS Outputs

- $\blacksquare$  Low  $r_{DS(on)}$

- Startup Commutation Circuitry

- Back-EMF Commutation Circuitry

- Serial Port Interface

- Frequency-Locked Loop Speed Control

- Tachometer Signal Input

- Programmable Start-Up Current

- Diagnostics Mode

- Sleep Mode

- Linear Current Control

- Internal Current Sensing

- Dynamic Braking Through Serial Port

- Power-Down Dynamic Braking

- System Diagnostics Data Out

- Data Out Ported in Real Time

- Internal Thermal Shutdown Circuitry

Always order by complete part number, e.g., **A8905CLB**.

# ELECTRICAL CHARACTERISTICS at $T_A = +25^{\circ}C$ , $V_{DD} = 5.0 \text{ V}$

|                                 |                      |                                                                             |      | Limits |      |       |

|---------------------------------|----------------------|-----------------------------------------------------------------------------|------|--------|------|-------|

| Characteristic                  | Symbol               | Test Conditions                                                             | Min. | Тур.   | Max. | Units |

| Logic Supply Voltage            | $V_{DD}$             | Operating                                                                   | 4.5  | 5.0    | 5.5  | V     |

| Logic Supply Current            | I <sub>DD</sub>      | Operating                                                                   | _    | 7.5    | 10   | mA    |

|                                 |                      | Sleep Mode                                                                  | _    | _      | 1.5  | mA    |

| Load Supply Voltage             | $V_{BB}$             | Operating                                                                   | 4.5  | _      | 14   | V     |

| Thermal Shutdown                | T <sub>J</sub>       |                                                                             |      | 165    | _    | °C    |

| Thermal Shutdown Hys.           | $\DeltaT_J$          |                                                                             | _    | 20     | _    | °C    |

| Output Drivers                  |                      |                                                                             |      |        |      |       |

| Output Leakage Current          | I <sub>DSX</sub>     | V <sub>BB</sub> = 14 V, V <sub>OUT</sub> = 14 V                             | _    | 1.0    | 300  | μА    |

|                                 |                      | V <sub>BB</sub> = 14 V, V <sub>OUT</sub> = 0 V                              | _    | -1.0   | -300 | μΑ    |

| Total Output ON Resistance      | r <sub>DS(on)</sub>  | I <sub>OUT</sub> = 600 MA                                                   | _    | 1.1    | 1.4  | Ω     |

| Output Sustaining Voltage       | V <sub>DS(sus)</sub> | V <sub>BB</sub> = 14 V, I <sub>OUT</sub> = I <sub>OUT</sub> (MAX), L = 3 mH | 14   | _      | _    | V     |

| Clamp Diode Forward Voltage     | V <sub>F</sub>       | I <sub>F</sub> = 1.0 A                                                      | _    | 1.25   | 1.5  | V     |

| Control Logic                   |                      |                                                                             |      |        |      |       |

| Logic Input Voltage             | V <sub>IN(0)</sub>   | INDEX, RESET, CLK,                                                          | -0.3 | _      | 1.5  | V     |

|                                 | V <sub>IN(1)</sub>   | CHIP SELECT, OSC, BRAKE                                                     | 3.5  | _      | 5.3  | V     |

| Logic Input Current             | I <sub>IN(0)</sub>   | V <sub>IN</sub> = 0 V                                                       | _    | _      | -0.5 | μΑ    |

|                                 | I <sub>IN(1)</sub>   | V <sub>IN</sub> = 5.0 V                                                     | _    | _      | 1.0  | μΑ    |

| DATA Output Voltage             | V <sub>OUT(0)</sub>  | I <sub>OUT</sub> = 500 μA                                                   |      | _      | 1.5  | V     |

|                                 | V <sub>OUT(1)</sub>  | I <sub>OUT</sub> = -500 μA                                                  | 3.5  | _      | _    | V     |

| C <sub>ST</sub> Current         | I <sub>CST</sub>     | Charging                                                                    | 14   | 20     | 28   | μА    |

|                                 |                      | Discharging                                                                 | -14  | -20    | -28  | μΑ    |

| C <sub>ST</sub> Threshold       | V <sub>CSTH</sub>    |                                                                             | 2.1  | 2.5    | 2.9  | V     |

|                                 | V <sub>CSTL</sub>    |                                                                             | _    | 500    | _    | mV    |

| Filter Current                  | I <sub>FILTER</sub>  | Charging                                                                    | 7.0  | 10     | 15   | μА    |

|                                 |                      | Discharging                                                                 | -7.0 | -10    | -15  | μΑ    |

|                                 |                      | Leakage, V <sub>FILTER</sub> = 2.5 V                                        | _    | 5.0    | _    | nA    |

| C <sub>D</sub> Current          | I <sub>CD</sub>      | Charging                                                                    | 14   | 22     | 28   | μΑ    |

|                                 |                      | Discharging                                                                 | -26  | -35    | -66  | μΑ    |

| C <sub>D</sub> Current Matching | _                    | I <sub>CD(DISCHRG)</sub> /I <sub>CD(CHRG)</sub>                             | 1.7  | 2.2    | 2.3  | _     |

| C <sub>D</sub> Threshold        | $V_{CD}$             |                                                                             | _    | 2.5    | _    | V     |

| C <sub>WD</sub> Current         | I <sub>CWD</sub>     | Charging                                                                    | 14   | 22     | 28   | μΑ    |

Continued next page ...

#### **ELECTRICAL CHARACTERISTICS continued**

|                                   |                  |                                                |      | Lin  | nits |       |

|-----------------------------------|------------------|------------------------------------------------|------|------|------|-------|

| Characteristic                    | Symbol           | Test Conditions                                | Min. | Тур. | Max. | Units |

| C <sub>WD</sub> Threshold Voltage | V <sub>TL</sub>  |                                                | 0.80 | 0.85 | 0.95 | V     |

|                                   | $V_{TH}$         |                                                | 2.4  | 2.75 | 3.0  | V     |

| Max. FLL Oscillator Frequency     | f <sub>OSC</sub> | V <sub>DD</sub> = 5.1 V, T <sub>A</sub> = 25°C | 20   | _    | _    | MHz   |

|                                   |                  | V <sub>DD</sub> = 4.5 V, T <sub>A</sub> = 70°C | _    | 10   | _    | MHz   |

| I <sub>OUT</sub> (MAX) Accuracy   | _                | I <sub>OUT</sub> = 1 A                         | _    | ±20  | _    | %     |

| BRAKE Threshold                   | $V_{BRK}$        |                                                | 1.4  | 1.7  | 2.0  | V     |

| Transconductance Gain             | g <sub>m</sub>   |                                                | 0.26 | 0.35 | 0.50 | A/V   |

| Centertap Resistors               | R <sub>CT</sub>  |                                                | 5.0  | 10   | 13   | kΩ    |

| Back-EMF Hysteresis               | _                | V <sub>BEMF</sub> - V <sub>CTAP</sub> at       | 15   | 25   | 40   | mV    |

|                                   |                  | FCOM Transition                                | -15  | -25  | -40  | mV    |

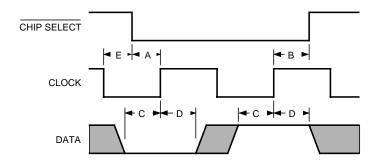

#### **SERIAL PORT TIMING CONDITIONS**

Dwg. WP-019

| A. | $\label{thm:minimum} \mbox{Minimum CHIP SELECT setup time before CLOCK rising edge } \ldots$ | 100 ns  |

|----|----------------------------------------------------------------------------------------------|---------|

| B. | Minimum CHIP SELECT hold time after CLOCK rising edge                                        | 150 ns  |

| C. | Minimum DATA setup time before CLOCK rising edge                                             | 150 ns  |

| D. | Minimum DATA hold time after CLOCK rising edge                                               | 150 ns  |

| E. | Minimum CLOCK low time before CHIP SELECT                                                    | . 50 ns |

| F. | Maximum CLOCK frequency                                                                      | 3 MHz   |

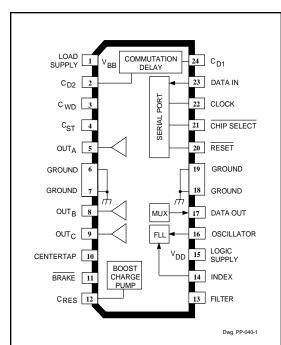

#### **TERMINAL FUNCTIONS**

| Term. | Terminal Name    | Function                                                                                                                                                                                                       |

|-------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | LOAD SUPPLY      | V <sub>BB</sub> ; the 5 V or 12 V motor supply.                                                                                                                                                                |

| 2     | C <sub>D2</sub>  | One of two capacitors used to generate the ideal commutation points from the back-EMF zero-crossing points.                                                                                                    |

| 3     | C <sub>WD</sub>  | Timing capacitor used by the watchdog circuit to disable the back-EMF comparators during commutation transients, and to detect incorrect motor position.                                                       |

| 4     | C <sub>ST</sub>  | Startup oscillator timing capacitor.                                                                                                                                                                           |

| 5     | OUT <sub>A</sub> | Power amplifier output A to motor.                                                                                                                                                                             |

| 6-7   | GROUND           | Power and logic ground and thermal heat sink.                                                                                                                                                                  |

| 8     | OUT <sub>B</sub> | Power amplifier output B to motor.                                                                                                                                                                             |

| 9     | OUT <sub>C</sub> | Power amplifier output C to motor.                                                                                                                                                                             |

| 10    | CENTERTAP        | Motor centertap connection for back-EMF detection circuitry.                                                                                                                                                   |

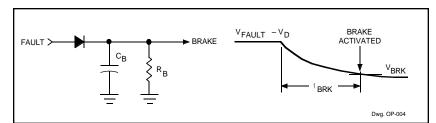

| 11    | BRAKE            | Active low turns ON all three sink drivers shorting the motor windings to ground. External capacitor and resistor at Brake provide brake delay. The brake function can also be controlled via the serial port. |

| 12    | C <sub>RES</sub> | External reservoir capacitor used to hold charge to drive the source drivers' gates. Also provides power for brake circuit.                                                                                    |

| 13    | FILTER           | Analog voltage input to control motor current. Also, compensation node for internal speed control loop.                                                                                                        |

| 14    | INDEX            | External tachometer input.                                                                                                                                                                                     |

| 15    | LOGIC SUPPLY     | V <sub>DD</sub> ; the 5 V logic supply.                                                                                                                                                                        |

| 16    | OSCILLATOR       | Clock input for the speed reference counter. Typical max. frequency is 10 MHz.                                                                                                                                 |

| 17    | DATA OUT         | Thermal shutdown indicator, FCOM, TACH, or SYNC signals available in real time, controlled by 2-bit multiplexer in serial port.                                                                                |

| 18-19 | GROUND           | Power and logic ground and thermal heat sink.                                                                                                                                                                  |

| 20    | RESET            | When pulled low forces the chip into sleep mode; clears all serial port bits.                                                                                                                                  |

| 21    | CHIP SELECT      | Strobe input (active low) for data word.                                                                                                                                                                       |

| 22    | CLOCK            | Clock input for serial port.                                                                                                                                                                                   |

| 23    | DATA IN          | Sequential data input for the serial port.                                                                                                                                                                     |

| 24    | C <sub>D1</sub>  | One of two capacitors used to generate the ideal commutation points from the back-EMF zero-crossing points.                                                                                                    |

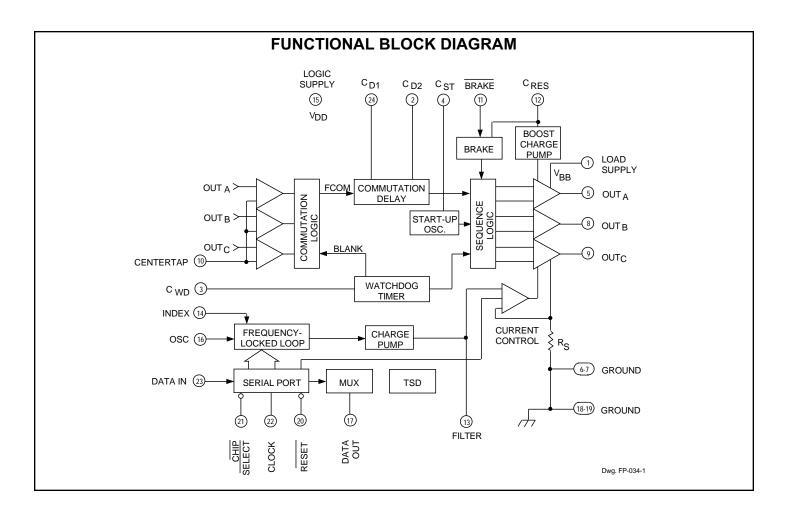

#### **FUNCTIONAL DESCRIPTION**

**Power Outputs.** The power outputs of the A8905CLB are n-channel DMOS transistors with a total source plus sink  $r_{DS(on)}$  of typically 1.1  $\Omega$ . Internal charge pump boost circuitry provides voltage above supply for driving the high-side DMOS gates. Intrinsic ground clamp and flyback diodes provide protection when switching inductive loads and may be used to rectify motor back-EMF in power-down conditions. An external Schottky power diode or pass FET is required in series with the load supply to allow motor back-EMF rectification in power-down conditions.

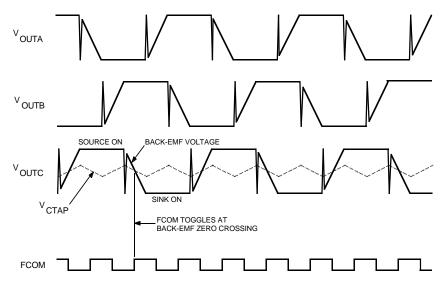

Back-EMF Sensing Motor Startup and Running Algorithm. The A8905CLB provides a complete self-contained back-EMF sensing startup and running commutation scheme. The three half-bridge outputs are controlled by a state machine. There are six possible combinations. In each state, one output is high (sourcing current), one low (sinking current), and one is OFF (high impedance or 'Z'). Motor back EMF is sensed at the OFF output. The truth table for the output drivers sequencing is:

| Sequencer<br>State | OUTA | OUTB | OUT <sub>C</sub> |

|--------------------|------|------|------------------|

| 1                  | High | Low  | Z                |

| 2                  | Ž    | Low  | High             |

| 3                  | Low  | Z    | High             |

| 4                  | Low  | High | Ž                |

| 5                  | Z    | High | Low              |

| 6                  | High | Z    | Low              |

At startup, the outputs are enabled in one of the sequencer states shown. The back EMF is examined at the OFF output by comparing the output voltage to the motor centertap voltage at CENTERTAP. The motor will then either step forward, step backward, or remain stationary (if in a null-torque position). If the motor moves, the back-EMF detection circuit waits for the correct polarity back-EMF zero crossing (output crossing through centertap). True back-EMF zero crossings are used by the adaptive commutation delay circuit to advance the state sequencer (commutate) at the proper time to synchronously run the motor.

Back-EMF zero crossings are indicated by FCOM, an internal signal that toggles at every zero crossing. FCOM is available at the DATA OUT terminal via the programmable data out multiplexer.

Dwg. WP-016-1

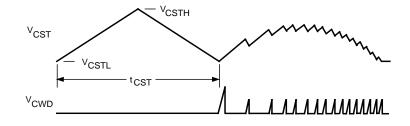

**Startup Oscillator.** If the motor does not move at the initial startup state, then it is in a null-torque position. In this case, the outputs are commutated automatically by the startup oscillator after a period set by the external capacitor at  $C_{ST}$ .

Dwg. WP-020

where

$$t_{CST} = \frac{4(V_{CSTH} - V_{CSTL}) \times C_{ST}}{I_{ST(charge)} + I_{ST(discharge)}}$$

In the next state, the motor will move, back EMF will be detected, and the motor will accelerate synchronously. Once normal synchronous back-EMF commutation occurs, the startup oscillator is defeated by pulses of pulldown current at  $C_{ST}$  at each commutation, which prevents  $C_{ST}$  from reaching its upper threshold and thus completing a cycle and commutating.

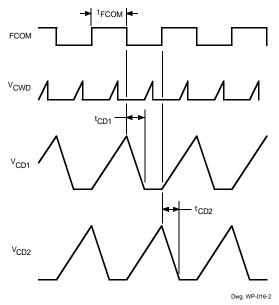

Adaptive Commutation Delay. The adaptive commutation delay circuit uses the back-EMF zero-crossing indicator signal (FCOM) to determine an optimal commutation time for efficient synchronous operation. This circuit commutates the outputs, delayed from the last zero crossing, using two external timing capacitors,  $C_{D1}$  and  $C_{D2}$ , to measure the time between crossings.

$$\label{eq:tcd} where \qquad t_{CD} = t_{FCOM} \, x \, \frac{I_{CD(charge),}}{\left[I_{CD(discharge)}\right]}$$

$C_{D1}$  charges up with a fixed current from its 2.5 V reference while FCOM is high. When FCOM goes low at the next zero crossing,  $C_{D1}$  is discharged at approximately twice the charging current. When  $CD_1$  reaches the CD threshold, a commutation occurs.  $C_{D2}$  operates similarly except on the opposite phase of FCOM . Thus the commutations occur approximately halfway between zero crossings. The actual delay is slightly less than halfway to compensate for electrical delays in the motor, which improves efficiency.

Because the commutation-delay capacitors are adaptive in nature, the absolute value and tolerance is not critical. In choosing these

capacitors, the voltage excursion should be 1.5 V to 2.5 V at rated speed. Solving for C in the equation I = Cdv/dt, where dv = 2.5 V,  $I = 22 \mu A$ , and

$$dt = t_{FCOM} = \frac{20/RPM}{\#motor\ poles}$$

Use of a capacitor slightly greater than this value will ensure that the commutation delay capacitors never charge to the high rail.

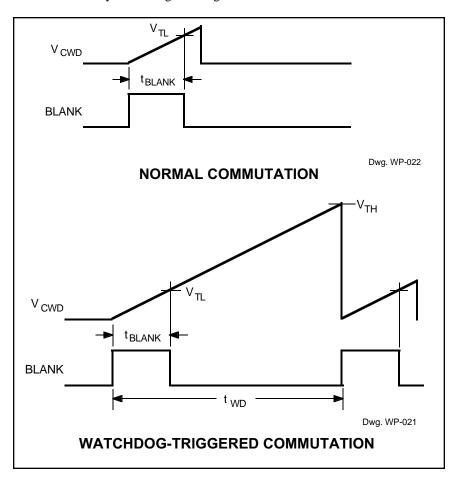

**Blanking and Watchdog Timing Functions.** The blanking and watchdog timing functions are derived from one timing capacitor,  $C_{WD}$ .

where

$$t_{\text{BLANK}} = \frac{V_{TL} \ x \ C_{WD}}{I_{CWD}}$$

and

$$t_{WD} = \frac{V_{TH} \ x \ C_{WD}}{I_{CWD}}$$

The CWD capacitor begins charging at each commutation, initiating the BLANK signal. BLANK is an internal signal that inhibits the back-EMF comparators during the commutation transients, preventing errors due to inductive recovery and voltage settling transients.

The watchdog timing function allows time to detect correct motor position by checking the back-EMF polarity after each commutation. If the correct polarity is not observed between  $t_{\text{BLANK}}$  and  $t_{\text{WD}}$ , then the watchdog timer commutates the outputs to the next state to synchronize the motor. This function is useful in preventing excessive reverse rotation, and helps in resynchronizing (or starting) with a moving spindle.

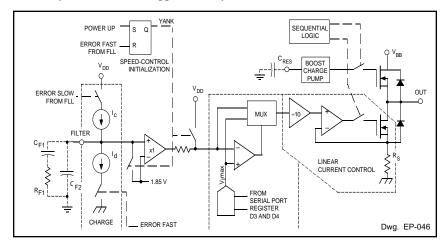

**Current Control.** The A8905CLB provides linear current control via the FILTER terminal, an analog voltage input. Maximum current limit is also provided, and is controlled in four steps via the serial port. Output current is sensed via an internal sense resistor ( $R_S$ ). The voltage across the sense resistor is compared to one-tenth the voltage at the FILTER terminal less two diode drops, or to the maximum current limit reference, whichever is lower. This transconductance function is  $I_{OUT} = (V_{FILTER} - 2V_D) / 10R_S$ , where  $R_S$  is nominally 0.3  $\Omega$  and  $V_D$  is approximately 0.7 V.

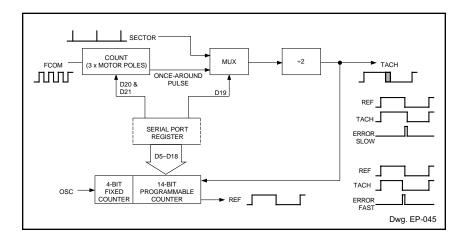

**Speed Control.** The A8905CLB includes a frequency-locked loop speed control system. This system monitors motor speed via internal or external digital tachometer signals, generates a precision speed reference, determines the digital speed error, and corrects the motor current via an internal charge pump and external filtering components on the FILTER terminal.

A once-per-revolution TACH signal can be generated by counting cycles of FCOM (the number of motor poles must be selected via the serial port). TACH is then a jitter-free signal that toggles once per motor revolution. The rising edge of TACH triggers REF, a precision speed reference derived by a programmable counter. The duration of REF is set by programming the counter to count the desired number of OSC cycles

$$\frac{\text{desired}}{\text{total count}} = \frac{60 \text{ x f}_{OSC}}{\text{desired motor speed (rpm)}}$$

where the total count (number of oscillator cycles) is equal to the sum of the selected (programmed low) count numbers corresponding to bits D5 through D18.

The speed error is detected as the difference in falling edges of TACH and REF. The speed error signals control the error-correcting charge pump on the FILTER terminal, which drive the external loop compensation components to correct the motor current.

Index. An external tachometer signal may be used to create the TACH signal, rather than the internally derived once around. To use this mode, the signal is input to the INDEX terminal, and the index mode must be enabled via the serial port. When Switching from the once-around mode to index mode, it is important to monitor the SYNC signal on DATA OUT, and switch modes only when SYNC is low. This ensures making the transition without disturbing the speed control loop. The speed reference counter should be reprogrammed at the same time.

Speed Loop Initialization (YANK). To improve the acquire time of the speed control loop, there is an automatic feature controlled by an internal YANK signal. The motor is started at the maximized programmed current by bypassing the FILTER terminal. The FILTER terminal is clamped to two diodes above ground, initializing it near the closed loop operating point. YANK is enabled at startup and stays high until the desired speed is reached. Once the first error-fast occurs, indicating the motor crossed through the desired speed, YANK goes low. This releases the clamp on the FILTER terminal and current control is returned to FILTER. This feature optimizes speed

acquire and minimizes settling. The Current Control Block Diagram illustrates the YANK signal and its effects.

**Braking.** A dynamic braking feature of the A8905CLB shorts the three motor windings to ground. This is accomplished by turning the three source drivers OFF and the three sink drivers ON. Activation of the brake can be implemented through the BRAKE input or through the D2 bit in the serial port. The supply voltage for the brake circuitry is the C<sub>RES</sub> voltage, allowing the brake function to remain active after power failure. Power-down braking with delay can be implemented by using an external RC and other components to control the brake terminal, as shown. Brake delay can be set using the equation below to ensure that voice-coil head retract occurs before the spindle motor brake is activated. Once the brake is activated, due to the inherent capacitive input, the three sink drivers will remain active until the device is reset.

$$t_{BRK} = R_B C_B \left( 1 - l_n \frac{V_{BRK}}{V_{FAULT} \cdot V_D} \right)$$

**Centertap.** The A8905CLB internally simulates the centertap voltage of the motor. To obtain reliable start-up performance from motor to motor, the motor centertap should be connected to this terminal.

**Serial Port.** The serial port functions to write various operational and diagnostic modes to the A8905CLB. The serial port DATA IN is enabled/disabled by the CHIP SELECT terminal. When CHIP SELECT is high the serial port is disabled and the chip is not affected by changes in data at the DATA IN or CLOCK terminals.

To write data to the serial port, the CLOCK terminal should be low prior to the CHIP SELECT terminal going low. Once CHIP SELECT goes low, information on the DATA IN terminal is read into the shift register on the positive-going transition of the CLOCK. There are 24 bits in the serial input port.

Data written into the serial port is latched and becomes active upon the low-to-high transition of the CHIP SELECT terminal at the end of the write cycle. D0 will be the last bit written to the serial port.

**Reset.** The RESET terminal (when pulled low) clears all serial port bits, including the D0 latch, which puts the A8905CLB in the sleep mode

#### **SERIAL PORT BIT DEFINITIONS**

- D0- Sleep/Run Mode; LOW = Sleep, HIGH = Run This bit allows the device to be powered down when not in use.

- D1- Step Mode; LOW = Normal Operation, HIGH = Step Only When in the step-only mode the back-EMF commutation circuitry is disabled and the power outputs are commutated by the start-up oscillator. This mode is intended for device and system testing.

- D2- Brake; LOW = Run, HIGH = Brake.

D3 and D4-These two bits set the output current limit:

| D3 | D4 | <b>Current Limit</b> |

|----|----|----------------------|

| 0  | 0  | Saturated            |

| 0  | 1  | 1 A                  |

| 1  | 0  | 800 mA               |

| 1  | 1  | 600 mA               |

|    |    |                      |

D5 thru D18-This 14-bit word (active low) programs the REF time to set desired motor speed.

| Bit Number | Count Number |

|------------|--------------|

| D5         | 16           |

| D6         | 32           |

| D7         | 64           |

| D8         | 128          |

| D9         | 256          |

| D10        | 512          |

| D11        | 1 024        |

| D12        | 2 048        |

| D13        | 4 096        |

| D14        | 8 192        |

| D15        | 16 384       |

| D16        | 32 768       |

| D17        | 65 536       |

| D18        | 131 072      |

D19-Speed-control mode switch;

LOW = internal once-around speed signal,

HIGH = external index data.

D20 and D21-These bits program the number of motor poles for the once-around FCOM counter:

| D20 | D21 | Motor Poles |

|-----|-----|-------------|

| 0   | 0   | 8           |

| 0   | 1   | _           |

| 1   | 0   | 16          |

| 1   | 1   | 12          |

D22 and D23-Control the multiplexer for DATA OUT:

| D22 | D23 | Data Out                    |

|-----|-----|-----------------------------|

| 0   | 0   | TACH (once around or index) |

| 0   | 1   | Thermal Shutdown            |

| 1   | 0   | SYNC                        |

| 1   | 1   | FCOM                        |

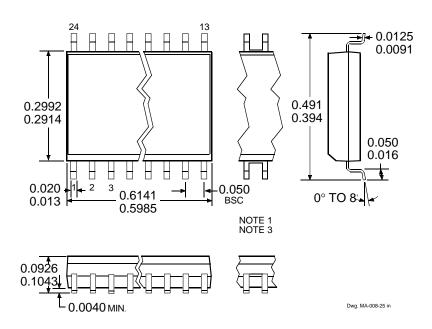

## Dimensions in Inches (for reference only)

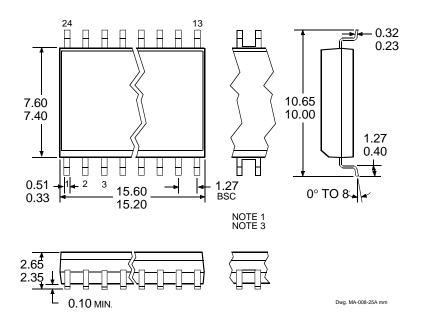

#### **Dimensions in Millimeters**

(controlling dimensions)

NOTES: 1. Webbed lead frame. Leads 6, 7, 18, and 19 are internally one piece.

- 2. Lead spacing tolerance is non-cumulative.

- 3. Exact body and lead configuration at vendor's option within limits shown.

Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the design of its products.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringements of patents or other rights of third parties which may result from its use.