# Acapella Optical Modem IC ACS411CS Main Features

- \* Three chip set supporting full duplex serial transmission over twin optical fiber, one fiber with WDM.

- \* Configurable parallel microprocessor bus interface.

- \* Up to 16 independent synchronous data channels.

1 x OC1 (STS1) @ 51.840Mbps

1 x E3/T3

4 x E2, 7 x T2

16 x E1/T1

- \* Select between NRZ and pseudo-bipolar HDB3/AMI/B3ZS/ B6ZS/B8ZS input data coding types.

- \* Incorporates 2 x 256kbps maintenance channels with option of multi channel operation with a framing signal.

- \* Link budgets of 27dB with Laser + PIN on single mode fiber.

- \* Conforms to all jitter attenuation, jitter transfer and input jitter tolerance specification defined by AT&T, ITU-T and Bellcore recommendations.

- \* Bit Error Rate (BER) of < 10<sup>-10</sup>

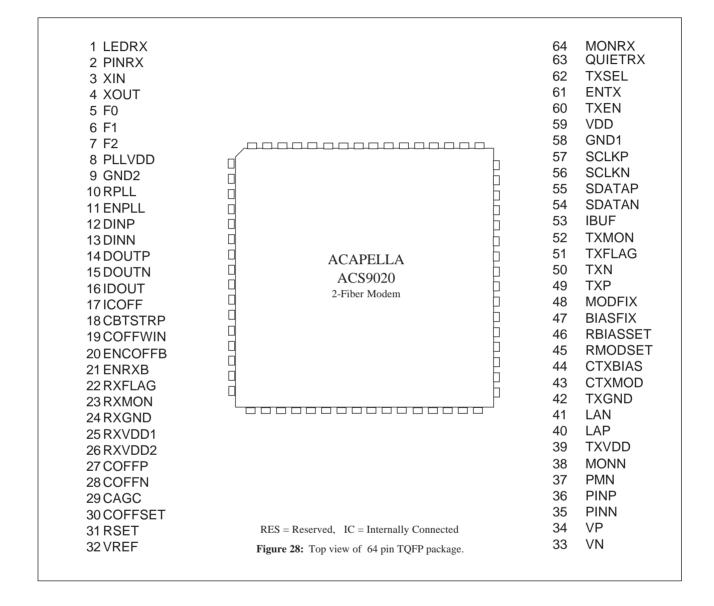

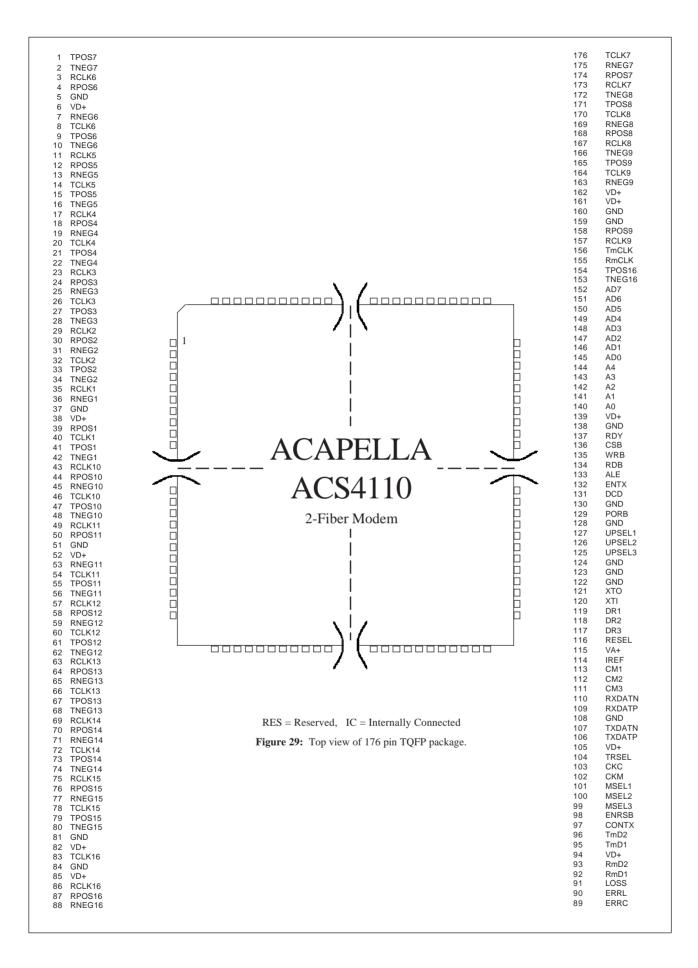

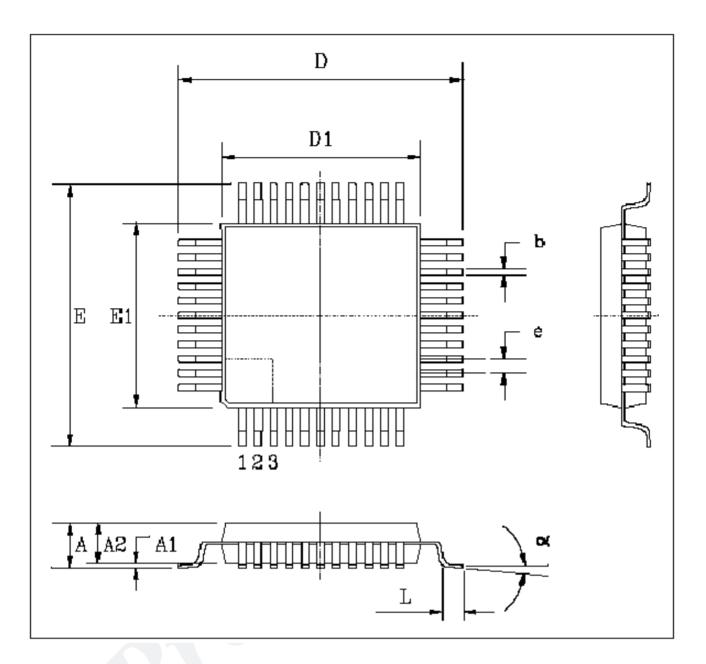

- \* ACS9020 available in 64 pin TQFP and ACS4110 available in 176 pin TQFP package.

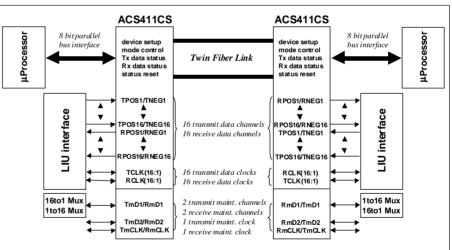

Twin fiber full duplex system using ACS411CS chip set with external T1/E1 Framer ICs and microprocessor.

# **General Description**

The ACS411CS is a complete controller, driver and receiver chipset supporting full-duplex synchronous transmission up to 51.840Mbps over single/twin optical fiber. The designer can share the available bandwidth over 1 to 16 main channels.

In addition to the main channels, the ACS411CS provides two independent maintenance channels with a data rate selectable up to 256kbps. On the electrical side the ACS411CS has a selectable interface for either NRZ or the pseudo bipolar data coding types HDB3/AMI/B3ZS/B6ZS/B8ZS.

The ACS411CS has a parallel microprocessor bus interface. This can be used for device set-up, diagnostics, control and status analysis. Additional flags for Tx data status, Rx data status and alarm indication for both near end and far end receive fail are accessible via the uP interface. Communicating modems automatically maintain synchronization with each

# **Acapella Optical Modem IC**

# ACS411CS

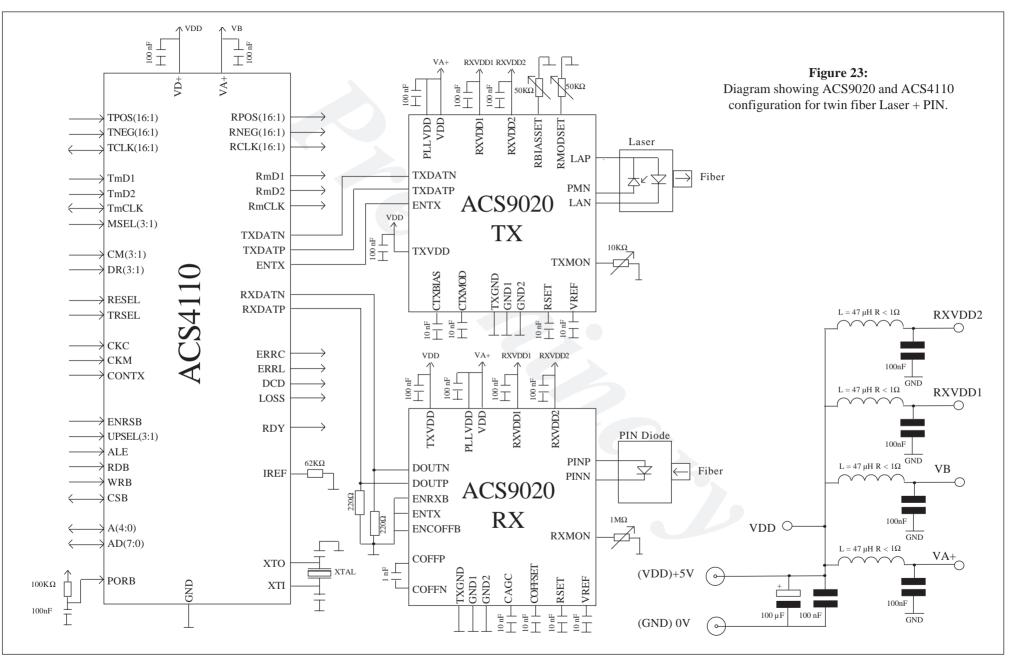

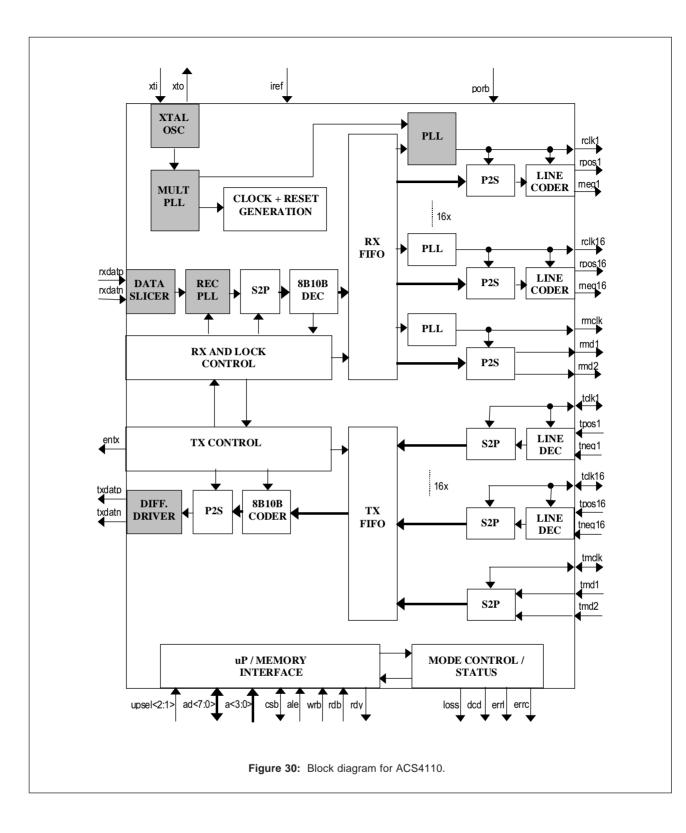

The ACS411CS comprises a chip set of two/three (link budget dependent) highly integrated devices, the ACS9020 and ACS4110. The ACS9020 is an analogue device and the ACS4110 is predominately a digital device.

The ACS9020 contains the Laser/LED driver as well as the PIN receiver circuitry. Since the devices are transmitting and receiving continuously, for long haul applications two ACS9020 devices are required, one configured as the transmitter and the other configured as the receiver.

The ACS4110 comprises the logic necessary to time compress and decompress the data, plus clock recovery and all the logic associated with valid data transmission and reception and locking status. The ACS4110 also has a configurable parallel microprocessor bus interface for device configuration (control) and status analysis. The device setup is also possible via the far end (remote control) or directly via pins for the basic device setup.

For the purpose of this specification the chip-set will be referred to as the ACS411CS and the individual devices as the ACS9020 or ACS4110.

For low link budget applications (up to 10dB) two chips, the ACS9020 analogue IC (including laser driver and PIN receiver circuitry) and the ACS4110 are sufficient.

For applications requiring a higher link budget (up to 30dB) a three chip solution has to be used, where the laser driver and PIN receiver circuitry are separated.

#### **Inter-Modem Coding**

The inter-IC coding between communication modems is 8B10B. Whilst transparent to the user, 8B10B encoding ensures that there is no DC component in the signal, and provides frequent data transitions, factors which ease the task of data recovery and clock extraction.

The coding rules are continuously checked to ensure the integrity of the link, and errors are indicated on the ERRL and ERRC pins (see section headed ERRC and ERRL - Error Detection ).

#### **Transmit and Receive functions**

Data presented at the near-end TPOS/TNEG is timecompressed, encoded in the 8B10B format and transmitted over the fiber link to the far end receiver. Similarly, data presented at the far-end TPOS/TNEG is time-compressed, encoded in the 8B10B format and transmitted over the other fiber link to the near end.

#### PORB

The Power On Reset (PORB) pin resets the device if forced low for 2ms or more. In normal operation PORB should be held High. It is recommended that PORB is connected to VD+ via a 100K $\Omega$  resistor and to GND via a 100nF capacitor.

#### System Clock

The system clock on the ACS411CS is derived locally using the on-chip crystal oscillator and multiplying PLL.

The oscillator (XTO/I) requires the use of a fundamental parallel resonance crystal with appropriate padding capacitors. The crystal specification should be:

| Calibration tolerance: | +/- 20ppm @ 25°C        |

|------------------------|-------------------------|

| Temp. tolerance:       | +/-20ppm @ -40 to +85°C |

| Temperature range:     | -40 to +85°C            |

| Load condition:        | parallel load 15pF      |

Padding capacitor: 18-22pF (tune for desired tolerance)

The system clock defines the burst frequency at which data is transmitted over the optical link via the optical interface. The receive circuitry within the ACS4110 recovers the clock from the received data at the RXDAT inputs and produces a clock that is synchronised to the incoming data stream. The system clock must have a maximum tolerance of +/-50ppm over the desired temperature range.

#### **Optical Operational Modes**

The ACS411CS has four optical operational modes, all supporting twin fiber. The ACS9020 can also utilise Lasers/LED and PIN combinations, including a PIN with an internal Trans-Impedence Amplifier (TIA) controlled by PINRX.

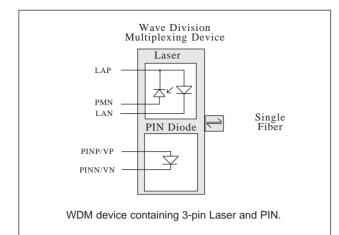

The twin fiber Laser modes in Table 1 may be converted to single fiber operation simply by interfacing to Wave Division Multiplexer (WDM) device indicated by mode 5.

| Mode | Optical Device                               |

|------|----------------------------------------------|

| 1    | Laser and PIN diode without TIA.             |

| 2    | Laser and PIN diode with integrated TIA.     |

| 3    | LED and PIN diode without TIA.               |

| 4    | LED and PIN diode diode with integrated TIA. |

| 5    | WDM                                          |

|      |                                              |

Table 1: Optical modes

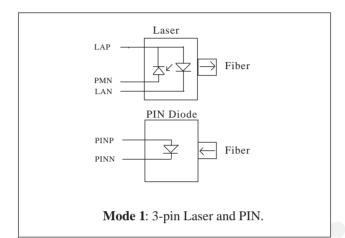

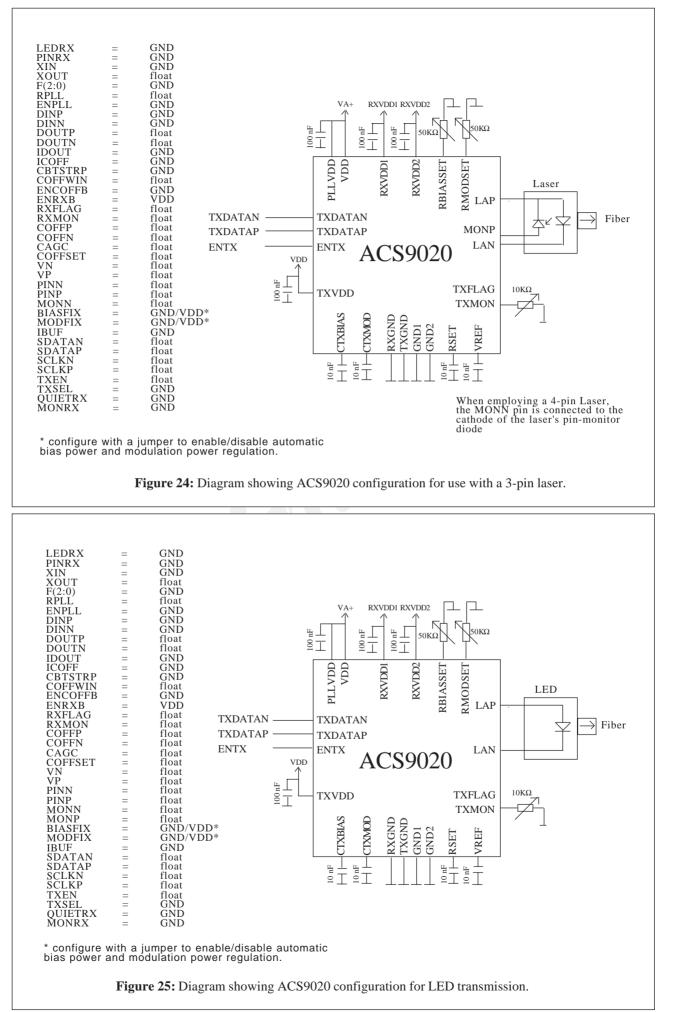

#### Mode 1 - Laser & PIN without integrated TIA

In mode 1, the device is configured for use with a Laser and a PIN Diode without a TIA. In this configuration it is important to employ the TIA available within the ACS9020. The ACS9020 TIA is activated by setting PINRX = High.

In this configuration, the PIN Diode should be connected to the PINP/PINN pins so that the TIA/ Post-Amp combination on the ACS9020 is used.

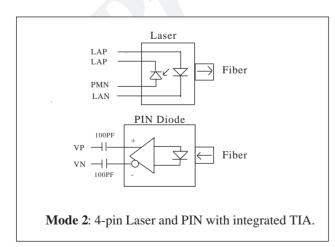

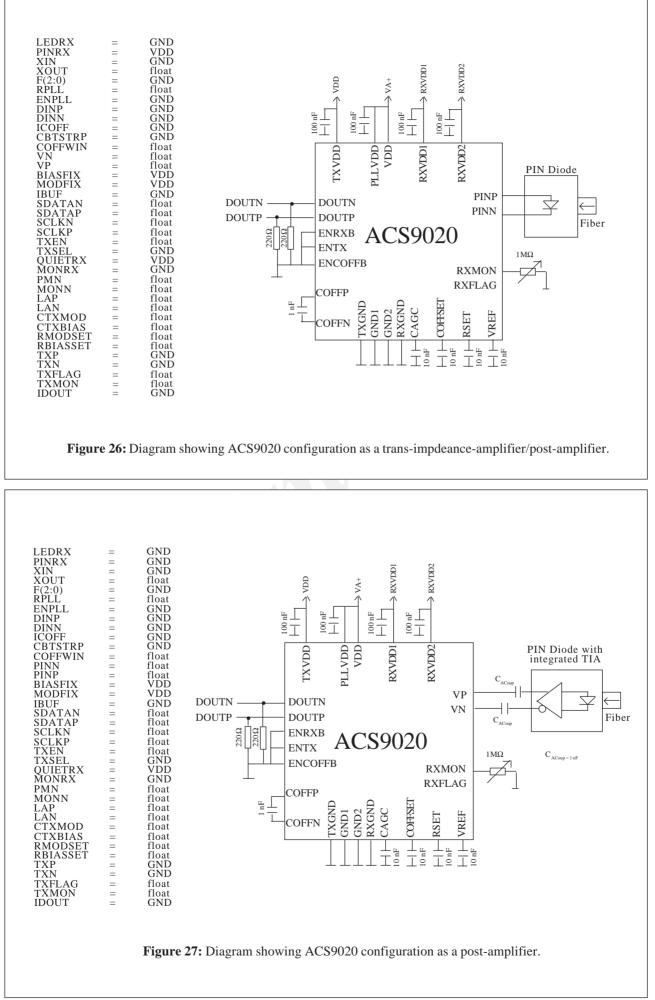

#### Mode 2 - Laser and & PIN Receiver with a TIA.

In mode 2, the device is configured for use with a Laser and PIN Diode with an integrated TIA (Pin Receiver). In this mode it is important to bypass the TIA on the ACS9020 device. The VP/VN inputs are activated by setting PINRX = Low.

In this mode, the outputs from the PIN Receiver should be connected to the VP/VN inputs of the ACS9020 Post-Amp via AC coupling capacitors as shown in the diagram below.

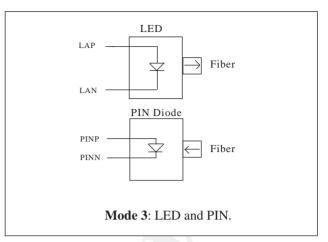

#### Mode 3- LED & PIN without integrated TIA

In mode 3, the device is configured for use with a LED and a PIN Diode without a TIA. In this configuration it is important to employ the TIA available within the ACS9020. The ACS9020 TIA is activated by setting PINRX = High.

In this configuration, the PIN Diode should be connected to the PINP/PINN pins so that the TIA/ Post-Amp combination on the ACS9020 is used.

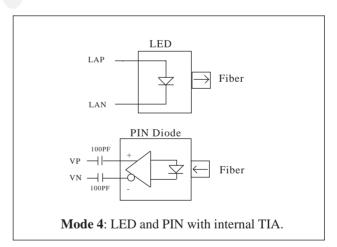

#### Mode 4 - LED & PIN with a TIA.

In mode 4, the device is configured for use with an LED and PIN Diode with an integrated TIA (Pin Receiver). In this mode it is important to bypass the TIA on the ACS9020 device.The VP/VN inputs are activated by setting PINRX = Low.

In this mode, the outputs from the PIN Receiver should be connected directly to the VP/VN inputs of the ACS9020 Post-Amp via AC coupling capacitors as shown in the diagram below.

#### Mode 5 - WDM Bidirectional Device

The device can be configured for use with a WDM device (with and without a TIA) to realise a single fiber link. The electrical connections are the same as those for mode1 and mode2 dependent on whether the WDM bidirectional device has a TIA included or not.

If the device has a TIA integrated then the receivers Positive/Negative differential outputs are connected to VP/VN respectively via AC coupling capacitors with PINRX set Low.

If the device does not have an integrated TIA then the PIN Diodes's Cathode/Anode is connected to PINP/PINN respectively with PINRX set High.

#### **Control of LED Current**

To minimise the switching delay, a permenent bias current is maintained through the LED. A second current source called the modulation current varies the intensity of the output light power such that:

Optical Low current = Bias current.

Optical high current = Bias current + Modulation current

Unlike Lasers, LED's have a linear relationship between current and output light power. Also, the output power of LEDs does not vary significantly with temperature. Therefore, LEDs are driven with a predetermined biased current and modulation current fixed by the resistors between RBIASET and GND and RMODSET and GND respectively. In order to fix the modulation current the signal MODFIX should be set = High.

The bias current is determined by a resistor connected between pin RBIASSET and Ground.The bias current can be calculated from the formula below:

#### I (LAN) (BIAS) = 50/ R<sub>RBIASSET</sub>

Where  $R_{RBIASSET} > 1$ Kohm, tolerance +/- 20%

I = Amps

The modulation current is determined by a resistor connected between pin RMODSET and Ground.The modulation current can be calculated from the formula below:

#### $I_{(LAN)}$ (MOD) = 100/ $R_{RMODSET}$

Where  $R_{RMODSET} > 1$ Kohm, tolerance +/- 20%

I = Amps

When setting the bias current and the modulation current it is important to ensure that the sum of the component currents do not exceed 100 mA.

$$I_{(LAN)} = I_{(BIAS)} + I_{(MOD)} <= 100 \text{ mA}$$

The bias current and modulation currents should be set to give the appropraite extinction ratio. The extinction ratio is the ratio of the optical high power compared to the optical low power.

Eg. An extinction ratio of 13db, is where the optical high power is 20 times the optical low power.

#### **Control of LASER Current**

To minimise switching the delay, a permenent bias current is maintained through the LASER. A second current source called the modulation current varies the intensity of the output light power such that:

Optical Low current = Bias current.

Optical high current = Bias current + Modulation current

For Lasers, there is a non-linear relationship between the output power and the applied current. In addition, Laser output power will vary significantly with temperarure for a constant current. For these reason Laser drive current must be controlled so as to maintain a constant optical output power from the Laser. The monitor pin resident in the laser converts the incident light power (typically leaked from the rear facet of the laser itself) to a monitor current, which is directly compared to a preset programmed current (the current flowing through RMODSET). The Laser drive current is automatically adjusted to maintain the original preset light level over the temperature and voltage range. The designer should be aware that whilst the control loop maintains the current generated by the monitor-pin within a tolerance of 2%, there is additional uncertainty attributed to the monitor-pin's temperature coefficient of responsivity. Data relating to the Laser characteristics should be acquired from the Laser supplier.

The bias current is set in the same way as it is for the LED driver. The bias current is determined by a resistor connected between pin RBIASSET and GND. The bias current can be calculated from the formula below:

#### $I_{(LAN)}$ (BIAS) = 50/ $R_{RBIASSET}$

Where  $R_{RBIASSET} > 1$ Kohm, tolerance +/- 20%

I = Amps

Whilst the bias current flowing through the Laser is fixed, the modulated component is automatically regulated to maintain a near constant output light power. In order to activate the automatic regulation of the modulation current it is important that the pin MODFIX is set Low.

The monitor-pin current is set by a variable resistor ( $R_{\text{RMODSET}}$ ) connected between pin RMODSET and Ground. Acapella recommends that  $R_{\text{RMODSET}}$  should comprise a logarithmic potentiometer of value 50

Kohms. It is important that  $R_{\text{RMODSET}}$  is inserted and adjusted to its maximum resistance value of 50 Kohms prior to applying power to the ACS9020 for the first time and prior to following the procedure detailed in section headed, *Laser Adjustment Procedure*.

#### I<sub>(PMN - AVERAGE)</sub> (BIAS + MOD) = 1/ R<sub>RMODSET</sub>

Where  $R_{RMODSET} > 1$ Kohm, tolerance +/- 20%

#### **TXMON and TxFLG**

TXMON is used to monitor the current delivered to the LED or Laser. TXMON is a current source that proportionally mirrors the current flow through the LED or Laser. By placing an appropriate external resistor  $R_{TXMON}$  between TXMON and GND, the voltage developed (referenced to GND), will be proportional to the transmit current. During the Laser setup procedure TXMON should be monitored to ensure that the Laser manufacturer's maximum current specification is not exceeded.

The transmit current monitor is a current source flowing from VDD out of pin TXMON. This current is representative of the Laser/LED drive current.

$I_{\text{TXMON}} = I_{\text{BIAS}} / 50 + I_{\text{MOD}} / 100$

I<sub>BIAS</sub> is the Low level bias current.

$I_{\text{MOD}}$  is the peak Modulation level bias current. The average modulation current is half this value.

Average drive current,  $I_{AVG} = (I_{BIAS} + I_{MOD})/2$

Therefore  $I_{TXMON} = I_{AVG}/50$

TXMON may also be employed during normal operation to continuously check the Laser current. The voltage developed across  $R_{TXMON}$  is compared within an internally generated reference voltage of 1.25V. In the event that the reference voltage is exceeded, the TXFLAG is set High, otherwise it is set Low. In this way, the value of resistor on TXMON can be chosen to activate TXFLAG at any desired transmit current

e.g. If  $\rm R_{_{TXMON}}$  = 1KW, then TXFLAG will be set if  $\rm I_{_{AVG}}$  exceeds 62.5mA.

If desired, TXFLAG activation can be delayed by adding a damping capacitor between TXMON and GND.

#### Laser Adjustment Procedure

The output power from the Laser should be measured with an optical power meter during the setup procedure. In addition TXMON may be monitored to ensure that manufacturers maximum current limits are not exceeded during the set-up process. Select one of the laser drive modes in accordance with the section headed, *Optical Operational Modes*. Start be setting the current control resistors  $R_{\text{RMODSET}}$  and  $R_{\text{RBIASSET}}$  to their highest values (at least 50Kohm is recommended).

The bias current is then set to the desired level by adjusting the variable resistor  $R_{RBIASSET}$ . Since the bias current sets the optical low-level for the Laser, it is essential that the Laser driver data inputs are set at a continuous logic low level. The resistor value (typically a 50K potentiometer) is reduced until the desired bias current is achieved or until the desired low-level optical output power is achieved. It should be understood that since the bias current is fixed (not regulated), the low level optical output power will vary across the temperature and voltage range.

Once the bias current is set, the modulation current maybe set by adusting the variable resistor R<sub>RMODSET.</sub> The automatic power regulation circuitry for the modulation current maintains the average optical output power and not the peak power. For this reason, during the set-up process in the absence of the appication data, it is recommended that the Laser driver is stimulated with a square wave. Most application data used in fiber optic transmission is dc-balanced (equal number of ones and zeros), so a square-wave is an accurate representation of the real data.

The resistor value (typically a 50K potenmtiometer) is reduced until the desired optical-high ouput power is achieved. The modulation ouput power will then be regulated such that the average ouput optical output power (bias + modulation) is mainatined over the recommended temperature and voltage range.

#### **Receive Monitor RXMON and RXFLAG**

The ACS9020 incorporates a power meter which generates a current source on the RXMON pin, which is proportional to the received signal strength. A voltage is generated on an internal 50Kohm resistor which is continuously compared with an internally generated reference of 1.25 volts.

The RXFLAG is set when the RXMON voltage exceeds the 1.25 volt reference. The flag is used to indicate that there is sufficient signal strength to give a minimum differential output signal on the receiver output pins DOUTP and DOUTN. If the voltage on DOUTP/DOUTN exceeds 500 mV peak-to-peak then the RXMON voltage will exceed 1.25 Volts and the RXFLAG will be set.

Because of process tolerances on the internal resistor and the internally generated reference voltage, the RXFLAG should be considered only as a guide to the receive signal strength. The receive threshold can be adjusted by placing a 1Mohm external potentiometer between the RXMON pin and Ground.

#### Transmit monitor TXMON and TXFLAG

TXMON is used to monitor the current delivered to the LED or Laser. TXMON is a current source that proportionally mirrors the current flow through the LED or Laser. By placing an appropriate external resistor  $R_{TXMON}$  between TXMON and GND, the voltage developed (referenced to GND), will be proportional to the transmit current. During the Laser setup procedure TXMON should be monitored to ensure that the Laser manufacturer's maximum current specification is not exceeded.

The transmit current monitor is a current source flowing from VDD out of pin TXMON. This current is representative of the Laser/LED drive current.

$I_{\text{TXMON}} = I_{\text{BIAS}} / 50 + I_{\text{MOD}} / 100$

I<sub>BIAS</sub> is the Low level bias current.

$I_{\text{MOD}}$  is the peak Modulation level bias current. The average modulation current is half this value.

Average drive current,

$$I_{AVG} = (I_{BIAS} + I_{MOD}) /2$$

Therefore  $I_{TXMON} = I_{AVG} / 50$

TXMON may also be employed during normal operation to continuously check the Laser current. The voltage developed across  $R_{TXMON}$  is compared within an internally generated reference voltage of 1.25V. In the event that the reference voltage is exceeded, the TXFLAG is set High, otherwise it is set Low. In this way, the value of resistor on TXMON can be chosen to activate TXFLAG at any desired transmit current

e.g. If  $R_{TXMON} = 1K\Omega$ , then TXFLAG will be set if  $I_{AVG}$  exceeds 62.5mA.

If desired, TXFLAG activation can be delayed by adding a damping capacitor between TXMON and GND.

#### **Receive Monitor RXMON and RXFLAG**

The ACS9020 incorporates a power meter which generates a current source which is proportional to the received optical current.

There is an internal resistor of value of  $50K\Omega$  +/- 20 % connected between RXMON and GND which converts the current into a voltage.

RXMON is compared with 1.25V. If RXMON exceeds 1.25V, then output RXFLAG is set = 1, otherwise RXFLAG is set = 0. With the internal resistor of  $50K\Omega$ . By adding an external parallel resistor between RXMON and GND, this threshold may be increased.

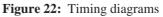

#### **Transmission Clock TCLK**

There are 16 independent Transmit clocks TCLK(16:1) on the ACS4110. For the purpose of this specification, these signals will be referred to collectively as TCLK. The ACS4110 gives a choice between internally and externally generated transmit clocks. When the CKC pin is held Low, the set of TCLK clocks are configured as outputs producing a clock at the frequency defined by DR(3:1).

When the CKC pin is held High, the set of TCLK clocks are configured as inputs, and will accept an externally produced transmission clock with a tolerance of up to 250ppm with respect to the transmission rate determined by DR(3:1).

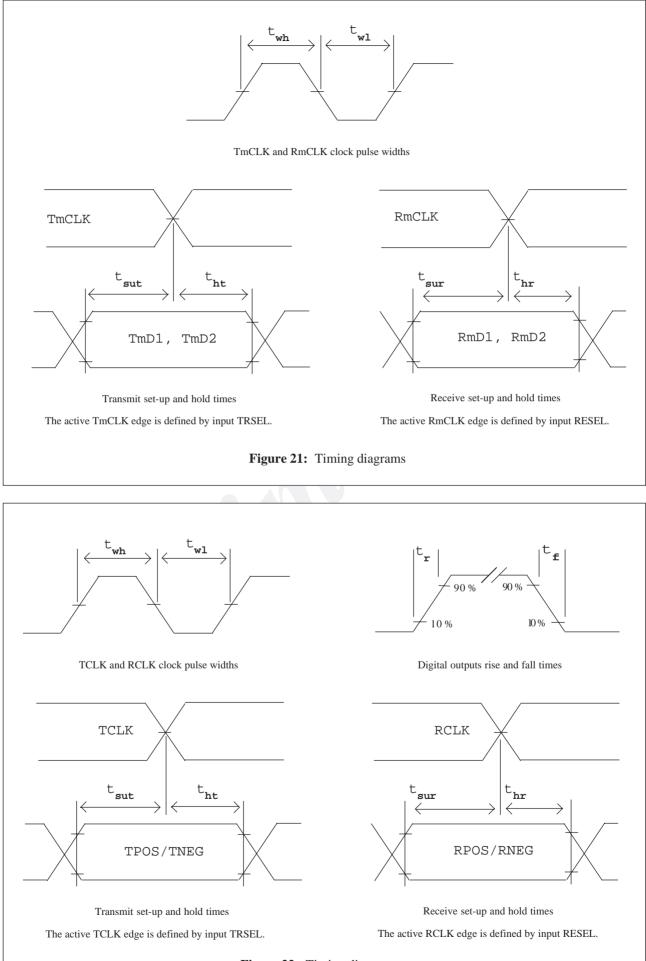

The data appearing on TPOS/TNEG is valid on the rising or falling edge of the TCLK clock dependent on the setting of TRSEL *(see Figure 22. Timing diagrams).* This is the case for both internally and externally generated transmission clocks.

#### **Receive Clock RCLK**

There are 16 independent Receive clocks RCLK(16:1) on the ACS4110. For the purpose of this specification, these signals will be referred to collectively as RCLK.

The data appearing on RPOS/RNEG is valid on the rising or falling edge of the RCLK clock dependent on the setting of RESEL *(see Figure 22. Timing diagrams)*. To ensure that the average receive frequency is the same as the transmitted frequency, RCLK is generated from a Phase-Lock Loop (PLL) system (except where master mode has been selected). The PLL makes periodic corrections to the output RCLK clock by subtracting or adding a single crystal clock bit-period, so that the average frequency of the RCLK clock tracks the average frequency of the transmit clock of the far-end modem (or system master clock). This decompression/dejittering function is covered in more detail in section headed, *Jitter Characteristics.*

The recovery and de-jittering functions comply to jitter tolerance and jitter transfer specifications of the selected data rates. The algorithm that determines the transfer function and response of the PLLs is modified (shaped) according to the selected data rate.

#### **System Frequencies and Clock Generation**

The crystal clock frequency and the multiplying factors of the MPLL are determined by the choice of data rates. Table 2 lists the required frequencies of the system.

| Mode    | Data Rate      | XTAL       | Fsys   |

|---------|----------------|------------|--------|

|         | MHz            | MHz        | MHz    |

| 16 x T1 | 1.544          | 23.160     | 69.480 |

| 16 x E1 | 2.048          | 22.528     | 67.584 |

| 7 x T2  | 6.312          | 23.144     | 69.432 |

| 4 x E2  | 8.448          | 22.528     | 67.584 |

| 1 x E3  | 34.368         | 22.912     | 68.736 |

| 1 x T3  | 44.736         | 22.368     | 67.104 |

| 1 x OC1 | 51.840         | 25.920     | 77.760 |

|         | Table 2: Syste | em frequen | cies   |

#### **Data Coding**

The main synchronous channels may use any of the following coding methods: NRZ, AMI, HDB3, B3ZS, B6ZS and B8ZS. The desired mode is selected by POL(3:1) input pins, as shown in Table 3.

| Data<br>Coding | POL3             | POL2         | POL1 |

|----------------|------------------|--------------|------|

| NRZ            | 0                | 0            | 0    |

| AMI            | 0                | 0            | 1    |

| HDB3           | 0                | 1            | 0    |

| B8ZS           | 0                | 1            | 1    |

| B6ZS           | 1                | 0            | 0    |

| B3ZS           | 1                | 0            | 1    |

| NRZ            | 1                | 1            | 0    |

| NRZ            | 1                | 1            | 1    |

|                | le 3: Line codir | ng selection | ·    |

For Non-Return-to-Zero (NRZ) coding, data is applied directly to TPOS inputs, and output data appears only on the RPOS output pins. When using NRZ code, unconnected TNEG input pins will automatically pull-up to VD+. In addition, the ACS411CS will assert a continuous Low on redundant RNEG output pins.

AMI, B3ZS, B6ZS, B8ZS and HDB3 coding is normally bipolar. However, it is possible to interface with the ACS411CS using two inputs and outputs rather than a single bipolar interface. Data equivalent to positive excursions of the bipolar AMI/BxZS/HDB3 signal are applied as a logic High to TPOS, while data equivalent to negative excursions are applied as a logic High to TNEG. Similarly, AMI/BxZS/HDB3 positive excursions will appear as a logic High on RPOS and negative excursions will appear as a logic High on RNEG. It is anticipated that most users of the ACS411CS will interface directly with a E1/T1 framers. All the popular framers provide POS/NEG bipolar interfaces which will directly connect to the ACS4110.

If required, a detailed description of the AMI/HDB3/ BxZS coding rules are available from Acapella.

#### **Data Rate Selection**

For the purpose of this specification TPN1 represents the set of signals TPOS1 and TNEG1, and RPN1 represents the set of signals RPOS1 and RNEG1. See section headed, *Data Coding* for a description of the coding types.

The maximum recommended crystal (XTAL) is 26.88MHz. An internal multiplier factors the XTAL frequency by 3. The maximum bandwidth is 51.840MHz (OC1). This bandwidth can be utilised in various ways, it may be divided up over 1, 4, 7 or 16 channels.

All 16 main channels are completely independent. One channel consists of the following 6 signals:

Transmit side:

| TPOS        | +ve in bipolar signal or NRZ data     |

|-------------|---------------------------------------|

| TNEG        | -ve in bipolar signal TPOS            |

| TCLK        | transmit clock (internal or external) |

| Receive sid | de:                                   |

| RPOS        | +ve in bipolar signal or NRZ data     |

| RNEG        | -ve in bipolar signal or NRZ data     |

| RCLK        | receive clock                         |

|             |                                       |

The data rate can be selected via the data rate selection bits DR(4:1), either directly via pins or via the microprocessor interface. The selection determines the number of active channels in combination with the selected crystal frequency and the line data rate in accordance with Table 4.

| DF<br>3 | R Pin<br>2                               | is<br>1 | TCLK<br>(MHz) | Nos. of channels | Tmode   |

|---------|------------------------------------------|---------|---------------|------------------|---------|

| 1       | 1                                        | 0       | 1.544         | 16               | 16 x T1 |

| 1       | 0                                        | 1       | 2.048         | 16               | 16 x E1 |

| 1       | 0                                        | 0       | 6.312         | 7                | 7 x T2  |

| 0       | 1                                        | 1       | 8.448         | 4                | 4 x E2  |

| 0       | 1                                        | 0       | 34.368        | 1                | 1 x E3  |

| 0       | 0                                        | 1       | 44.736        | 1                | 1 x T3  |

| 0       | 0                                        | 0       | 51.840        | 1                | 1 x OC1 |

|         | Table 4: Data rate and channel selection |         |               |                  |         |

Channels not used in a specific mode are disabled. For example in  $4 \times E2$  mode channels 1 to 4 are carrying E2 data rates, and channels 5 to 16 are disabled. All channels can be disabled individually via the microprocessor interface, or alternatively via far-end remote control.

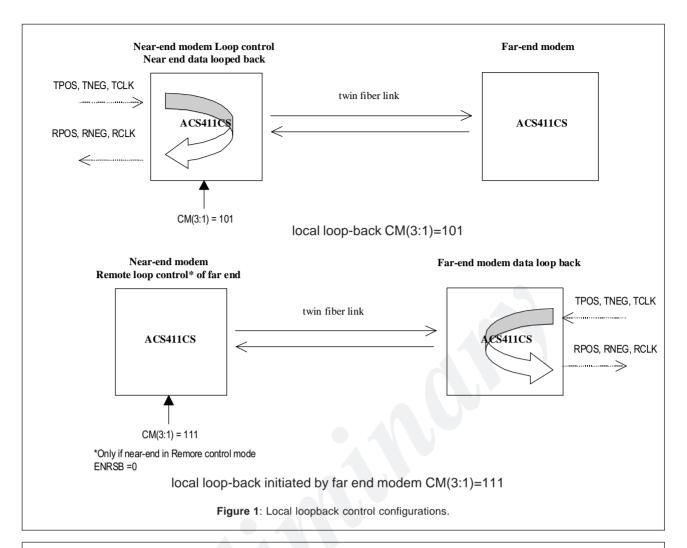

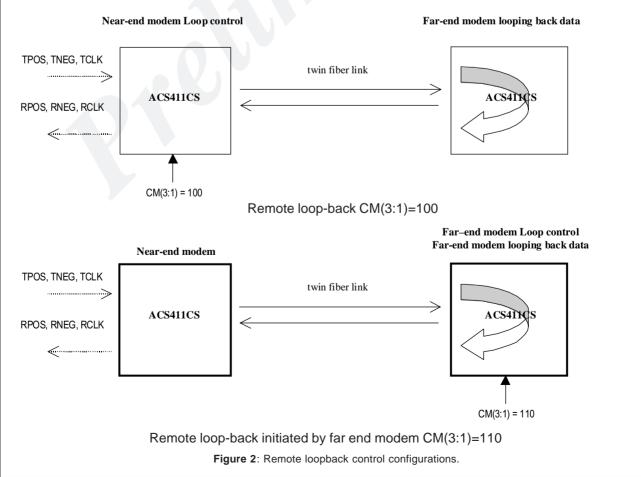

#### **Diagnostic modes (main channel)**

The ACS4110 has four diagnostic/configuration modes implemented for the main channels, configured by CM(3:1). The following diagnostic/configuration modes are implemented for the main channels:

- full duplex

- full duplex slave

- full duplex master

- remote loop-back

- local loop-back

The modes are selectable via CM(3:1) either directly via pins, via the microprocessor interface or via remote control setup. All modes remote loop-back and local loop-back are selectable individually for each channel via the microprocessor interface. Table 5. shows the selection of diagnostic modes and configurations.

| CM(3:1) | Diagnostic Mode/Configuration                  |

|---------|------------------------------------------------|

| 111     | local loop-back initiated from far end         |

|         | (remote setup only)                            |

| 110     | remote loop-back initiated from far end        |

| 101     | local loop-back                                |

| 100     | remote loop-back                               |

| 011     | full duplex master                             |

| 010     | full duplex slave                              |

| 001     | full duplex slave/remote full duplex           |

|         | (remote setup only)                            |

| 000     | full duplex                                    |

|         |                                                |

| _       |                                                |

| 1       | Table 5:         Selection of diagnostic modes |

In remote setup (ENRSB=0), the far-end device will be setup complementary to the near-end device (control device) according to the Table 6.

| CM(3:1)                                              | Near End initiate<br>(Control device)                                                                                                  | Far End initiate<br>(Remote control device)                                                                                      |

|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| 111<br>110<br>101<br>100<br>011<br>010<br>001<br>000 | full duplex<br>*<br>local loop-back<br>remote loop-back<br>full-fuplex master<br>full-duplex slave<br>full-duplex slave<br>full duplex | local loop-back<br>remote loop-back<br>full duplex<br>*<br>full-duplex slave<br>full-duplex master<br>full-duplex<br>full duplex |

|                                                      |                                                                                                                                        |                                                                                                                                  |

Table 6: Selection of diagnostic modes

\* Remote Loop-back Detect.

For a remote loop-back initiated from the far end device, CM(3:1)=110, the initiating end transmitting and receiving the data will be setup as full duplex (see Figure:1).

For remote loop-back, CM(3:1)=100, the remote loopback is initiated from the near end.

In both cases, the data that is looped back will be the data applied to the near end device (see Figure:1).

All modes are selectable via CM(3:1) either directly via pins or via the microprocessor interface. All the diagnostic modes, including remote loop-back and local loop-back are selectable individually for each main and maintenance channel via the microprocessor interface.

#### **Full-Duplex**

In the full-duplex configuration, the RCLK clock of both devices track the average frequency of the corresponding TCLK clock of the opposite end of the link. The receiving Digital-Phase-Lock Loop (DPLL) system makes periodic adjustments to the RCLK clock to ensure that the average frequency is exactly the same as the far-end TCLK clock. In summary, each TCLK is an independent master clock and each RCLK a slave of the far-end TCLK clock.

The relationship between TmCLK and RmCLK are treated similarly.

#### **Full-Duplex Slave**

In slave mode, the TCLK and RCLK clock is derived from the TCLK clock of the far-end modem, such that their average frequencies are identical. Clearly, it is essential that only one modem within a communicating pair is configured in slave mode. The CKC pin should be forced to GND, so that TCLK is always configured as an output.

The relationship between TmCLK and RmCLK are treated similarly. The CKM pin should be forced to GND, so that TmCLK is always configured as an output.

#### **Full-Duplex Master**

In master mode, the local RCLK clock is internally generated from the local TCLK clock. The local TCLK clock may be internally or externally generated. Master mode is only valid if the far-end device is configured in slave mode or if the far-end TCLK clock is derived from the far-end RCLK clock. Only one modem within a communicating pair may be configured as a master.

The relationship between TmCLK and RmCLK are treated similarly.

#### Local Loopback

In local loopback mode, TPN and TmD data is looped back inside the near-end modem and is output at its own RPN and RmD outputs.

Data received from the far-end device is ignored, except to maintain lock. If concurrent requests occur for local and remote loopback, local loopback is selected. The local loopback diagnostic mode is used to test data flow up to, and back from, the local ACS4110 and does not test the integrity of the link itself. Therefore, local loopback operates independently of synchronisation with a second modem (i.e. DCD may be High or Low). The local

loopback test can be initiated via the microprocessor interface (in all microprocessor modes), giving independent control for each channel. All channels can be simultaneously initiated into local loopback when the microprocessor mode is disabled via the CM(3:1) pins.

#### **Remote Loopback**

In remote loopback mode, both modems are exercised completely, as well as the Lasers/LEDs and the fiber optic link. The remote loopback test is normally used to check the integrity of the entire link from the near-end (initiating modem).

Whilst a device is responding to a request for remote loopback from the far-end, requests from the nearend to initiate remote loopback will be ignored.

The remote back request can be initiated by either the near end modem (the near-end modem sends a request to the far-end modem to loopback its received data) or by the far end modem itself. In both cases the far end modem loops back the received data to the near end.

The remote loopback test can be initiated via the microprocessor interface (in all microprocessor modes), giving independent control for each channel. All channels can be simultaneously initiated into remote loopback when the microprocessor mode is disabled via the CM(3:1) pins.

#### **Maintenance channel**

The ACS4110 offers up to 2 synchronous maintenance channel consisting of the following signals:

Transmit Side

| TMD1  | transmit NRZ data/framing             |

|-------|---------------------------------------|

| TMD2  | transmit NRZ data/framing             |

| TmCLK | transmit clock (internal or external) |

Receive Side

| RMD1  | receive NRZ data/framing |

|-------|--------------------------|

| RMD2  | receive NRZ data/framing |

| RmCLK | receive clock            |

#### **Maintenance Data Rate Selection**

The data rate can be selected via the maintenance data rate selection bits MSEL(3:1), either directly via pins or via the microprocessor interface.

TMD1/RMD1 and TMD2/RMD2 support up to 256kbps synchronous data synchronised to TmCLK/RmCLK. They can be used as two independent channels giving a total available bandwidth to 512kbps.

Alternatively, TMD1 or TMD2, together with a specific data rate selection, can be used to divide the bandwidth of the remaining maintenance channel into subchannels with a certain data rate, defined in Table 7.

| MSEL(3:1)              | Data Rate (kbps)           |

|------------------------|----------------------------|

| 101                    | 8                          |

| 100                    | 16                         |

| 011                    | 32                         |

| 010                    | 64                         |

| 001                    | 128                        |

| 000                    | 256                        |

|                        |                            |

| Table 7: Maintenance C | hannel Data Rate Selection |

For example: 4 x 16kbps maintenance channels. select MSEL(3:1) = 010, total available bandwidth on TMD1 is 64kbps and frame every 4th bit. The "framing" channel TMD2 is bit locked to the data channel TMD1.

#### **Diagnostic Modes and Configuration**

The diagnostic and configuration modes available for the main channels are also available for the maintenance channels. CM(3:1) also controls the maintenance channels, while all modes including remote loopback and local loopback are also selectable individually via the microprocessor interface.

#### **Transmit and Receive Clock**

The ACS4110 gives the choice between internally or externally generated TmCLK under the control of the CKM pin. When the CKM pin is held Low, TmCLK is configured as an output producing a clock at the data rate determined by MSEL(3:1). When the CKM pin is held High, TmCLK is configured as an input, and will accept an externally produced transmission clock at the data rate determined by MSEL(3:1).

Input data appearing on the TMD1/2 inputs is latched into the device on either the rising or falling edge of the TmCLK clock depending on the setting of TRSEL. This data appears at the RMD1/2 outputs of the farend modem on the rising or falling edge of the RmCLK clock depending on the setting of RESEL (*see Figure 21. Timing diagrams*). To ensure that the average receive frequency is the same as the transmitted frequency, RmCLK is generated from a Digital Phase-Lock Loop (DPLL) system.

Whilst the TMD1/RMD1 and TMD2/RMD2 maintenance channels have a fixed phase relationship with each other, they do not have a fixed phase relationship with the main TPOS/TNEG data transmission channels.

TmCLK and the reference clock for the (digital) clock recovery and de-jittering PLLs (DPLL) for RmCLK are derived digitally from the system clock for 256kbps by the division factors shown in Table 8. If lower data rates than 256kbps are selected, the 256kHz clock will be divided down by a factor 2/4/8/ 16/32 determined by MSEL(3:1).

| Mode                                                                                | FSys/256 kbps |

|-------------------------------------------------------------------------------------|---------------|

| 16 x T1                                                                             | 271.40625     |

| 16 x E1                                                                             | 264           |

| 7 x T2                                                                              | 271.21875     |

| 4 x E2                                                                              | 264           |

| 1 x E3                                                                              | 268.5         |

| 1 x T3                                                                              | 262.125       |

| 1 x OC1                                                                             | 303.75        |

| Table 8:System Clock Division Factors for<br>Maintenance Clock Generation (256kbps) |               |

#### **ERRC and ERRL - Error Detection**

These signals can be used to give an indication of the quality of the optical link. Even when a DC signal is applied to the data, maintenance and TCLK inputs, the ACS411CS modem transmits data over the link in each direction at the Fsys system frequency. This transmit and control data is used to maintain the timing and synchronisation.

The transmit and control data is constantly monitored to make sure it is compatible with the 8B10B format. If a coding error is detected ERRL will go High and will remain High until reset. ERRL may be reset by asserting PORB, or by removing the fiber optic cable from one side of the link thereby forcing the device temporarily out of lock.

ERRC produces a pulse on detection of each coding error. These pulses may be accumulated by means of an external electronic counter. In the microprocessor modes, the value on an internal accumulating 8 bit counter can be read via the bus interface address 0x1D.

Please note that ERRL and ERRC detect 8B10B coding errors and not data errors, nevertheless because of the complexity of the coding rules employed on the ACS411CS, the absence of detected errors on these pins will give a good indication of a high quality link.

#### **Microprocessor Interface**

#### **Bus Interface Mode Selection**

The ACS4110 incorporates an 8-bit parallel microprocessor bus interface, which can be configured for the following modes via the bus interface mode control pins UPSEL(3:1) as defined in Table 9.

| UPSEL(3:1                                                                            | ) Mode                                                                   | Description                                                                                                                                                                                       |

|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 111 (7)<br>110 (6)<br>101 (5)<br>100 (4)<br>011 (3)<br>010 (2)<br>001 (1)<br>000 (0) | OFF<br>OFF<br>SERIAL<br>MOTOROLA<br>INTEL<br>MULTIPLEXED<br>EPROM<br>OFF | Interface disabled<br>Interface disabled<br>Serial uP bus interface<br>Motorola interface<br>Intel compatible bus interface<br>Multiplexed bus interface<br>EPROM read mode<br>Interface disabled |

| Table 9                                                                              | : Microprocessor                                                         | Interface Mode Selection                                                                                                                                                                          |

Note: Bit 0 is the least significant bit for all modes used here, and the byte structure complies to little endian format (byte 0 is least significant and stored at lowest address).

In OFF Mode, the bus interface is disabled. Control of the device is solely via I/O pins. This will result in limited programmability, as for example individual set-ups for remote loop-back and local loop-back for each channel are not possible, only a collective one. In this mode, all BUS I/O pins are tri-stated or used as additional input pins (ie. POL(3:1), CKLOCAL).

#### **EPROM mode**

The EPROM mode (UPSEL = 1) enables the device to read its set-up from a memory device. An internal state machine controls the access to the memory. All addresses in the memory map are read, and the device is set up according to the corresponding data. The access time is scaled to interface with the AMD AM27C020 at lowest speed (250ns) specification.

The valid read addresse 0, 0xAA is used to check if a memory device is actually attached to the device. If no memory is attached, the bus interface reverts to the default OFF mode. All other read addresses are not valid. The bus interface pins used in EPROM mode are defined in Table 10.

| Pin     | Dir | Description                          |

|---------|-----|--------------------------------------|

| CSB     | 0   | Active low chip select/output enable |

| A(4:0)  | 0   | Address output to EPROM              |

| AD(7:0) | I   | Data input from EPROM                |

Table 10: uP Bus Interface Pins for EPROM mode.

#### MULTIPLEXED mode

The MULTIPLEXED mode (UPSEL = 2) enables the ACS4110 to interface with a microprocessor using a combined multiplexed address/data bus. The bus interface pins are defined in Table 11.

| Pin                                        | Dir                   | Description                                                                                                                        |

|--------------------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------|

| CSB<br>ALE<br>RDB<br>WRB<br>AD(7:0)<br>RDY | <br> <br> <br> 0<br>0 | Active low chip select<br>Address latch enable<br>Active low read enable<br>Active low write enable<br>Address / Data bus<br>Ready |

| Table 11:                                  | uP Bus Interface      | e Pins for MULTIPLEXED mode.                                                                                                       |

#### INTEL mode

The INTEL mode (UPSEL = 3) enables the ACS4110 to interface with a Intel 80x86 type microprocessor bus. The bus interface pins used are defined in Table 12.

| Pin                                           | Dir              | Description                                                                                                     |

|-----------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------|

| CSB<br>RDB<br>WRB<br>A(4:0)<br>AD(7:0)<br>RDY | <br> <br> <br> 0 | Active low chip select<br>Active low read enable<br>Active low write enable<br>Address bus<br>Data bus<br>Ready |

| ( )                                           | I<br>IO<br>O     |                                                                                                                 |

| Table 40. UDI                                 |                  |                                                                                                                 |

Table 12:

uP Bus Interface Pins for INTEL mode.

#### **MOTOROLA mode**

The MOTOROLA mode (UPSEL = 4) enables the ACS4110 to interface with a Motorola 680x0 type microprocessor bus. The bus interface pins used are defined in Table 13.

| Pin                                    | Dir              | Description                                                                                                                     |

|----------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------|

| CSB<br>WRB<br>A(4:0)<br>AD(7:0)<br>RDY | <br> <br> 0<br>0 | Active low chip select<br>Read / write bar select<br>Address bus<br>Data bus<br>Active low data transfer<br>acknowledge (DTACK) |

|                                        |                  |                                                                                                                                 |

Table 13:

uP Bus Interface Pins for MOTOROLA mode.

#### SERIAL mode

The SERIAL mode (uPSEL = 5) enables the ACS4110 to interface with a serial microprocessor bus. The bus interface pins are defined in Table 14.

| Pin                | Dir       | Description                                                                                    |

|--------------------|-----------|------------------------------------------------------------------------------------------------|

| CSB<br>ALE<br>A(1) | <br> <br> | Active low chip select<br>= SCLK: Serial interface clock<br>= CLKE: Active SCLK edge selection |

| A(0)<br>AD(0)      | l<br>O    | control bit<br>= SDI: Serial data input<br>= SDO: Serial data output                           |

Table 14: uP Bus Interface Pins for SERIAL mode.

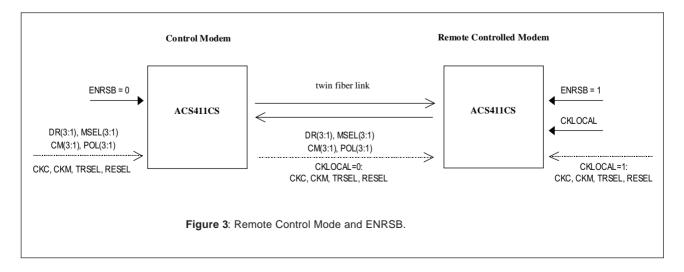

#### **Remote Control**

The device setup of one modem can be over-ridden with the device set up from the other modem when remote control is enabled from the ENRSB pin. To enable remote control mode, ENRSB pin is held Low (Logic 0). If a modem is set up in remote control, the data from the control modem overides the local microprocessor interface or pin set-up of the remote controlled modem. The signals that will be over-ridden are defined in Table 15.

| Name                                                                        | Description                                                                                                                                                                                                                                                                                                            |  |

|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ch_enb(16:1                                                                 | ) Channel enable defined in local microprocessor<br>for individual channel setup                                                                                                                                                                                                                                       |  |

| DR(3:1)<br>POL(3:1)<br>CM(2:1)<br>TRSEL<br>RESEL<br>CKM<br>CKC<br>MSEL(3:1) | Data rate select<br>Line code polarity select<br>Configuration mode(full-duplex/master/slave)<br>Clock edge select for transmit clocks<br>Clock edge select for receive clocks<br>Clock direction select maintenance channel<br>Clock direction select main channels(combined)<br>Maintenance channel data rate select |  |

| Tal                                                                         | ble 15: Remote Control Device Setup.                                                                                                                                                                                                                                                                                   |  |

Remote control is only possible in one direction (only one modem allowed with ENRSB = 0).

The near-end modem has to be setup as the control device (ENRSB=0) in order to configure the far-end by remote control. If both modems are setup as control devices (ENRSB=0), data transmission and reception will be disabled.

When in remote setup, the signal CKLOCAL selects whether the Tx/Rx clock settings (CKC, CKM, RESEL, TRSEL, trsel\_m and resel\_m) should be taken from the controlling device (CKLOCAL=0) or locally (CKLOCAL=1).

The diagram in Figure 1 shows the configurations in Remote Control mode.

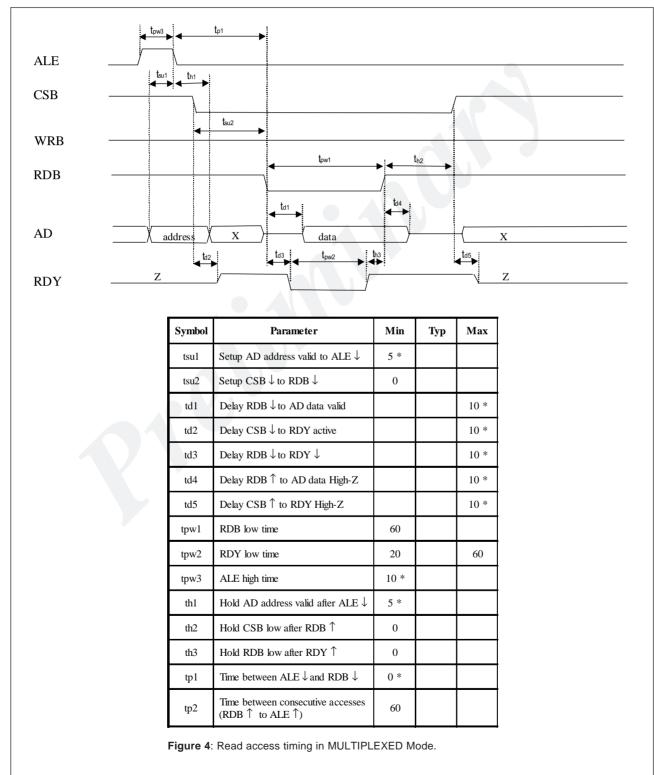

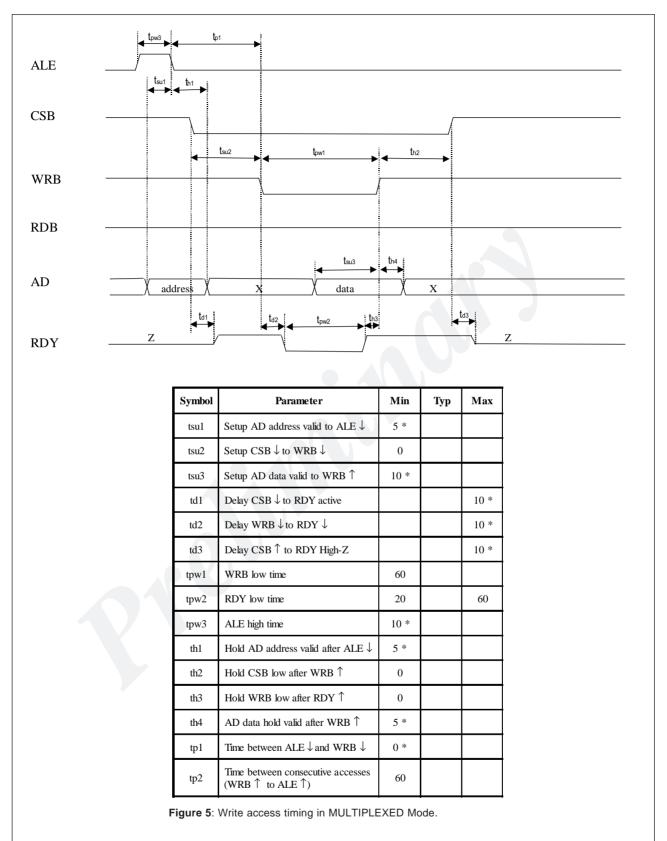

### uP Interface timing - MULTIPLEXED mode

In MULTIPLEXED mode, the device is configured to interface with a microprocessor using a multiplexed address/data bus. The following figures show the timing diagrams of write and read accesses for this mode.

The RDY low time Trdy is at least 2 CLKX cycles after WRB/RDB going low.

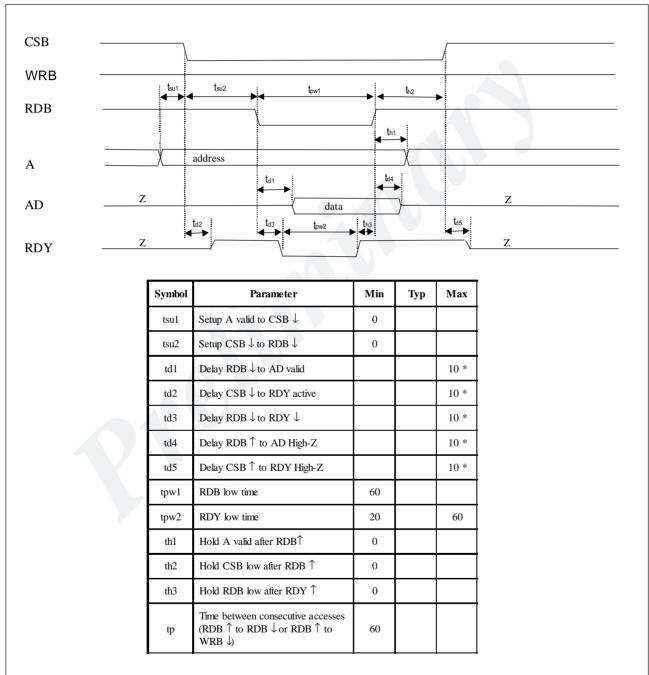

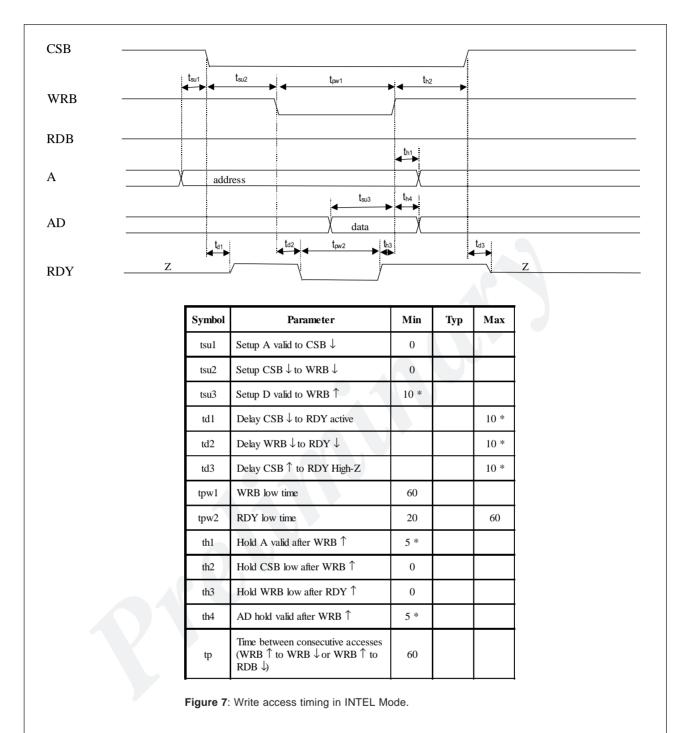

### uP Interface timing - INTEL mode

In INTEL mode, the device is configured to interface with a microprocessor using a 80x86 type bus. The following figures show the timing diagrams of write and read accesses for this mode.

The RDY low time Trdy is at least 2 CLKX cycles after WRB/RDB going low.

Figure 6: Read access timing in INTEL Mode.

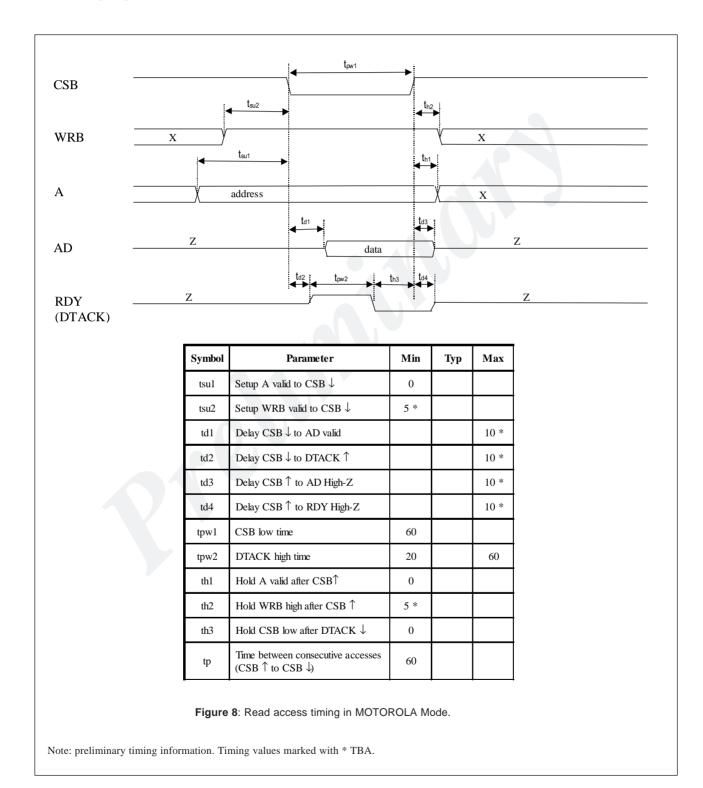

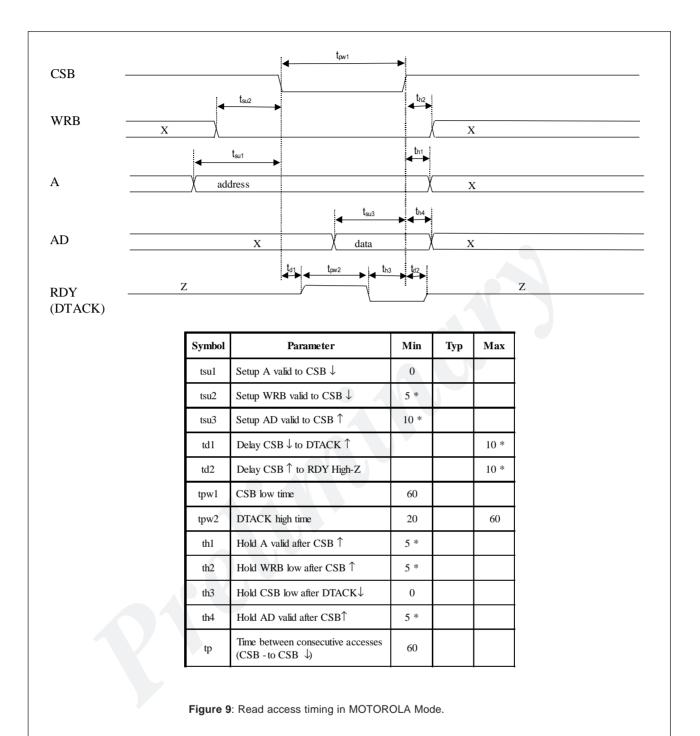

### uP Interface timing - MOTOROLA mode

In MOTOROLA mode, the device is configured to interface with a microprocessor using a 680x0 type bus. The following figures show the timing diagrams of write and read accesses for this mode.

The Dtack high time Trdy is at least 2 CLKX cycles after CSB going low.

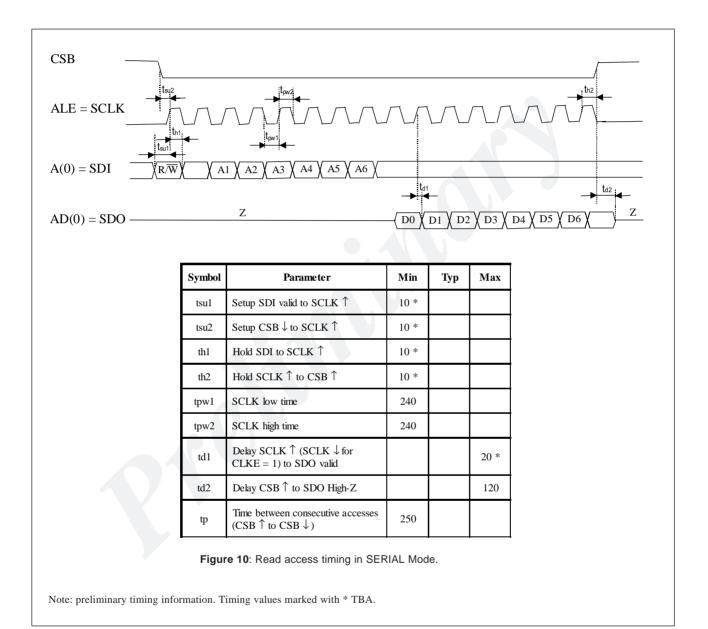

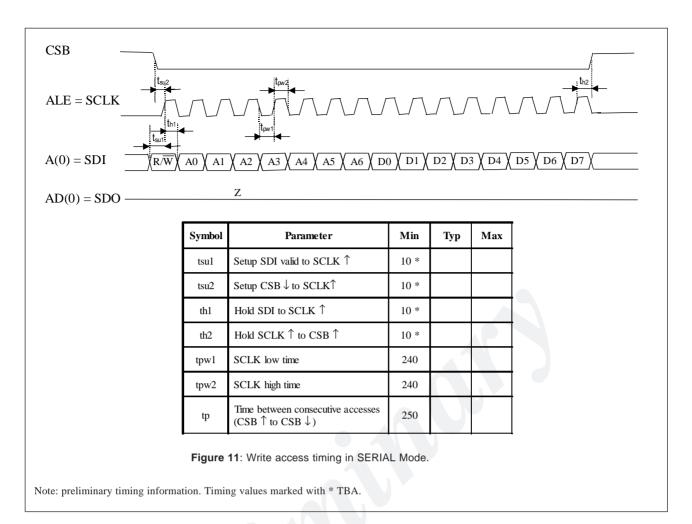

#### uP Interface timing - SERIAL mode

In SERIAL mode, the device is configured to interface with a serial microprocessor bus. The following figures show the timing diagrams of write and read accesses for this mode.

During read access the output data sdo (AD(0)) is clocked out on the rising edge of SCLK (ALE) when the active edge selection control bit CLKE (A(1)) is

0, and on the falling edge when CLKE is 1. Address, read/write control bit and write data are always clocked into the interface on the rising edge of SCLK.

Both input data sdi and clock SCLK are oversampled , filtered and synchronized to the system clock CLKX.

The serial interface clock (SCLK) is not required to run when no access is performed (CSB = 1).

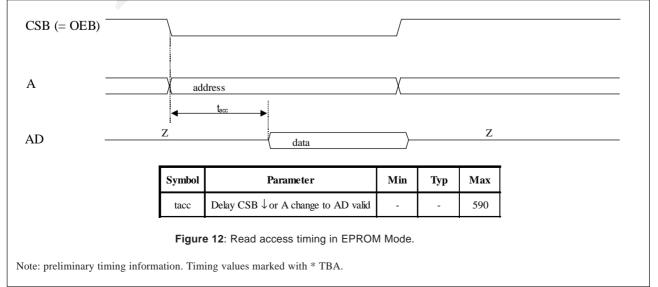

#### uP Interface timing - EPROM mode

In EPROM mode, the ACS4110 takes control of the bus as master, and reads the device set-up from an AMD AM27C020 type EPROM at lowest speed (250ns) after device start-up (system reset). The EPROM access state machine in the up interface sequences the accesses. The following figures show the timing diagrams of the read access for this mode.

For a more detailed timing specification, see AMD Am27C020 data sheet, July 1993, p. 2-95.

If the microprocessor interface is enabled (UPSEL / = 0), the default start-up values are taken over from the pin values as default during reset for the following control pins:

CM(3:1)

CKC, CKM, TRSEL , RESEL

MSEL(3:1), ENRSB

DR(3:1)

#### **Memory Map**

Table 15 shows the memory map of the ACS4110. The location names are chosen to match the corresponding pin names. Signals not directly equivalent to pins are in lower case.

The device identification number id<7:0> on address 0x00 is used in EPROM mode to check if an external memory device is connected. The value to be programmed is 0xAA.

The whole chip set-up except DR<3:1> can be controlled individually for each channel.

The error counter errc<7:0> (address 0x1D) is an 8-bit saturating counter for the ERRC error pulse. A write of a 0x00 mask to this address clears the counter to 0x00.

The status signals ERRL, fail\_ne, fail\_fe can also be cleared by writing a 0 to the specific bit in the address. For example, writing a mask of 0xDF to address 0x1C clears the ERRL signal, but leaves other status signals unchanged.

If the microprocessor interface is enabled (UPSEL /= 0), the default start-up values of all control bits except POL(3:1) and CKLOCAL are taken over from the pin values as default during reset.

| Address      | Bit      | Access     | Name            | Description                                                                               |

|--------------|----------|------------|-----------------|-------------------------------------------------------------------------------------------|

| 0x00         | 7-0      | R          | id<7:0>         | Device identification number.                                                             |

| 0x01         | 7-0      | R/W        | ch_enb<8:1>     | Channel enable (active low) for channels 1 to 8.                                          |

| 0x02         | 7-0      | R/W        | ch_enb<16:9>    |                                                                                           |

| 0x03         | 7-0      | R/W        | cm1<8:1>        | Configuration mode CM bit 1 for channels 1 to 8.                                          |

| 0x04         | 7-0      | R/W        | cm1<16:9>       | Configuration mode CM bit 1 for channels 9 to 16.                                         |

| 0x05         | 7-0      | R/W        | cm2<8:1>        | Configuration mode CM bit 2 for channels 1 to 8.                                          |

| 0x06         | 7-0      | R/W        | cm2<16:9>       | Configuration mode CM bit 2 for channels 9 to 16.                                         |

| 0x07         | 7-0      | R/W        | cm3<8:1>        | Configuration mode CM bit 3 for channels 1 to 8.                                          |

| 0x08         | 7-0      | R/W        | cm3<16:9>       | Configuration mode CM bit 3 for channels 9 to 16.                                         |

| 0x09         | 7-0      | R/W        | pol1<8:1>       | Line code polarity POL bit 1 for channels 1 to 8.                                         |

| 0x0A         | 7-0      | R/W        | pol1<16:9>      | Line code polarity POL bit 1 for channels 9 to 16.                                        |

| 0x0B         | 7-0      | R/W        | pol2<8:1>       | Line code polarity POL bit 2 for channels 1 to 8.                                         |

| 0x0C         | 7-0      | R/W        | pol2<0.19       | Line code polarity POL bit 2 for channels 9 to 0.                                         |

| 0x0D         | 7-0      | R/W        | pol2<10.5>      | Line code polarity POL bit 2 for channels 5 to 10.                                        |

| 0x0E         | 7-0      | R/W        | pol3<16:9>      | Line code polarity POL bit 3 for channels 9 to 0.                                         |

| 0x0E<br>0x0F | 7-0      | R/W        | ckc<8:1>        | Clock direction select for channels 1 to 8.                                               |

| 0x10         | 7-0      | R/W        | ckc<16:9>       | Clock direction select for channels 9 to 3.                                               |

| 0x10<br>0x11 | 7-0      | R/W        | trsel<8:1>      | Transmit clock edge select for channels 1 to 8.                                           |

| 0x12         | 7-0      | R/W<br>R/W | trsel<16:9>     | Transmit clock edge select for channels 9 to 16.                                          |

| 0x12<br>0x13 | 7-0      | R/W<br>R/W | resel<8:1>      |                                                                                           |

| 0x15<br>0x14 | 7-0      | R/W<br>R/W | resel<16:9>     | Receive clock edge select for channels 1 to 8.                                            |

|              |          |            | 16861<10.9>     | Receive clock edge select for channels 9 to 16.                                           |

| 0x15         | 7        | -<br>D /W/ |                 | Confirmation and CM for maintenance shows 1                                               |

|              | 6-4      | R/W        | cm_m<3:1>       | Configuration mode CM for maintenance channel.                                            |

|              | 3        | R/W        | CKLOCAL         | Local Tx/Rx CLK setup in remote control mode                                              |

|              | 2        | R/W        | CKM             | Clock direction select maintenance channel.                                               |

|              | 1        | R/W        | trsel_m         | Transmit clock edge select for maintenance channel.                                       |

| 0-16         | 0        | R/W        | resel_m         | Receive clock edge select for maintenance channel.                                        |

| 0x16         | 7<br>6-4 | -<br>D/W/  | MSEL<3:1>       | Maintenance channel data rate select.                                                     |

|              |          | R/W        |                 |                                                                                           |

|              | 3        | R/W        | ENRSB           | Enable remote control setup.                                                              |

| 0 17         | 2-0      | R/W        | DR<3:1>         | Data rate select.                                                                         |

| 0x17         | 7-0      | R          | $rl_det < 8:1>$ | Near-end remote loop-back detect channels 1 to 8.                                         |

| 0x18         | 7-0      | R          | rl_det<16:9>    | Near-end remote loop-back detect channels 9 to 16.                                        |

| 0x19         | 7-0      | R          | $ll_det < 8:1>$ | Far-end local loop-back detect channels 1 to 8.                                           |

| 0x1A         | 7-0      | R          | ll_det<16:9>    | Far-end local loop-back detect channels 9 to 16.                                          |

| 0x1B         | 7-2      | -<br>D     |                 | Normand months loop hash data the maintenance shows                                       |

|              | 1        | R          | rlm_det         | Near-end remote loop-back detect for maintenance channel                                  |

| 0x1C         | 0<br>7   | R          | llm_det         | Far-end local loop-back detect for maintenance channel.<br>Data carrier detect status.    |

| UXIC         |          | R          | DCD             |                                                                                           |

|              | 6        | R          | LOSS            | Loss of signal status.                                                                    |

|              | 5        | R/W        | ERRL            | Error latch.                                                                              |

|              | 4        | -          | C '1            |                                                                                           |

|              | 3        | R/W        | fail_ne         | Alarm indication for near-end receive fail.<br>Alarm indication for far-end receive fail. |

|              | 2        | R/W        | fail_fe         |                                                                                           |

|              | 1        | R          | resync_ne       | Near-end device has entered re-synchronization.                                           |

| 0.1D         | 0        | R          | resync_fe       | Far-end device has entered re-synchronization.                                            |

| 0x1D         | 7-0      | R/W        | errc<7:0>       | 8-bit saturating error counter (reset by write).                                          |

| 0x1E         | 7-0      | R/W        | tm<7:0>         | Test mode select.                                                                         |

| 0x1F         | 7-0      | -          |                 |                                                                                           |

#### Table 15: Memory Map

#### Laser/LED Considerations

Since LEDs or Lasers from different suppliers may emit different wavelengths, it is recommended that the Lasers/LEDs in a communicating pair of modems are obtained from the same supplier. Acapella will assist with contact names and addresses on request.

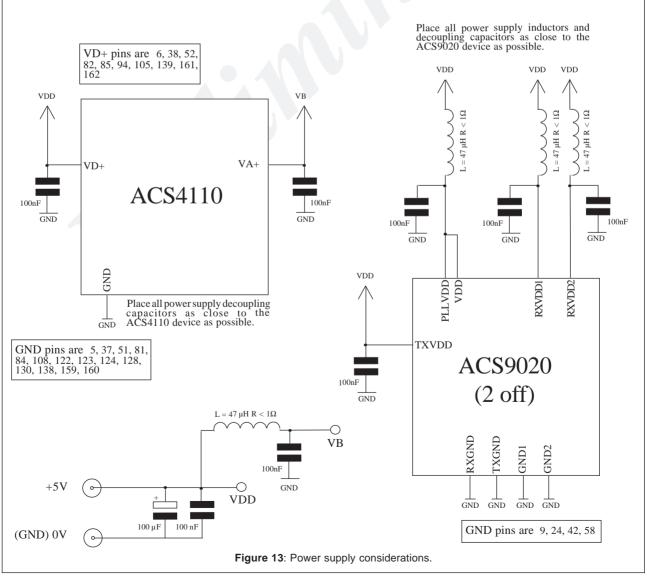

#### **Power Supply Decoupling**

The ACS9020 contains a highly sensitive amplifier, capable of responding to extremely low current levels. To exploit this sensitivity it is important to reduce external noise to a low level compared to the input signal from the Laser/LED. The modem should have an independent power trace to the point where power enters the board.

The Laser/LED should be sited very close to the PMN, PINP, PINN, LAN and LAP pins. A generous ground plane should be provided, especially surrounding the sensitive PINP and PINN tracks from the ACS9020 pins to the optical component. The modem should be protected from EMI/RFI sources in the standard ways.

#### LOSS (Loss Of Synchronisation)

There are two conditions that will make LOSS go to Logic 1. These are:

i) Loss of synchronisation - synchronisation windows incorrectly aligned i.e DCD=0.

ii) 64 received symbols break the 8B10B encoding rules in a sequence of 256 symbols.

In order to return LOSS to the Logic 0 state the following criteria must be met:

i) The devices must be synchronised - synchronisation windows correctly aligned i.e DCD=1.

ii) There are no received symbols in a sequence of 256 symbols which break the 8B10B coding rules.

#### Link Budgets

The link budget is the difference between the power coupled to the fiber via the transmit Laser/LED and the power required to realise the minimum inputamplifier current via the receive PIN/LED. The link budget is normally specified in dB, and represents the maximum attenuation allowed between communicating Lasers/LEDs. The budget is utilised in terms of the cable length, cable connectors and splices. It usually includes an operating margin to allow for degradation in LASER/LED performance. The power coupled to the cable is a function of the efficiency of the Laser/LED, the current applied to the Laser/LED and the type of the fiber optic cable employed.

#### Twin Fiber LED link (880nm LED + PIN)

#### Link Budget Example (Rtset set so LED launch current = 100 mA peak)

#### Fiber type Glass (multimode) Fiber size 62.5micron

| Minimum transmit couple power to fiber ( $\mu W$ )        | 100  |

|-----------------------------------------------------------|------|

| Minimum PIN responsivity (A/W)                            | 0.1  |

| Minimum ACS9020 sensitivity (nA)                          | 1500 |

| Minimum input power to ACS9020 amplifier ( $\mu$ W)       | 20   |

| Link budget (dB) (multi mode fiber attenuation = 3 dB/km) | 8.24 |

#### Twin Fiber LASER link (1310nm Laser and PIN)

#### Link Budget Example (Rtset set so LASER launch current = 25 mA peak)

| Fiber type Glass (single mode)<br>Fiber size 9 micron                   |      |

|-------------------------------------------------------------------------|------|

| Minimum transmit couple power to fiber ( $\mu W$ )                      | 1000 |

| Minimum PIN responsivity (A/W)                                          | 0.8  |

| Minimum ACS9020 sensitivity (nA)                                        | 1500 |

| Minimum input power to ACS9020 amplifier ( $\mu W$ )                    | 4    |

| Link budget (dB) (single mode fiber attenuation = $0.3 \text{ dB/km}$ ) | 27   |

#### Single Fiber LASER link (1310nm and 1510nm WDM device)

#### **Link Budget Example** (Rtset set so LASER launch current = 25 mA peak)

| Fiber type Glass (single mode)<br>Fiber size 9 micron                   |      |

|-------------------------------------------------------------------------|------|

| Minimum transmit couple power to fiber ( $\mu W$ )                      | 1000 |

| Minimum PIN responsivity (A/W)                                          | 0.8  |

| Minimum ACS9020 sensitivity (nA)                                        | 1500 |

| Minimum input power to ACS9020 amplifier ( $\mu$ W)                     | 4    |

| Link budget (dB) (single mode fiber attenuation = $0.3 \text{ dB/km}$ ) | 27   |

Figure 14: Link bugdet examples.

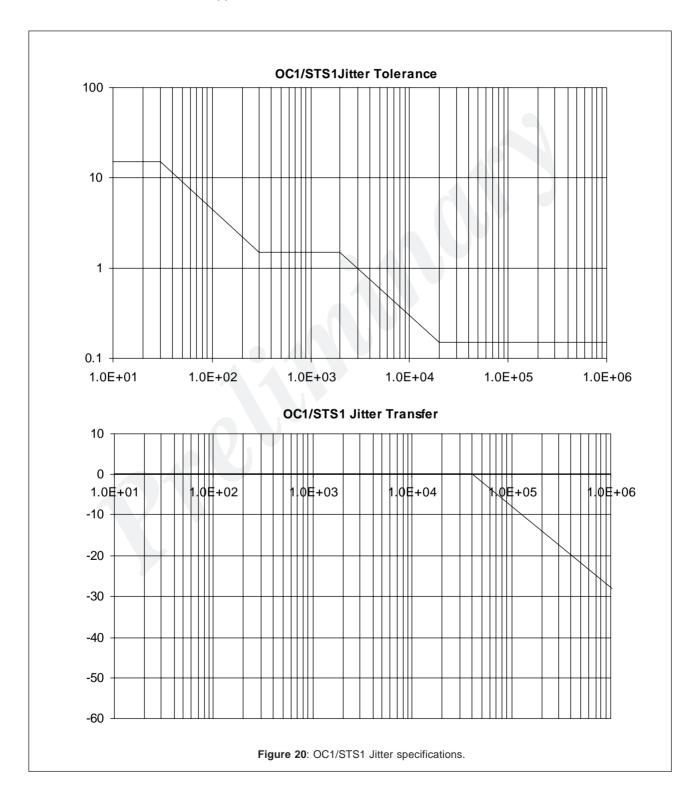

#### **Jitter Characteristics**

The receive path includes a Phase Locked Loop block, which provides an independent PLL for each transmission channel. The purpose of each PLL is to regenerate the clock signal such that it tracks the transmit clock of the far end modem. The PLL will also attenuate the jitter present in the received data stream. For E1, E2, T1 and T2 modes, the PLL algorithm implemented is entirely digital. For E3, T3 and OC1/ STS1 modes, the PLL block utilised a mixed signal PLL algorithm. The mixed signal PLL does not require the use of external tuning components. The dynamic range of all PLL algorithms is +/- 500ppm. The dynamic range is used to accommodate oscillator frequency differences between the two communicating modems, as well as any jitter and wander present in the received data stream.

The jitter characteristics for the ACS4110 is independent of the binary content of the transmitted data stream.

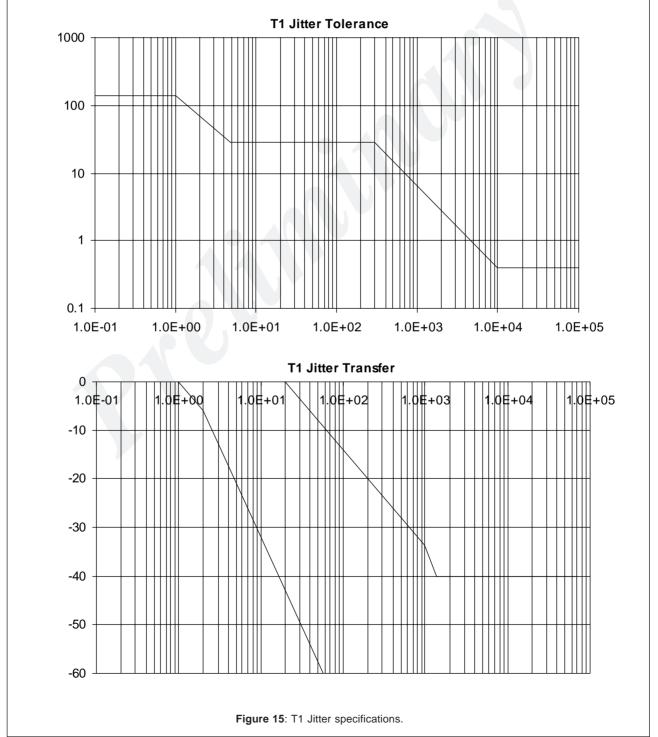

#### **T1 Jitter specification**

When configured for T1 operation, the Jitter Tolerance and Jitter Transfer performance conforms to that specified in AT&T Publication 62411.

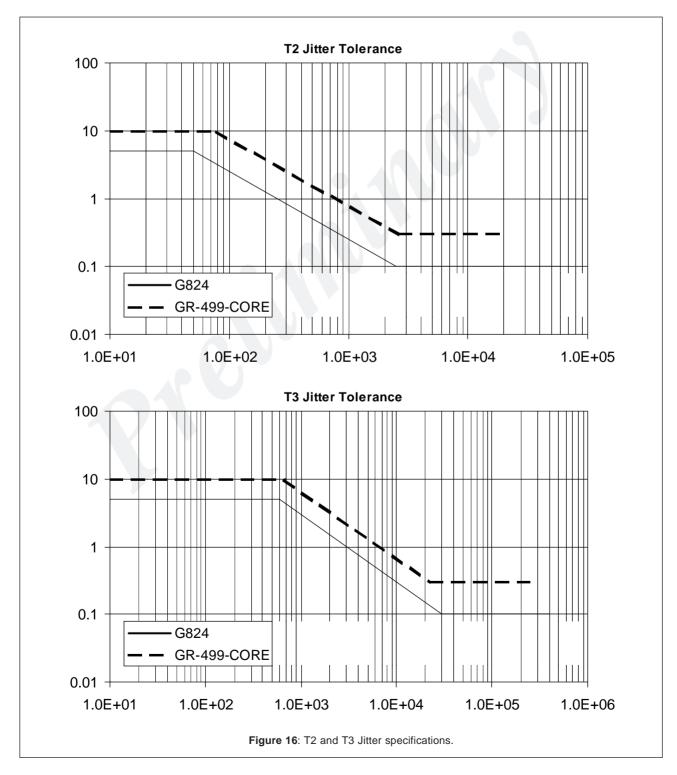

# T2 and T3 Jitter specification

When configured for T2 operation, the Jitter Tolerance performance exceeds that specified in both ITU-T G.824 and Bellcore GR-499-CORE.

When configured for T3 operation, the Jitter Tolerance performance exceeds that specified in both ITU-T G.824 and Bellcore GR-499-CORE.

In the absence of input jitter, the output jitter generated from the mixed signal PLL after band pass filtering from 12kHz to 400kHz is 0.07UIpp.

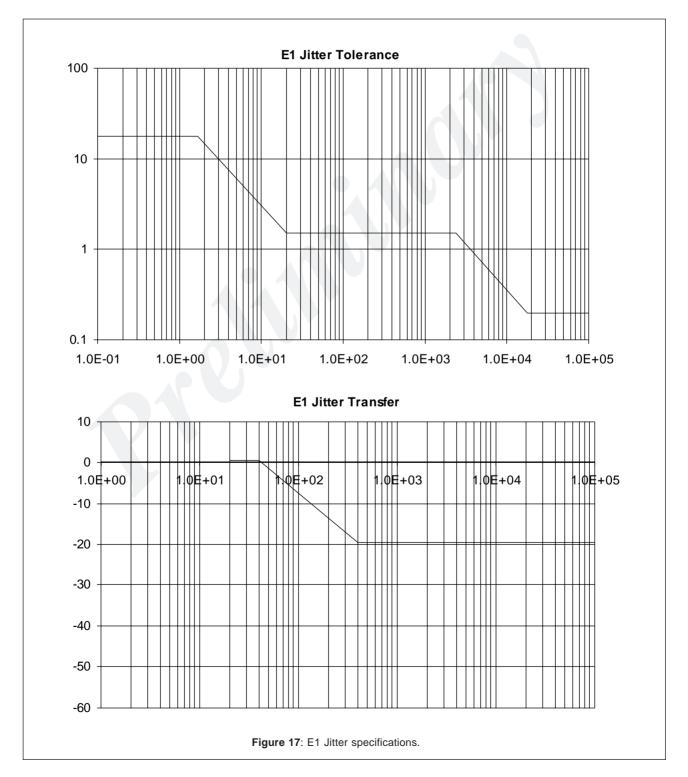

## E1 Jitter specification

When configured for E1 operation, the Jitter Tolerance performances exceeds that specified in ITU-T G.823. The Jitter Transfer performance exceeds that specified in ITU-T G.736.

With reference to ITU-T G.736, section 6.1.3; in the case where the timing signal is derived from an incoming 2048kbit/s signal having no jitter, the output jitter should not exceed 0.10 UIpp when it is measured in the frequency range 20Hz to 100kHz.

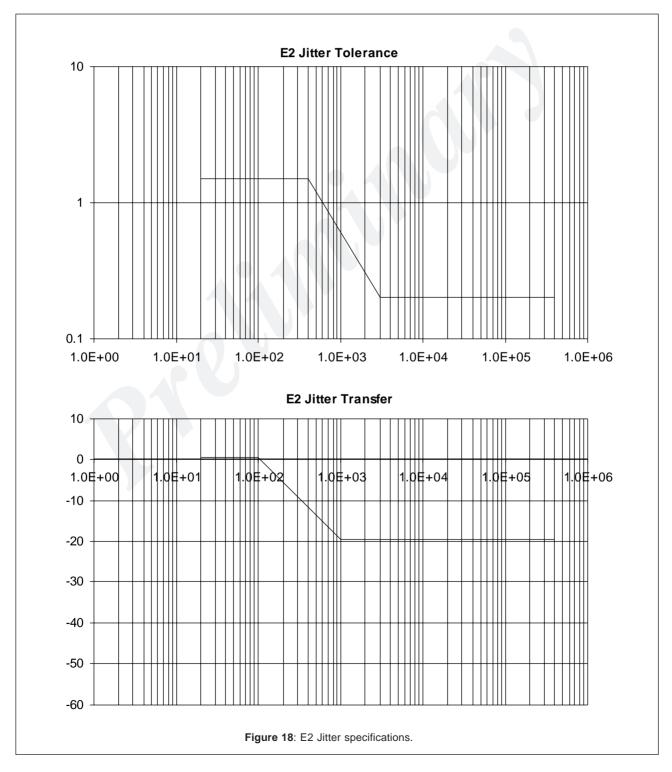

# E2 Jitter specification

When configured for E2 operation, the Jitter Tolerance performance exceeds that specified in ITU-T G.823.

In the absence of input jitter, the output jitter generated from the Digital PLL for E2 operation is:

Frequency band Output Jitter

20Hz to 400kHz 80kHz to 400kHz 0.7Ulpp 0.09Ulpp

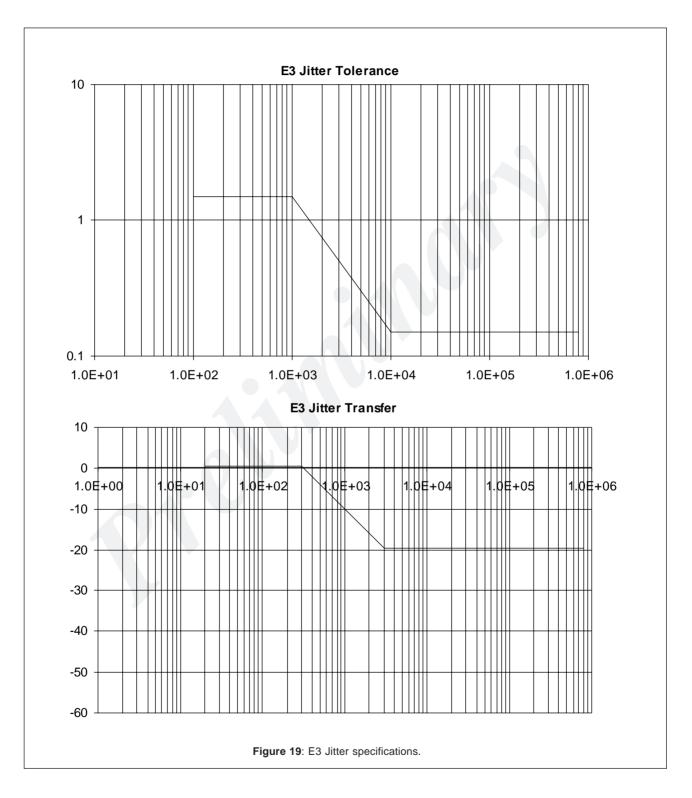

# E3 Jitter specification

When configured for E3 operation, the Jitter Tolerance performance exceeds that specified in ITU-T G.823.

Output Jitter Generation after band pass filtering 10 kHz to 800kHz.

# OC1/STS1 Jitter specification

When configured for OC1/STS1 operation, the Jitter Tolerance and Jitter Transfer performance exceeds the requirements specified in Bellcore GR-253-CORE.

In the absence of input jitter, the output jitter generated from the mixed signal PLL after band pass filtering from 12kHz to 400kHz is 0.07UIpp.

ACS411CS PRE-RELEASE Issue 6.0 July 1999

32

Pin Description ACS4110 part 1.

| Pin Description ACS4110 part 2. |

|---------------------------------|

|---------------------------------|

| Pin                                                                                            | Sym                                                                                                                                                 | ю | Name                      | Description                                                        |

|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---|---------------------------|--------------------------------------------------------------------|

| 6,38,<br>52,82,<br>85,94,<br>105,139,<br>161,162                                               | VD+                                                                                                                                                 | - | +ve power<br>supply       | Power supply, 4.75 - 5.25<br>Volts.                                |

| 115                                                                                            | VA+                                                                                                                                                 | - | +ve power<br>supply       | Power supply for Clock<br>Recovery PLL, 4.75 - 5.25<br>Volts.      |

| 5, 37,<br>51,81,<br>84,108,<br>122,123,<br>124,128,<br>130,138,<br>159,160                     | GND                                                                                                                                                 | - | Ground                    | Power Supply                                                       |

| 41<br>33<br>27<br>21<br>15<br>9<br>1<br>171<br>165<br>47<br>55<br>61<br>67<br>73<br>79<br>154  | TPOS1<br>TPOS2<br>TPOS3<br>TPOS4<br>TPOS5<br>TPOS6<br>TPOS7<br>TPOS8<br>TPOS9<br>TPOS10<br>TPOS11<br>TPOS12<br>TPOS13<br>TPOS14<br>TPOS15<br>TPOS16 | Ι | Transmit Data<br>Positive | Transmit channel 1-16,<br>corresponds to +ve in bipolar<br>signal. |

| 42<br>34<br>28<br>22<br>16<br>10<br>2<br>172<br>166<br>48<br>56<br>62<br>68<br>74<br>80<br>153 | TNEG1<br>TNEG2<br>TNEG3<br>TNEG4<br>TNEG5<br>TNEG6<br>TNEG7<br>TNEG8<br>TNEG9<br>TNEG10<br>TNEG11<br>TNEG12<br>TNEG13<br>TNEG14<br>TNEG15<br>TNEG16 | I | Transmit Data<br>Negative | Transmit channel 1-16,<br>corresponds to -ve in bipolar<br>signal. |

| 39<br>30<br>24<br>18<br>12<br>4<br>174<br>168<br>158<br>44<br>50<br>58<br>64<br>70<br>76<br>87 | RPOS1<br>RPOS2<br>RPOS3<br>RPOS4<br>RPOS5<br>RPOS6<br>RPOS7<br>RPOS8<br>RPOS9<br>RPOS10<br>RPOS11<br>RPOS12<br>RPOS13<br>RPOS14<br>RPOS15<br>RPOS16 | 0 | Receive Data<br>Positive  | Receive channel 1-16,<br>corresponds to +ve in bipolar<br>signal.  |

| Pin                                                                                            | Sym                                                                                                                                                 | ю   | Name                            | Description                                                                                                                                                                           |  |  |  |

|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 36<br>31<br>25<br>19<br>13<br>7<br>175<br>169<br>163<br>45<br>53<br>59<br>65<br>71<br>77<br>88 | RNEG1<br>RNEG2<br>RNEG3<br>RNEG4<br>RNEG5<br>RNEG6<br>RNEG7<br>RNEG8<br>RNEG9<br>RNEG10<br>RNEG11<br>RNEG12<br>RNEG13<br>RNEG14<br>RNEG15<br>RNEG16 | 0   | Receive Data<br>Negative        | Receive channel 1-16,<br>corresponds to -ve in bipolar<br>signal.                                                                                                                     |  |  |  |

| 131                                                                                            | DCD                                                                                                                                                 | 0   | Data Carrier<br>Detect          | When DCD=1, then the communicating modems have synchronised, and are communicating.                                                                                                   |  |  |  |

| 120<br>121                                                                                     | XTI/<br>XTO                                                                                                                                         |     | System Clock<br>Crystal         | Connect fundamental parallel<br>resonance crystal with<br>appropriate padding capacitor<br>to GND.                                                                                    |  |  |  |

| 129                                                                                            | PORB                                                                                                                                                | Ι   | Power On<br>Reset               | Will initialise the device when<br>PORB= 0. PORB is normally<br>connected to an RC circuit so<br>that a POR is automatically<br>invoked on power-up. PORB=<br>1 for normal operation. |  |  |  |

| 156                                                                                            | TmCLK                                                                                                                                               | I/O | Transmit<br>maintenance<br>CLK  | Transmit maintenance Clock.<br>samples TmD on edge selected<br>by TRSEL control.                                                                                                      |  |  |  |

| 155                                                                                            | RmCLK                                                                                                                                               | 0   | Receive<br>maintenance<br>Clock | Receive maintenance Clock.<br>samples RmD on edge selected<br>by RESEL control.                                                                                                       |  |  |  |

| 116                                                                                            | RESEL                                                                                                                                               | Ι   | Receive Edge<br>Select          | When RESEL = 1,<br>RPOS/RNEG and RmD data is<br>valid on the rising edge of<br>RCLK/RmCLK. When RESEL<br>= 0, the data is valid on the<br>falling edge of RCLK/RmCLK.                 |  |  |  |

| 104                                                                                            | TRSEL                                                                                                                                               | Ι   | Transmit Edge<br>Select         | When TRSEL = 0,<br>TPOS/TNEG and TmD data is<br>latched on the falling edge of<br>TCLK/TmCLK. When TRSEL<br>=1, the data is latched on the<br>rising edge of TCLK/TmCLK.              |  |  |  |