# Contents

## 1. AP2001 Specification

- 1.1 Features

- 1.2 General Description

- 1.3 Pin Assignments

- 1.4 Pin Descriptions

- 1.5 Block Diagram

- 1.6 Absolute Maximum Ratings

### 2. Hardware

- 2.1 Introduction

- 2.2 Typical Application

- 2.3 Input / Output Connections

- 2.4 Schematic

- 2.5 Bill of Material

- 2.6 Board Layout

## 3. Design Procedure

- 3.1 Introduction

- 3.2 Operating Specifications

- 3.3 Design Procedures

- 3.3.1 Selection of the buck inductor (L)

- 3.3.2 Selection of the output capacitor (Cout)

- 3.3.3 Selection of power switch (MOSFET)

- 3.3.4 Selection of power Rectifier (D)

- 3.3.5 Selection of the input capacitor (Cin)

## 4. Voltage monitor by AP434

# Application Note AP2001 Dual Buck Converter

# 1. AP2001 Specification

#### 1.1 Features

- Dual PWM Control Circuitry

- Operating voltage can be up to 50V

- Adjustable Dead Time Control (DTC)

- Under voltage Lockout (UVLO) Protection

- Short Circuit Protection (SCP)

- Variable Oscillator Frequency...... 500Khz Max

- 2.5V voltage reference Output

- 16-pin PDIP and SOP packages

### 1.2 General Description

The AP2001 integrates Pulse-width-Modulation (PWM) control circuit into a single chip, mainly designs for power-supply regulator. All the functions included an on-chip 2.5V reference output, two error amplifiers, an adjustable oscillator, two dead-time comparators, UVLO, SCP, DTC circuitry, and dual common-emitter (CE) output transistor circuit. Recommend the output CE transistors as pre-driver for Driving externally. The DTC can provide from 0% to 100%. Switching frequency can be adjustable by trimming RT and CT. During low VCC situation, the UVLO makes sure that the outputs are off until the internal circuit is operational normally.

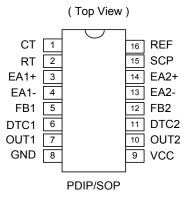

## 1.3 Pin Assignments

# 1.4 Pin Descriptions

| Name | Description                |  |  |

|------|----------------------------|--|--|

| СТ   | Timing Capacitor           |  |  |

| RT   | Timing Resistor            |  |  |

| EA+  | Error Amplifier Input(+)   |  |  |

| EA-  | Error Amplifier Input(-)   |  |  |

| FB   | Feedback Loop Compensation |  |  |

| DTC  | Dead Time Control          |  |  |

| OUT  | Pre-driver Output          |  |  |

| GND  | Ground                     |  |  |

| VCC  | Supply Voltage             |  |  |

| SCP  | Short Circuit Protection   |  |  |

| REF  | Voltage Reference          |  |  |

# Application Note AP2001 Dual Buck Converter

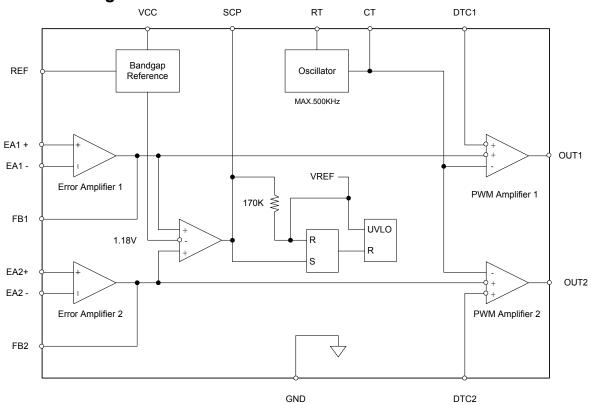

# 1.5 Block Diagram

# 1.6 Absolute Maximum Ratings

| Symbol            | Parameter                                                   | Rating      | Unit |

|-------------------|-------------------------------------------------------------|-------------|------|

| V <sub>CC</sub>   | Supply voltage                                              | 40          | V    |

| Vı                | Amplifier input voltage                                     | 20          | V    |

| Vo                | Collector output voltage                                    | 40          | V    |

| lo                | Collector output current                                    | 21          | mA   |

| T <sub>OP</sub>   | Operating temperature range                                 | -20 to +85  | °C   |

| T <sub>ST</sub>   | Storage temperature range                                   | -65 to +150 | °C   |

| T <sub>LEAD</sub> | Lead temperature 1.6 mm(1/16 inch) from case for 10 seconds | 260         | °C   |

#### 2. Hardware

#### 2.1 Introduction

The dual-buck demo board supply two constant dc output voltage that are 3.3V and 5V. This board can supply output power up to 15W for buck1 output (5V / 3A) and up to 10W for buck2 output (3.3V / 3A). Using a dc input voltage of 10.8 V to 13.2 V, full load efficiency up to 86 percent. This type of converter converts an unregulated input voltage to 2 regulated output voltage that they are always lower than the input voltage. The control method used in the board is fixed frequency, variable on-time pulse-width-modulation (PWM). The feedback method used is voltage-mode control. Other features of the board include undervoltage lockout (UVLO), short-circuit protection (SCP), and adjustable dead time control (DTC).

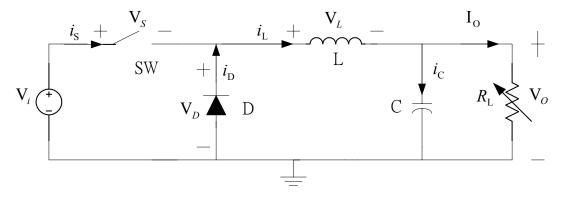

## 2.2 Typical Application

The AP2001 may operate in either the CCM (Continuous Conduction Mode) or the DCM (Discontinuous Conduction Mode). The following applications are designed for CCM (Continuous Conduction Mode) operation. That is, the inductor current is not allowed to fall to zero. To compare the disadvantage and advantage for CCM and DCM, the main disadvantage of CCM is the inherent stability problems (caused by the right-half-plane zero and the double pole in the small-signal control to output voltage transfer function). However, The main disadvantage of DCM that peak currents of switch and diode are larger than CCM when converting. Using power switch and output diode with larger current and power dissipation ratings should solve this issue of large peak current. The designer has to use larger output capacitors, and take more effort on EMI/RFI solution also. Designer could make a choice for each mode. For a low loading current, DCM is preferred for buck. If the load current requirement is high, CCM is preferred for buck. Figure 1 shows the basic buck topology. When the switch SW is turned on, energy is stored in the inductor L and it has constant voltage "VL = V1 - V0", the inductor current iL ramps up at a slope determined by the input voltage. Diode D is off during this period. Once the switch, SW, turns off, diode D starts to conduct and the energy stored in the inductor is released to the load. Current in the inductor ramps down at a slope determined by the difference between the input and output voltages.

Figure 1. Typical Buck Converter Topology

# 2.3 Input / Output Connections

Figure 3. I/O Connections

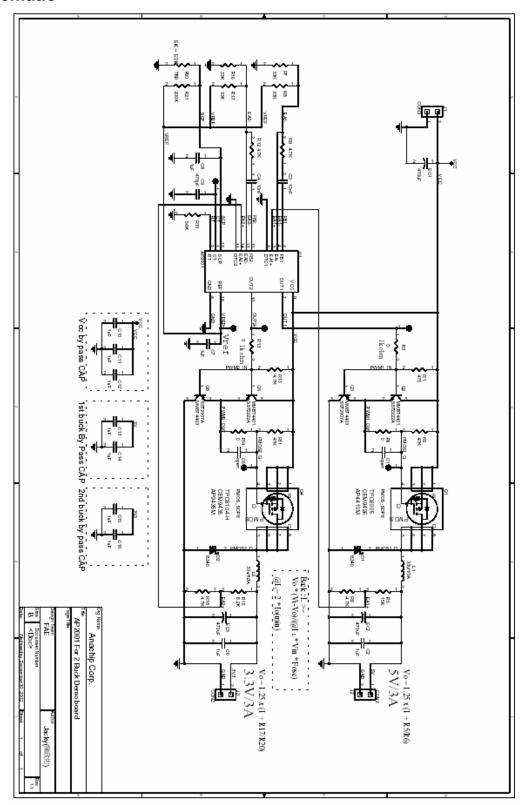

## 2.4 Schematic

Figure 4. 2\_buck demo board schematic

# Application Note AP2001 Dual Buck Converter

# 2.5 Board of Materials

| No. | Value     | Q'ty | Part Reference                             | Description                                 | Manufacturers    | Part Number          |

|-----|-----------|------|--------------------------------------------|---------------------------------------------|------------------|----------------------|

| 1   | open      | 1    | C1 C5                                      | Don't install                               | Philips          |                      |

| 2   | 1uF       | 10   | C2 C6 C7 C10 C11<br>C12 C13 C14 C15<br>C16 | Ceramic Chip CAP. 1uF 25V ±10% K X7R 0805   | Philips          |                      |

| 3   | 10nF      | 2    | C3 C4                                      | Ceramic Chip CAP. 10nF 25V ±10% K X7R 0805  | Philips          |                      |

| 4   | 1uF       | 1    | C8                                         | Ceramic Chip CAP. 1uF 25V ±10% K X7R 0805   | Philips          |                      |

| 5   | 470pF     | 1    | C9                                         | Ceramic Chip CAP. 470pF 25V ±10% K X7R 0805 | Philips          |                      |

| 6   | B340      | 2    | D1 D2                                      | Schottky Diode 3A 40V                       | DIODES           | B340A                |

| 7   | 470uF     | 3    | EC1 EC2 EC3                                | Electrolysis Capacitors                     |                  |                      |

| 8   | CON2      | 3    | J1 J2 J3                                   | 2P PCB Terminal Block                       | DINKLE           | ELK508V-02P          |

| 9   | 33uH/3A   | 1    | L1 L2                                      | TOROID COILS 33uH 3A                        | Star Electronics |                      |

| 10  | PMOS_SOP8 | 2    | Q1 Q4                                      | P-Channel MOSFET -30V -3A ↑                 | CET<br>APEC      | CEM4435<br>AP4435M   |

| 11  | MMBT4401  | 2    | Q3 Q6                                      | NPN BJT 40V 0.6A SOT-23                     | ROHM<br>DIODES   | SST2222A<br>MMBT4401 |

| 12  | MMBT4403  | 2    | Q2 Q5                                      | PNP BJT -40V -0.6A SOT-23                   | ROHM<br>DIODES   | SST2907A<br>MMBT4403 |

| 13  | 470       | 1    | R1                                         | Chip Resistance 470 1/8W ±10% J 0805        | Yageo(RL Series) |                      |

| 14  | 47K       | 2    | R2 R11                                     | Chip Resistance 47K 1/8W ±10% J 0805        | Yageo(RL Series) |                      |

| 15  | 0         | 4    | R3 R4 R13 R14                              | Chip Resistance 0 1/8W ±10% J 0805          | Yageo(RL Series) |                      |

| 16  | 15K       | 1    | R5                                         | Chip Resistance 15K 1/8W ±10% J 0805        | Yageo(RL Series) |                      |

| 17  | 4.7K      | 5    | R6 R9 R10 R12 R18                          | Chip Resistance 4.7K 1/8W ±10% J 0805       | Yageo(RL Series) |                      |

|     | 33K       |      | R7 R8 R16 R17                              | Chip Resistance 33K 1/8W ±10% J 0805        | Yageo(RL Series) |                      |

|     | 8.2K      |      | R15                                        | Chip Resistance 8.2K 1/8W ±10% J 0805       | Yageo(RL Series) |                      |

| 20  | 5.6K      | 1    | R19                                        | Chip Resistance 5.6K 1/8W ±10% J 0805       | Yageo(RL Series) |                      |

| 21  | TBD       | 1    | R20                                        | To be define (5K ~ 50K)                     | Yageo(RL Series) |                      |

| 22  | 200K      | 1    | R21                                        | Chip Resistance 22K 1/8W ±10% J 0805        | Yageo(RL Series) |                      |

| 23  | AP2001    | 1    | U1                                         | Monolithic Dual Channel PWM Controller      | Anachip          | AP2001S              |

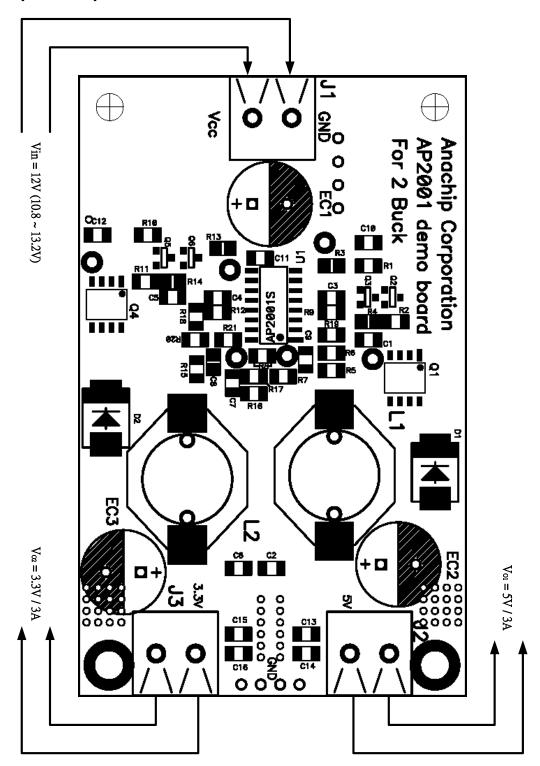

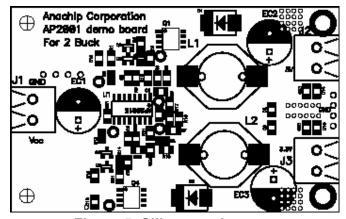

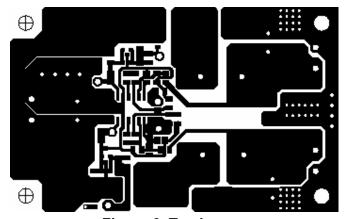

# 2.6 Board Layout

Board size is 80mm(W)x50mm(L)

Figure 5. Silkscreen layer

Figure 6. Top layer

Figure 7. Bottom layer

## 3. Design Procedure

#### 3.1 Introduction

The AP2001 integrated circuit is dual PWM controller, It operates over a wide input voltage range. This together with its low cost makes it a very popular choice for use in PWM controller. This section will describe the AP2001 to design procedure. The operation and the design of the dual-buck converter will also be discussed in detail.

## 3.2 Operating Specifications

| Specification                | Min  | Тур | Max  | Units |

|------------------------------|------|-----|------|-------|

| Input Voltage Range          | 10.8 | 12  | 13.2 | V     |

| Output Buck1 Voltage Range   |      | 5   |      | V     |

| Output Buck2 Voltage Range   |      | 3.3 |      | V     |

| Output Current (Buck1) Range | 0.3  | 3   |      | Α     |

| Output Current (Buck2) Range | 0.3  | 3   |      | Α     |

| Operating Frequency          | 180  | 200 | 220  | KHz   |

| Output Ripple                |      | 50  |      | mV    |

| Efficiency                   |      |     | 86   | %     |

**Table 1. Operating Specifications**

## 3.3 Design Procedures

This section describes the steps to design continuous-mode buck and boost converter, and explains how to construct basic power conversion circuits including the design of the control chip functions and the basic loop. A switching frequency of 200 kHz was chosen.

Example calculations accompany the design equations. Since this is a fixed output converter, all example calculations apply to the converter with output voltage is 3.3V/5V and input voltage set to 12 V, unless specified otherwise. The first quantity to be determined is the converter the duty cycle value.

Duty ratio D =

$$\frac{V_o + V_d}{V_{in} - V_{ds(sat)}} = \frac{T_{on}}{T_s}$$

,  $0 \le D \le 1$

Assuming the commutating diode forward voltage  $V_d$  = 0.5 V and the power switch on voltage  $V_{ds(sat)}$  = 0.1V, the duty cycle for  $V_o$  = 3.3V and  $V_{in}$  = 10.8, 12, 13.2 is 0.36, 0.32, 0.29 respectively; The duty cycle for  $V_o$  = 5V and  $V_{in}$  = 10.8, 12, 13.2 is 0.51, 0.46, 0.42 respectively.

#### 3.3.1 Selection of the buck inductor (L)

A buck converter uses a single-stage LC filter. Choose an inductor to maintain continuous-mode operation down to 10 percent (Io(min)) of the rated output load:

$$\triangle I_L = 2 \times 10\% \times I_0 = 2 \times 0.1 \times 3 = 0.6A$$

(For 5V and 3.3V)

The inductor "L" value is:

$$L \, \geq \, \frac{ \left( V_{\text{in}} - V_{\text{ds(sat)}} - V_{\text{o}} \right) \, x \, \, D_{\text{min}} }{ \Delta \, I_{\text{L}} \, x \, \, f_{\text{s}} } \, \, = \, \frac{ \left( 13.2 - 0.1 - 3.3 \right) \, x \, \, 0.29 }{ 0.6 \, x \, \left( 200 \, x \, \, 10^{\text{A}} \right) } = \, 23.7 \, \, \mu \, \, \text{H} \quad \text{For } 3.3 \, \text{V} \, \, 10^{\text{A}} \, \, \text{For } 3.3 \, \text{V} \, \, \text{To } 10^{\text{A}} \, \, \text{To } 10^{\text{A}}$$

$$L \, \geq \frac{\, \left( V_{\text{in}} - V_{\text{ds(sat)}} - V_{\text{o}} \right) \, x \, \, D_{\text{min}}}{\, \Delta \, I_{\text{L}} \, x \, \, f_{\text{s}}} \, \, = \, \frac{\, \left( 13.2 - 0.1 - 5 \right) x \, \, 0.42}{\, 0.6 \, x \, \left( 200 \, x \, \, 10^{\circ} 3 \right)} = \, 28.4 \, \mu \, H \quad \text{For 5V}$$

So we can choose 33  $\mu$  H for output voltage "3.3V" and "5V".

#### 3.3.2 Selection of the output capacitor (Cout)

Assuming that all of the inductor ripple current flows through the capacitor and the effective series resistance (ESR) is zero, the capacitance needed is:

$$C_{\text{out}} \, \ge \frac{ \triangle \, I_{\text{L}} }{ \, 8 \, x \, \, f_{\text{s}} \, x \, \, \triangle \, V_{\text{o}} } \, = \, \frac{0.6}{ \, 8 \, x \, \, (200 \, x \, \, 10^{\hspace{-0.5mm} -} \! 3) \, x \, \, 0.05} = \, 7.5 \, \mu \, \text{F}$$

Assuming the capacitance is very large, the ESR needed to limit the ripple to 50 mV is:

$$\mathsf{ESR} \ \leq \ \frac{\Delta \, \mathsf{V}_{\mathsf{o}}}{\Delta \, \mathsf{I}_{\mathsf{o}}} \ = \ \frac{0.05}{0.6} = \ 0.083 \, \Omega$$

The output filter capacitor should be rated at least ten times the calculated capacitance and 30–50 percent lower than the calculated ESR. This design used a 470  $\mu$  F/25V OS-Con capacitor in parallel with a ceramic to reduce ESR.

#### 3.3.3 Selection of the power switch (MOSFET)

Based on the preliminary estimate,  $R_{DS(on)}$  should be less than  $0.10 \text{ V} \div 3A = 33\text{m}\Omega$ . The **CEM4435**(*CET*) is a -30V p-channel MOSFET with  $R_{DS(on)} = 35\text{m}\Omega$ . Power dissipation (conduction + switching losses) can be estimated as:

$$P_{\text{MOSFET}} = I_o^2 \times R_{ds(on)} \times D_{max} + [0.5 \times V_{in} \times I_o \times (t_r + t_f) \times f_s]$$

Assuming total switching time (t<sub>r</sub> + t<sub>f</sub>) is 150 ns, a 55°C maximum ambient temperature, and thermal impedance  $R_{\theta JA} = 50$ °C/W , thus:

$P_{MOSFET} = (3 \times 3 \times 0.035 \times 0.36) + [0.5 \times 12 \times 3 \times (0.15 \times 10^{\circ}(-6)) \times (200 \times 10^{\circ}3) = 0.65W$

$$T_J = T_A + (R_{\theta JA} \times P_{MOSFET}) = 55 + (50 \times 0.65) = 87.5^{\circ}C...$$

(For 3.3V)

$P_{MOSFET} = (3 \times 3 \times 0.035 \times 0.51) + [0.5 \times 12 \times 3 \times (0.15 \times 10^{\circ}(-6)) \times (200 \times 10^{\circ}3) = 0.7W$

$T_J = T_A + (R_{\theta JA} \times P_{MOSFET}) = 55 + (50 \times 0.7) = 90^{\circ}C...$  (For 5V)

#### 3.3.4 Selection of the Rectifier (D)

The catch rectifier conducts during the time interval when the MOSFET is off. The **B340** (*DIODES*) is a 3A, 40V schottky rectifier in a SMC power surface-mount package. The power dissipation is:

$$P_D = I_0 \times V_d \times (1 - D_{min}) = 3 \times 0.5 \times (1 - 0.29) = 1.065W$$

.....(For 3.3V)

$P_D = I_0 \times V_d \times (1 - D_{min}) = 3 \times 0.5 \times (1 - 0.42) = 0.87W$ ....(For 5V)

Assuming a 55°C maximum ambient temperature, and thermal impedance  $R_{\beta JA} = 15^{\circ}C/W$ , thus:

$$T_J = T_A + (R_{\theta JA} \times P_D) = 55 + (15 \times 1.065) = 70.975^{\circ}C.$$

(For 3.3V)

$T_J = T_A + (R_{\theta JA} \times P_D) = 55 + (15 \times 0.87) = 68.05^{\circ}C.$  (For 5V)

#### 3.3.5 Selection of the input capacitor (Cin)

The RMS current rating of the input capacitor can be calculated from the following formula. The capacitor manufacturers data sheet must be checked to assure that this current rating is not exceeded.

$$I_{\text{in(rms)}} = 2\sqrt{\left[D \times \left(I_{\text{0(max)}} + I_{\text{0(min)}}\right) \times \left(I_{\text{0(max)}} - I_{\text{0(min)}}\right) + \left(\Delta I_{\text{L}}^2\right)/3\right]} = \sqrt{\left[0.36 \times (3 + 0.3) \times (3 - 0.3) + 0.36/3\right]}$$

$$= 2 \times 1.8A = 3.6A$$

This capacitor should be located close to the IC using short leads and the voltage rating should be approximately 2 times the maximum input voltage. We select input capacitor value "470uF/25V".

# 4. Voltage monitor by AP434

In some applications, the output voltage is concerned too high to damage the IC. To avoid the IC being damaged, comparing output voltage with a reference could monitor the output voltage. AP434 is a monolithic IC that includes one independent OP-Amp and another OP-Amp, which the non-inverting input is wired to a fixed voltage reference. AP434 data sheet provides the low cost and space saving of voltage monitoring function.

Written by Cheng-Yu Chen(陳政佑)