Elan Microelectronics Crop.

# CONFIDENTIAL

# EM65100

69COM/ 101SEG 4 Gray Level STN LCD Driver

March 08, 2005 Version 0.6

|         | EM65100 Specification Revision History                                                                                                                                                                                                                                                                                                                                             |                 |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

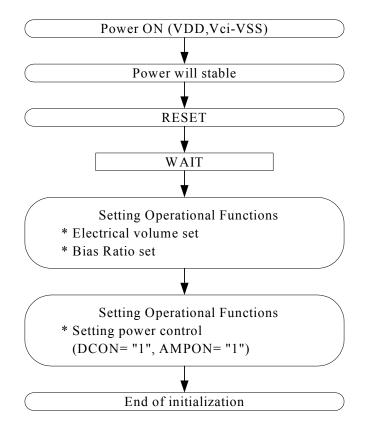

| Version | Content                                                                                                                                                                                                                                                                                                                                                                            | Date            |

| 0.1     | Initial version                                                                                                                                                                                                                                                                                                                                                                    | April 13, 2003  |

| 0.2     | Page 12:Power circuit block diagramPage 16:Parallel input orderPage 16,51:delete slave modePage 18,60:First step to read the specific registerPage 21:RAM address of Monochrome modePage 38: bank numberPage 40,41: write/read one byte data into DDRAMPage 57:The table of SC register set upPage 63,64: driver sink current, Ron value of SSEG andSCOM DC characteristics values | June 3,2003     |

| 0.3     | Remove the word "Preliminary"<br>Page 6: Modify RESB ITO Resistor value<br>Page 7: CSB and WRB exchange pad sequence<br>Page 15: "CK" pin voltage for using internal clock.                                                                                                                                                                                                        | August 1,2003   |

| 0.4     | Modify dynamic current of Display off on page 63                                                                                                                                                                                                                                                                                                                                   | August 28,2003  |

| 0.5     | Modify ITO value                                                                                                                                                                                                                                                                                                                                                                   | October 12,2004 |

| 0.6     | Modify RESET time                                                                                                                                                                                                                                                                                                                                                                  | March 08,2005   |

**Caution:** The information in this document is subject to change without notice. Before using this document, please confirm that this is the latest version.

# Contents

| 1.  | GENERAL DESCRIPTION 4                               |

|-----|-----------------------------------------------------|

| 2.  | FEATURE 4                                           |

| 3.  | APPLICATIONS                                        |

| 4.  | PIN CONFIGURATIONS (PACKAGE) 5                      |

| 5.  | FUNCTIONAL BLOCK DIAGRAM 10                         |

| 6.  | PIN DESCRIPTION                                     |

| 7.  | FUNCTIONAL DESCRIPTION                              |

| 8.  | CONTROL REGISTER                                    |

| 9.  | RELATIONSHIP BETWEEN SETTING AND COMMON/DISPLAY RAM |

| 10. | ABSOLUTE MAXIMUM RATINGS                            |

|     | DC CHARACTERISTICS                                  |

| 12. | AC CHARACTERISTIC                                   |

| 13. | APPLICATION CIRCUIT                                 |

# 1. General description

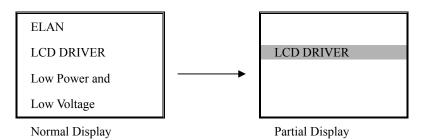

EM65100 is one STN-LCD drivers for 4-gray scale display. The sub-screen display function makes it possible to display different images and data in a sub-screen inside the main LCD screen. It also has a built-in display RAM, a power supply circuit for LCD drive, and an LCD controller circuit, therefore contributing to compact system design. Its partial display function realizes low power consumption.

\*Partial display function: A function that utilizes only part of the screen, thus reducing power consumption.

### 2. Feature

Display RAM capacity

Graphic: 104\*67\*2=13,936 bits

Icons: 104\*2\*2=416 bits

- ▶ Ratio of display duty cycle: 1/10, 1/18, 1/26, 1/34, 1/42, 1/50, 1/58, 1/69

- Outputs

Segment:101 outputs, Common: 67 outputs

Static driver: 2 outputs

- ▶ Built-in display104x69x2=14352bit RAM and power supply circuit

- Partial display functions

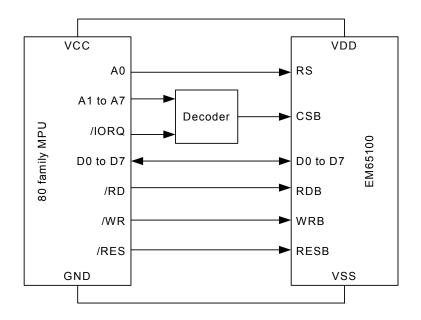

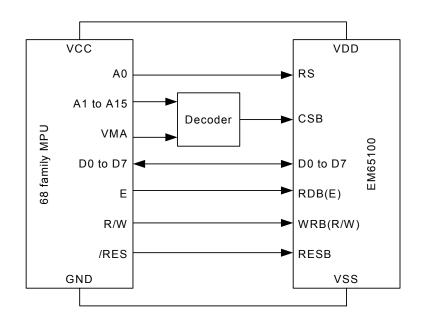

- ▶ Bus connection with 80-family/ 68-family and Elan MPU

- Serial interface is available

- ► Logic power supply voltage: 1.8 to 3.3 V

- ► LCD driving voltage: 5.0 to 12.0 V

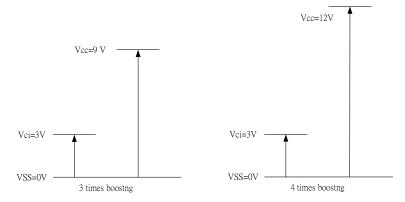

- ► Booster: 2 to 4 times

- ► Write system cycle: 140 ns

- Package(Ordering information):

| Part Number | Package          | Description | Package information |

|-------------|------------------|-------------|---------------------|

| EM65100AGH  | Gold bumped chip | NA          | Page 5              |

Note: The EM65100 series has the following sub-codes depending on their shapes.

H: Bare chip (Aluminum pad without bumped); GH: Gold bumped chip;

F: COF package; T: TAB (TCP) package

Example EM65100AGH → EM65100: Elan number ; A: Package Version ;GH: COF Gold bumped chip

### 3. Applications

- ► Mobile phone

- ► Small PDA

# 4. Pin configurations (package)

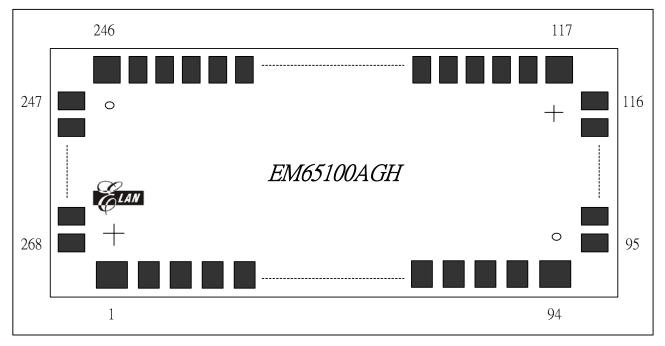

Figure 1. Pin configuration

Note: With the Elan logo in down left the pin 1 is in the down left corner

| Mark   | Coordinate (X,Y) | Mark    | Coordinate (X,Y) |

|--------|------------------|---------|------------------|

| U-Left | -3195.0,350.0    | U-Right | 3195.0,350.0     |

| D-Left | -3195.0,-350.0   | D-Right | 3195.0,-350.0    |

100um

U-Left and D-Right:

## Pad configuration

| Item                               | Pad No.        | Size                    |      | Unit |

|------------------------------------|----------------|-------------------------|------|------|

| Item                               | Tau No.        | Х                       | Y    | Umt  |

| Chip size                          | -              | 7260                    | 1570 |      |

|                                    | 1~94           | 56                      | 63   |      |

|                                    | 95,96,267,268  | 63                      | 56   |      |

| Dumm Cino                          | 97~115,248~266 | 63                      | 36   |      |

| Bump Size                          | 116,247        | 63                      | 48   |      |

|                                    | 117,246        | 48                      | 63   |      |

|                                    | 118~245        | 36                      | 63   |      |

| Pad Pitch                          |                | 50 (min.)               |      | μm   |

| Die thickness<br>(excluding bumps) | 508 +/- 25.4   |                         |      |      |

| Bump Height                        | All            | Pad 17 +/- 3 (within di | e)   |      |

| Minimum Bump Gap                   | 14             |                         |      |      |

| Coordinate Origin                  |                | Chip center             |      |      |

# **Recommended COG ITO Traces Resistor**

| Interface                         | ITO Traces resistances |

|-----------------------------------|------------------------|

| V0~V4                             |                        |

| CAP1+,CAP1-,CAP2+,CAP2-,CAP3+,Vcc | M500                   |

| VDD,Vci                           | Max=50Ω                |

| VSSL,VSSH                         |                        |

| WRB,RDB,CSB,,D0~D7                | Max=3KΩ                |

| RESB                              | Max=5~10 KΩ            |

### **PAD Coordinates Table**

| Pin NO   | Pad Name       | Coordinate<br>(X,Y)                  | Pin NO    | Pad Name        | Coordinate<br>(X,Y)              |

|----------|----------------|--------------------------------------|-----------|-----------------|----------------------------------|

| 1        | WRB            | -3348.6 ,-654.5                      | 51        | CAP1-           | 338.6 ,-654.5                    |

| 2        | RESB           | -3278.6 ,-654.5                      | 52        | CAP1+           | 408.6 ,-654.5                    |

| 3        | RS             | -3208.6 ,-654.5                      | 53        | CAP1+           | 478.6 ,-654.5                    |

| 4        | CSB            | -3138.6 ,-654.5                      | 54        | CAP1+           | 548.6 ,-654.5                    |

| 5        | RDB            | -3068.6 ,-654.5                      | 55        | CAP1+           | 618.6 ,-654.5                    |

| 6        | D0             | -2998.6 ,-654.5                      | 56        | CAP1+           | 688.6 ,-654.5                    |

| 7        | D1             | -2928.6 ,-654.5                      | 57        | CAP2+           | 758.6 ,-654.5                    |

| 8        | D2             | -2858.6 ,-654.5                      | 58        | CAP2+           | 828.6 ,-654.5                    |

| 9        | D3             | -2788.6 ,-654.5                      | 59        | CAP2+           | 898.6 ,-654.5                    |

| 10       | D4             | -2718.6 ,-654.5                      | 60        | CAP2+           | 968.6 ,-654.5                    |

| 11       | D5             | -2648.6 ,-654.5                      | 61        | CAP2+           | 1038.6 ,-654.5                   |

| 12       | D6             | -2578.6 ,-654.5                      | 62        | CAP2-           | 1108.6 ,-654.5                   |

| 13       | D7             | -2508.6 ,-654.5                      | 63        | CAP2-           | 1178.6 ,-654.5                   |

| 14       | VSS            | -2438.6 ,-654.5                      | 64        | CAP2-           | 1248.6 ,-654.5                   |

| 15       | CK             | -2368.6 ,-654.5                      | 65        | CAP2-           | 1318.6 ,-654.5                   |

| 16       | CKS            | -2298.6 ,-654.5                      | 66        | CAP2-           | 1388.6 ,-654.5                   |

| 17       | VREF           | -2228.6 ,-654.5                      | 67        | V4              | 1458.6 ,-654.5                   |

| 18       | VREF           | -2158.6 ,-654.5                      | 68        | V4              | 1528.6 ,-654.5                   |

| 19       | VREF           | -2088.6 ,-654.5                      | 69        | V4              | 1598.6 ,-654.5                   |

| 20       | VREF           | -2018.6 ,-654.5                      | 70        | V4              | 1668.6 ,-654.5                   |

| 20       | VREF           | -1948.6 ,-654.5                      | 70        | V3              | 1738.6 ,-654.5                   |

| 21       | VDD            | -1878.6 ,-654.5                      | 72        | V3              | 1808.6 ,-654.5                   |

| 23       | VDD            | -1808.6 ,-654.5                      | 72        | V3              | 1878.6 ,-654.5                   |

| 23       | VDD            | -1738.6 ,-654.5                      | 75        | V3              | 1948.6 ,-654.5                   |

| 24       | VDD            | -1668.6 ,-654.5                      | 75        | V2              | 2018.6,-654.5                    |

| 25       | VDD            | -1598.6 ,-654.5                      | 75        | V2<br>V2        | 2018.6,-654.5                    |

| 20       | Vci            | -1528.6 ,-654.5                      | 70        | V2<br>V2        | 2158.6 ,-654.5                   |

| 27       | Vci            | -1458.6 ,-654.5                      | 78        | V2<br>V2        | 2228.6,-654.5                    |

| 28       | Vci            | -1388.6 ,-654.5                      | 78        | V2<br>V1        | 2298.6,-654.5                    |

| 30       | Vci            | -1318.6 ,-654.5                      | 80        | V1<br>V1        | 2368.6,-654.5                    |

| 30       | Vci            | -1248.6 ,-654.5                      | 81        | VI              | 2438.6,-654.5                    |

| 32       | VSSL           | -1178.6 ,-654.5                      | 82        | V1<br>V1        | 2508.6,-654.5                    |

| 33       | VSSL           | -11/8.6 ,-654.5                      | 82        | V0              | 2578.6 ,-654.5                   |

| 33       | VSSL           | -1038.6 ,-654.5                      | 83        | <u>V0</u><br>V0 |                                  |

| 35       | VSSL           | -968.6 ,-654.5                       | 85        | <u></u>         | 2648.6 ,-654.5<br>2718.6 ,-654.5 |

| 36       | VSSL           | -898.6 ,-654.5                       | 85        | <u>V0</u><br>V0 | 2788.6 ,-654.5                   |

| 30       | VSSL           | -828.6 ,-654.5                       | 87        | VSSH            |                                  |

| 38       | Vcc            | -758.6 ,-654.5                       | 88        | VSSH            | 2858.6 ,-654.5<br>2928.6 ,-654.5 |

| 38<br>39 | Vcc            | •                                    | 88        | VSSH            | 2928.6,-654.5                    |

| 40       | Vcc            | -688.6 ,-654.5                       | 90        | VSSH            | 3068.6,-654.5                    |

| -        |                | -618.6 ,-654.5                       | 90        |                 |                                  |

| 41       |                | -548.6 ,-654.5                       |           | VSSH            | 3138.6,-654.5                    |

| 42       | CAP3+          | -478.6 ,-654.5                       | 92<br>03  | TEST            | 3208.6,-654.5                    |

| 43       | CAP3+          | -408.6 ,-654.5                       | 93        | P/S             | 3278.6 ,-654.5                   |

| 44       | CAP3+          | -338.6 ,-654.5                       | 94        | VDD<br>NC1      | 3348.6,-654.5                    |

| 45       | CAP3+          | -268.6 ,-654.5                       | 95        | NC1             | 3499.5,-469.5                    |

| 46       | CAP3+          | -198.6 ,-654.5                       | 96        | SCOM            | 3499.5,-399.5                    |

| 47       | CAP1-          | 58.6,-654.5                          | 97        | COM33           | 3499.5,-339.5                    |

| 48       | CAP1-          | 128.6 ,-654.5                        | 98        | COM32           | 3499.5 ,-289.5                   |

| 49<br>50 | CAP1-<br>CAP1- | <u>198.6</u> ,-654.5<br>268.6,-654.5 | 99<br>100 | COM31<br>COM30  | 3499.5 ,-239.5<br>3499.5 ,-189.5 |

| Pin NO | Pad Name       | Coordinate<br>(X,Y) | Pin NO | Pad Name       | Coordinate<br>(X,Y) |

|--------|----------------|---------------------|--------|----------------|---------------------|

| 101    | COM29          | 3499.5 ,-139.5      | 151    | SEG19          | 1525.0 ,654.5       |

| 102    | COM28          | 3499.5 ,-89.5       | 152    | SEG20          | 1475.0 ,654.5       |

| 103    | COM27          | 3499.5 ,-39.5       | 153    | SEG21          | 1425.0 ,654.5       |

| 104    | COM26          | 3499.5 ,10.5        | 154    | SEG22          | 1375.0 ,654.5       |

| 105    | COM25          | 3499.5 ,60.5        | 155    | SEG23          | 1325.0 ,654.5       |

| 106    | COM24          | 3499.5 ,110.5       | 156    | SEG24          | 1275.0 ,654.5       |

| 107    | COM23          | 3499.5 ,160.5       | 157    | SEG25          | 1225.0 ,654.5       |

| 108    | COM22          | 3499.5 ,210.5       | 158    | SEG26          | 1175.0 ,654.5       |

| 109    | COM21          | 3499.5 ,260.5       | 159    | SEG27          | 1125.0 ,654.5       |

| 110    | COM20          | 3499.5 ,310.5       | 160    | SEG28          | 1075.0 ,654.5       |

| 111    | COM19          | 3499.5,360.5        | 161    | SEG29          | 1025.0,654.5        |

| 112    | COM18          | 3499.5,410.5        | 162    | SEG30          | 975.0,654.5         |

| 113    | COM17          | 3499.5,460.5        | 163    | SEG31          | 925.0,654.5         |

| 114    | COM16          | 3499.5,510.5        | 164    | SEG32          | 875.0,654.5         |

| 115    | COM15          | 3499.5 ,560.5       | 165    | SEG33          | 825.0,654.5         |

| 116    | COM14          | 3499.5 ,616.5       | 166    | SEG34          | 775.0 ,654.5        |

| 117    | COM13          | 3231.0 ,654.5       | 167    | SEG35          | 725.0 ,654.5        |

| 118    | COM12          | 3175.0 ,654.5       | 168    | SEG36          | 675.0 ,654.5        |

| 119    | COM12<br>COM11 | 3125.0 ,654.5       | 169    | SEG37          | 625.0 ,654.5        |

| 120    | COM10          | 3075.0 ,654.5       | 170    | SEG38          | 575.0 ,654.5        |

| 120    | COM9           | 3025.0 ,654.5       | 170    | SEG39          | 525.0 ,654.5        |

| 121    | COM8           | 2975.0 ,654.5       | 172    | SEG40          | 475.0 ,654.5        |

| 122    | COM7           | 2925.0 ,654.5       | 172    | SEG40<br>SEG41 | 425.0 ,654.5        |

| 123    | COM6           | 2875.0 ,654.5       | 175    | SEG41<br>SEG42 | 375.0 ,654.5        |

| 124    | COM5           | 2875.0 ,654.5       | 175    | SEG42<br>SEG43 | 325.0,654.5         |

| 125    | COM5<br>COM4   | 2775.0 ,654.5       | 175    | SEG45<br>SEG44 | 275.0 ,654.5        |

| 120    | COM3           | 2725.0 ,654.5       | 170    | SEG45          | 225.0,654.5         |

| 127    | COM3<br>COM2   | 2675.0 ,654.5       | 178    | SEG45<br>SEG46 | 175.0 ,654.5        |

| 128    | COM2<br>COM1   | 2625.0 ,654.5       | 178    | SEG40          | 125.0 ,654.5        |

| 129    | COMU           | 2575.0 ,654.5       | 1/9    | SEG48          | 75.0 ,654.5         |

| 130    | COMO           |                     | 180    | SEG49          | 25.0 ,654.5         |

|        |                | 2525.0 ,654.5       | 181    | SEG50          |                     |

| 132    | SEG0           | 2475.0 ,654.5       |        | SEG50<br>SEG51 | -25.0 ,654.5        |

| 133    | SEG1           | 2425.0 ,654.5       | 183    |                | -75.0,654.5         |

| 134    | SEG2<br>SEG3   | 2375.0 ,654.5       | 184    | SEG52          | -125.0,654.5        |

| 135    |                | 2325.0 ,654.5       | 185    | SEG53          | -175.0 ,654.5       |

| 136    | SEG4           | 2275.0 ,654.5       | 186    | SEG54          | -225.0 ,654.5       |

| 137    | SEG5           | 2225.0 ,654.5       | 187    | SEG55          | -275.0 ,654.5       |

| 138    | SEG6           | 2175.0 ,654.5       | 188    | SEG56          | -325.0 ,654.5       |

| 139    | SEG7           | 2125.0 ,654.5       | 189    | SEG57          | -375.0 ,654.5       |

| 140    | SEG8           | 2075.0 ,654.5       | 190    | SEG58          | -425.0 ,654.5       |

| 141    | SEG9           | 2025.0 ,654.5       | 191    | SEG59          | -475.0 ,654.5       |

| 142    | SEG10          | 1975.0 ,654.5       | 192    | SEG60          | -525.0 ,654.5       |

| 143    | SEG11          | 1925.0 ,654.5       | 193    | SEG61          | -575.0 ,654.5       |

| 144    | SEG12          | 1875.0 ,654.5       | 194    | SEG62          | -625.0 ,654.5       |

| 145    | SEG13          | 1825.0 ,654.5       | 195    | SEG63          | -675.0 ,654.5       |

| 146    | SEG14          | 1775.0 ,654.5       | 196    | SEG64          | -725.0 ,654.5       |

| 147    | SEG15          | 1725.0 ,654.5       | 197    | SEG65          | -775.0 ,654.5       |

| 148    | SEG16          | 1675.0 ,654.5       | 198    | SEG66          | -825.0 ,654.5       |

| 149    | SEG17          | 1625.0 ,654.5       | 199    | SEG67          | -875.0 ,654.5       |

| 150    | SEG18          | 1575.0 ,654.5       | 200    | SEG68          | -925.0 ,654.5       |

| Pin NO | Pad Name | Coordinate<br>(X,Y) | Pin NO | Pad Name | Coordinate<br>(X,Y) |

|--------|----------|---------------------|--------|----------|---------------------|

| 201    | SEG69    | -975.0 ,654.5       | 251    | COM52    | -3499.5,410.5       |

| 202    | SEG70    | -1025.0 ,654.5      | 252    | COM53    | -3499.5 ,360.5      |

| 203    | SEG71    | -1075.0 ,654.5      | 253    | COM54    | -3499.5 ,310.5      |

| 204    | SEG72    | -1125.0 ,654.5      | 254    | COM55    | -3499.5 ,260.5      |

| 205    | SEG73    | -1175.0 ,654.5      | 255    | COM56    | -3499.5 ,210.5      |

| 206    | SEG74    | -1225.0 ,654.5      | 256    | COM57    | -3499.5 ,160.5      |

| 207    | SEG75    | -1275.0 ,654.5      | 257    | COM58    | -3499.5 ,110.5      |

| 208    | SEG76    | -1325.0 ,654.5      | 258    | COM59    | -3499.5 ,60.5       |

| 209    | SEG77    | -1375.0 ,654.5      | 259    | COM60    | -3499.5 ,10.5       |

| 210    | SEG78    | -1425.0 ,654.5      | 260    | COM61    | -3499.5 ,-39.5      |

| 211    | SEG79    | -1475.0,654.5       | 261    | COM62    | -3499.5 ,-89.5      |

| 212    | SEG80    | -1525.0 ,654.5      | 262    | COM63    | -3499.5 ,-139.5     |

| 213    | SEG81    | -1575.0 ,654.5      | 263    | COM64    | -3499.5 ,-189.5     |

| 214    | SEG82    | -1625.0 ,654.5      | 264    | COM65    | -3499.5 ,-239.5     |

| 215    | SEG83    | -1675.0 ,654.5      | 265    | COM66    | -3499.5 ,-289.5     |

| 216    | SEG84    | -1725.0 ,654.5      | 266    | COMB     | -3499.5 ,-339.5     |

| 217    | SEG85    | -1775.0,654.5       | 267    | SSEG     | -3499.5 ,-399.5     |

| 218    | SEG86    | -1825.0 ,654.5      | 268    | M86      | -3499.5 ,-469.5     |

| 219    | SEG87    | -1875.0 ,654.5      |        |          |                     |

| 220    | SEG88    | -1925.0 ,654.5      |        |          |                     |

| 221    | SEG89    | -1975.0 ,654.5      |        |          |                     |

| 222    | SEG90    | -2025.0 ,654.5      |        |          |                     |

| 223    | SEG91    | -2075.0,654.5       |        |          |                     |

| 224    | SEG92    | -2125.0 ,654.5      |        |          |                     |

| 225    | SEG93    | -2175.0 ,654.5      |        |          |                     |

| 226    | SEG94    | -2225.0,654.5       |        |          |                     |

| 227    | SEG95    | -2275.0 ,654.5      |        |          |                     |

| 228    | SEG96    | -2325.0 ,654.5      |        |          |                     |

| 229    | SEG97    | -2375.0 ,654.5      |        |          |                     |

| 230    | SEG98    | -2425.0 ,654.5      |        |          |                     |

| 231    | SEG99    | -2475.0 ,654.5      |        |          |                     |

| 232    | SEG100   | -2525.0 ,654.5      |        |          |                     |

| 233    | COM34    | -2575.0 ,654.5      |        |          |                     |

| 234    | COM35    | -2625.0 ,654.5      |        |          |                     |

| 235    | COM36    | -2675.0 ,654.5      |        |          |                     |

| 236    | COM37    | -2725.0 ,654.5      |        |          |                     |

| 237    | COM38    | -2775.0 ,654.5      |        |          |                     |

| 238    | COM39    | -2825.0 ,654.5      |        |          |                     |

| 239    | COM40    | -2875.0 ,654.5      |        |          |                     |

| 240    | COM41    | -2925.0 ,654.5      |        |          |                     |

| 241    | COM42    | -2975.0 ,654.5      |        |          |                     |

| 242    | COM43    | -3025.0 ,654.5      |        |          |                     |

| 243    | COM44    | -3075.0,654.5       |        |          |                     |

| 244    | COM45    | -3125.0 ,654.5      |        |          |                     |

| 245    | COM46    | -3175.0 ,654.5      |        |          |                     |

| 246    | COM47    | -3231.0 ,654.5      |        |          |                     |

| 247    | COM48    | -3499.5 ,616.5      |        |          |                     |

| 248    | COM49    | -3499.5 ,560.5      |        |          |                     |

| 249    | COM50    | -3499.5 ,510.5      |        |          |                     |

| 250    | COM51    | -3499.5,460.5       |        |          |                     |

#### Note: For PCB layout, IC substrate must be floated or connected to VSS

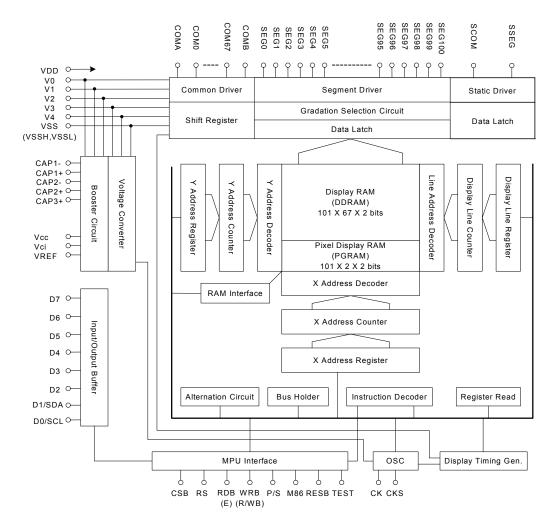

# 5. Functional block diagram

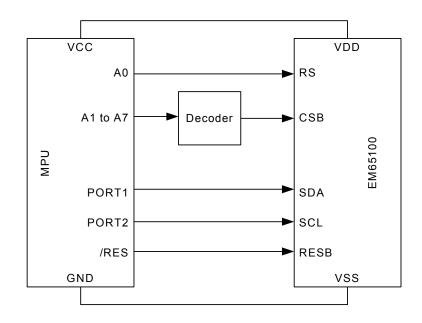

#### 5.1 System Block Diagram

Figure 2. System Block Diagram

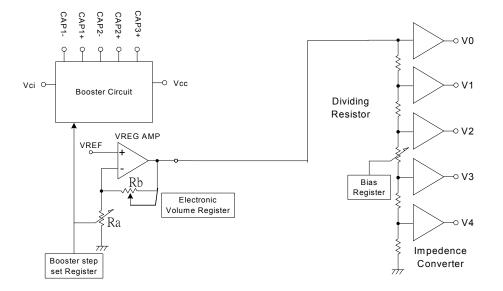

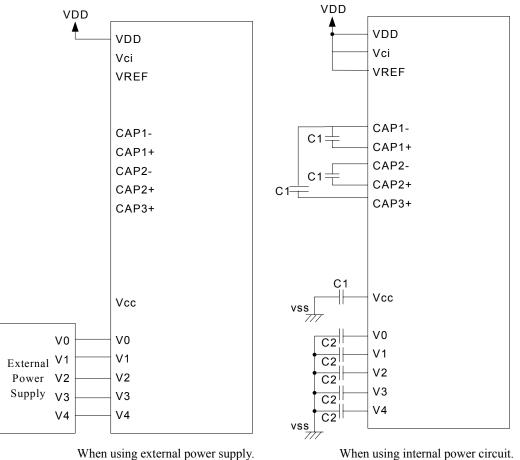

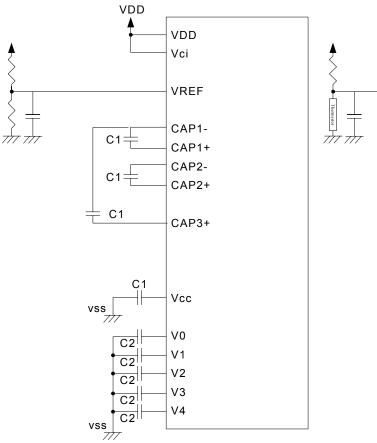

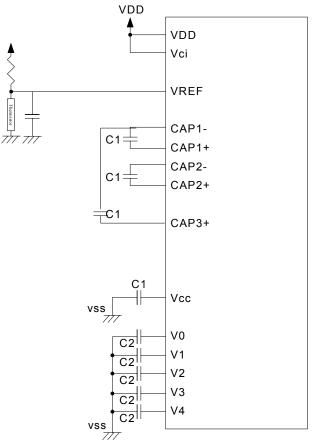

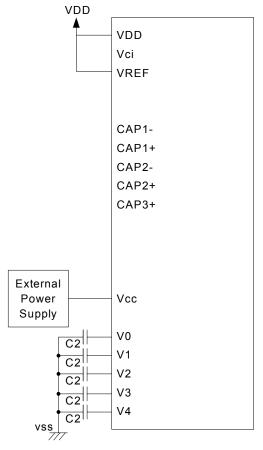

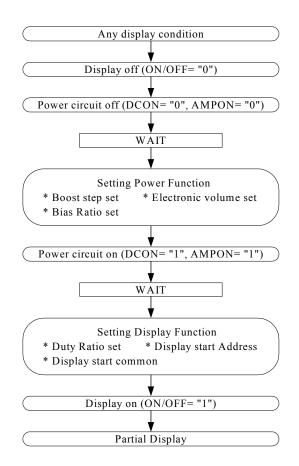

#### 5.2 Power Circuit Block Diagram

Figure 3. Power Circuit Block Diagram

# 6. Pin Description

### 6.1 Power Supply Pins

| Symbol                     | I/O             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD                        | Power<br>Supply | Power supply pin for logic circuit to +1.8 to 3.3V                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| VSSL                       | Power<br>Supply | Ground pin for logic circuit, connect to 0V                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| VSSH                       | Power<br>Supply | Ground pin for high voltage circuit, connected to 0V                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| V0<br>V1<br>V2<br>V3<br>V4 |                 | Bias power supply pin for LCD drive voltage<br>When using an external power supply, convert impedance by using resistance-division of LCD<br>drive power supply or operation amplifier before adding voltage to the pins. These voltages<br>should have following relationship: VSS <v4<v3<v2<v1<v0<br>When the internal power supply circuit is active, these voltages are generated by the built-in<br/>booster and voltage converter. Then, must connect capacitor each to VSS.</v4<v3<v2<v1<v0<br> |

#### 6.2 LCD Power Supply Circuit Pins

| Symbol | I/O             | Description                                                                                                         |

|--------|-----------------|---------------------------------------------------------------------------------------------------------------------|

| CAP1+  | 0               |                                                                                                                     |

| CAP1-  | 0               |                                                                                                                     |

| CAP2+  | 0               | When internal Booster circuit is used, external capacitor(s) is/are connected to these pin                          |

| CAP2-  | 0               |                                                                                                                     |

| CAP3+  | 0               |                                                                                                                     |

| VREF   | Ι               | Voltage input pin for generating reference power source                                                             |

| Vci    | Power<br>Supply | Voltage supply pin for booster circuit. Usually the same voltage level as VDD.                                      |

| Vcc    | 0               | Output pin of boosted voltage in the built-in booster.<br>The capacitor must be connected between this pin and VSS. |

6.3 System Bus Pins

| Symbol                    | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|---------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

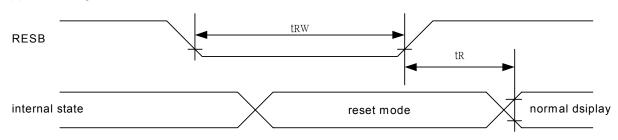

| RESB                      | Ι   | Reset input pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|                           |     | When RESB is "L", initialization is executed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| D0/SCL<br>D1/SDA<br>D2-D7 | I/O | Data bus / Signal interface related pins.<br>When parallel interface is selected (P/S = "H"), The D7-D0 are 8-bits bi-directional data bus,<br>connect to MPU data bus.<br>When serial interface is selected (P/S = "L"), D0 and D1 (SCL, SDA) are used as serial<br>interface pins.<br>SCL: Input pin for data transfer clock<br>SDA: Serial data input pin<br>SDA data is latched at the rising edge of SCL.<br>Internal serial/parallel conversion into 8-bit data occurs at the rising edge of 8 <sup>th</sup> clock of SCL<br>After completing data transferring, or when making no access, be sure to set SCL to "L". |  |  |

| CSB                       | Ι   | Chip Select input pin.<br>CSB = "L": accepts access from MPU<br>CSB = "H": denies access from MPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| RS                        | Ι   | RAM/Register select input pin.<br>RS = "0": D7-D0 are display RAM data<br>RS = "1": D7-D0 are control register data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| RDB<br>(E)                | Ι   | Read/Write control pin<br>Select 80-family MPU type (M86 = "L")<br>The RDB is a data read signal. When RDB is "L", D7-D0 are in an output status.<br>Select 68-family MPU type (M86 = "H")<br>R/WB = "H": When E is "H", D7-D0 are in an output status.<br>R/WB = "L": The data on D7-D0 are latched at falling edge of the E signal.                                                                                                                                                                                                                                                                                       |  |  |

| WRB<br>(R/WB)             | Ι   | Read/Write control pin   Select 80-family MPU type (M86 = "L")   The WRB is a data write signal. The data on D7-D0 are latched at rising edge of the WRB signal.   Select 68-family MPU type (M86 = "H")   Read/Write control input pin.   R/W = "H": Read   R/W = "L": Write                                                                                                                                                                                                                                                                                                                                               |  |  |

| M86                       | Ι   | MPU interface type selecting input pin.<br>M86 = "H": 68-family interface<br>M86 = "L": 80-family interface<br>Fixed at either "H" or "L"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| P/S                       | I   | Parallel/Serial interface select pin.P/SChip selectData identificationDataRead/WriteSerial clockHCSBRSD0-D7RDB, WRB-LCSBRSSDAWrite onlySCL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|                           |     | P/S = "H": For parallel interface.<br>P/S = "L": For serial interface. Fix D15-D5 pins are Hi-Z, RDB and WRB pins to either "H" or "L".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

#### 6.4 LCD Drive Circuit Signals

| Symbol          | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

|-----------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| SEG0-<br>SEG101 | 0   | Segment output pins for LCD drives.<br>According to the data of the Display RAM data, non-lighted at "0", lighted at "1" (Normal<br>Mode). non-lighted at "1", lighted at "0" (Reverse Mode) and, by a combination of M signal<br>and display data, one signal level among V0,V2,V3 and VSS signal levels are selected.<br>(When Monochrome Display)<br>M Signal<br>Display RAM<br>Data<br>Normal Mode<br>Reverse Mode<br>V0<br>V2<br>V0<br>V3<br>VSS<br>V3<br>V3<br>V3<br>V3<br>V3<br>V3<br>V3<br>V3<br>V3<br>V3 |  |  |  |  |  |  |

| COM0-<br>COM66  | 0   | Common output pins for LCD drivers. By a combination of the scanning data and M signal, one signal level among V0, V1, V4 and VSS signal level is selected.DataMOutput levelHHVSSLHV1HLV0LLV4                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| COMA            | 0   | Common output pin for LCD drive exclusively for icons.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| COMB            | 0   | Common output pin for LCD drive exclusively for icons.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

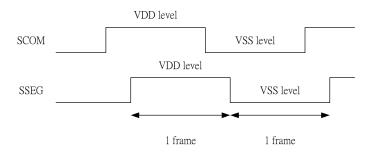

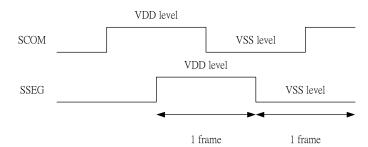

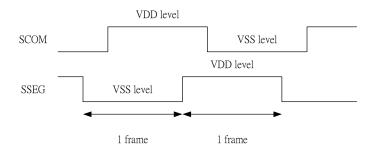

| SCOM<br>SSEG    | 0   | LCD driver output pin for static driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

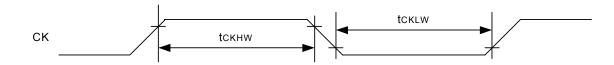

6.5 Oscillating Circuit Pin

| Symbol | I/O | Description                                                                                                                              |

|--------|-----|------------------------------------------------------------------------------------------------------------------------------------------|

| CKS    | Ι   | Display timing clock source select input pin.<br>CKS = "H": Use external clock from CK pin.<br>CKS = "L": Use internal oscillated clock. |

| CK     | Ι   | External clock input pin for display timing. When use internal clock, fix the CK pin at "L".                                             |

# 7. Functional Description

#### 7.1 MPU Interface

#### 7.1.1 Selection of Interface Type

The EM65100 transfers data through 8-bit parallel I/O (D7-D0) or serial data input (SDA, SCL). The parallel interface or serial interface can select by state of P/S pin. When select serial interface, data reading cannot be performed, only data writing can operate.

| P/S | I/F Type | CSB | RS | RDB | WRB | M86 | SDA | SCL | Data  |

|-----|----------|-----|----|-----|-----|-----|-----|-----|-------|

| Н   | Parallel | CSB | RS | RDB | WRB | M86 | -   | -   | D7~D0 |

| L   | Serial   | CSB | RS | -   | -   | -   | SDA | SCL | -     |

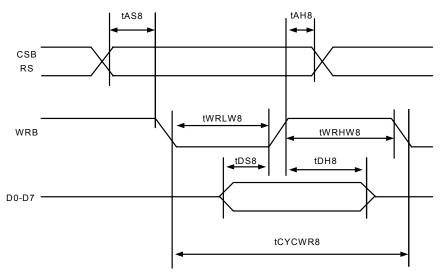

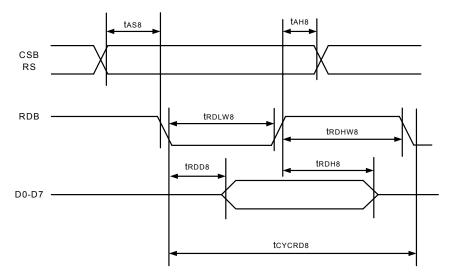

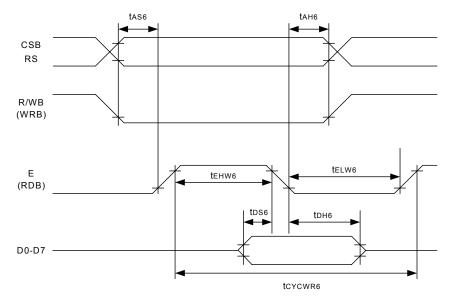

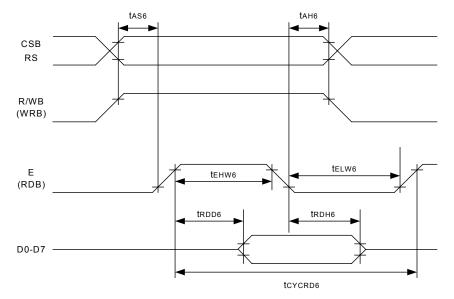

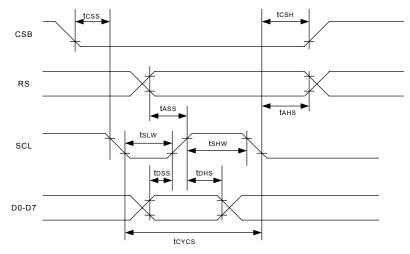

#### 7.1.2 Parallel Input

When parallel interface is selected with the P/S pin, the EM65100 allows data to be transferred in parallel to an 8-bit MPU through the data bus. For the 8-bit MPU, either the 80-family MPU interface or the 68-family MPU interface can be selected with the m86 pin.

| M86 | МРИ Туре      | CSB | RS | RDB | WRB  | Data  |

|-----|---------------|-----|----|-----|------|-------|

| Н   | 68-family MPU | CSB | RS | Е   | R/WB | D7~D0 |

| L   | 80-family MPU | CSB | RS | RDB | WRB  | D7~D0 |

#### 7.1.3 Read/Write functions of Register and display RAM

The EM65100 have four read/write functions at parallel interface mode. Each read/write function select by combinations of RS, RDB and WRB signals.

| RS | 68-family | 80-fan  | ıily | Function                |  |  |

|----|-----------|---------|------|-------------------------|--|--|

| ЛЭ | R/WB      | RDB WRB |      | Tunction                |  |  |

| 1  | 1         | 0       | 1    | Read internal Register  |  |  |

| 1  | 0         | 1       | 0    | Write internal Register |  |  |

| 0  | 1         | 0       | 1    | Read display data       |  |  |

| 0  | 0         | 1       | 0    | Write display data      |  |  |

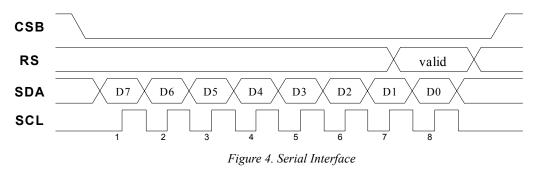

#### 7.1.4 Serial Interface

The serial interface of EM65100 can accept inputs of SDA and SCL in the state of chip select (CSB="L"). When not in the state of chip select. The internal shift register and counter are reset in the initial condition. Serial data SDA are input sequentially in order of D7 to D0 at the rising of serial clock (SCL) and are converted into 8-bit parallel data (by serial to parallel conversion) at the rising edge of the 8<sup>th</sup> serial clock, being processed in accordance with the data. The identification whether are serial data inputs (SDA) are display data or control register data is judged by input to RS pin.

RS = "L": display RAM data

#### RS = "H": control register data

After completing 8-bit data transferring, or when making no access, be sure to set serial clock input (SCL) to "L". Cares of SDA and SCL signals against external noise should be taken in board wiring. To prevent transfer error due to external noise, release chip select (CSB = "H") every completion of 8-bit data transferring.

When serial interface is used, access is only made for 8-bit data transfer.

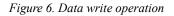

#### 7.2 Data write to Display RAM and Control Register

The data write to display RAM and Control Register use almost same procedure, only different setting of RS that select access object.

RS = "L": Display RAM data

RS = "H": Control register data

In the case of the 80-family MPU, the data is written at the rising edge of WRB. In the case of the 68-family MPU, the data is written at the falling edge of signal E.

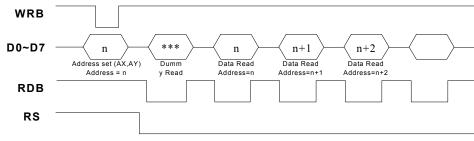

#### 7.3 Internal Register Read

In the case of display RAM read operation, need dummy read one time. The designated address data are not output to read operation immediately after the address set to AX or AY register, but are output when the second data read. Dummy read is always required one time after address set and write cycle.

Read display RAM operation

#### Figure 7. Read display RAM operation

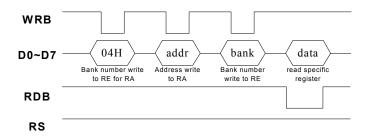

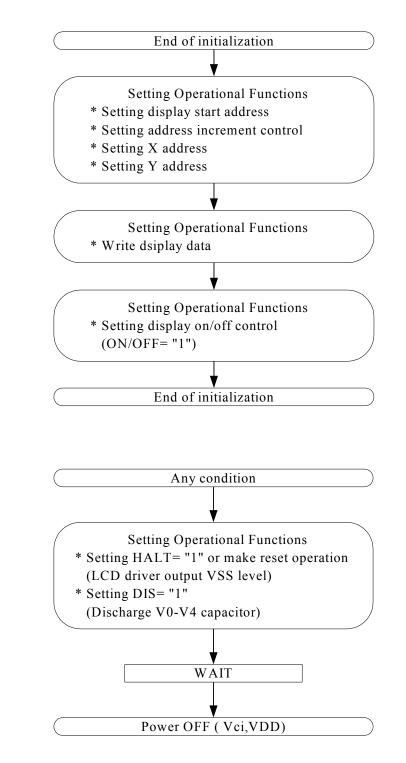

The EM65100 can be read the control registers, in case of control register read operation, data bus upper nibble (D3-D0) use for register address (0 to FH). In maximum, 16 registers can access directly. But number of register is more than 16 registers. Therefore, EM65100 has register bank control. The RE register is set bank number to access. And the RE address is 0FH, in any bank can access RE register. It is need 4-steps to read the specific register in maximum case.

- (1) Write 02H to RE register for access to RA register.

- (2) Writes specific register address to RA register.

- (3) Write specific register bank to RE register.

- (4) Read specific register contents.

Register read operation

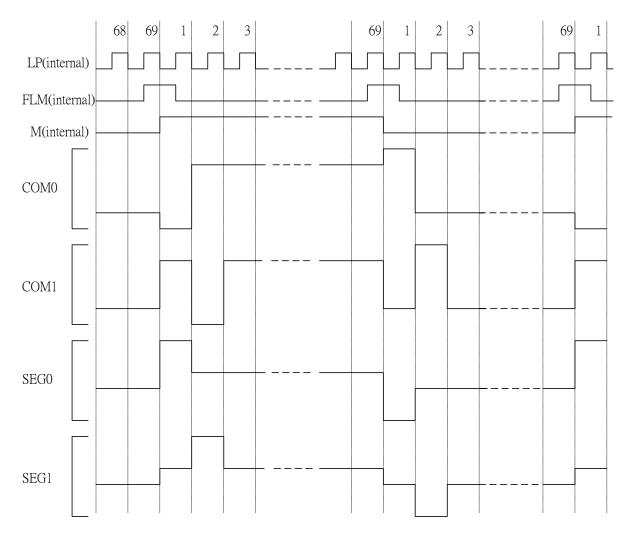

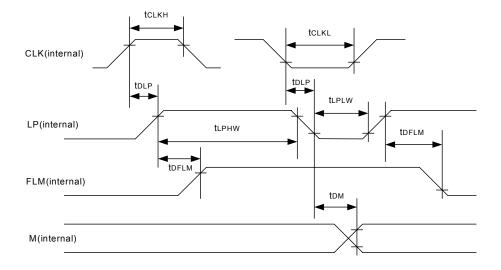

#### 7.4 Display Start Address Register

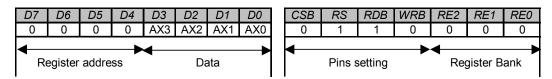

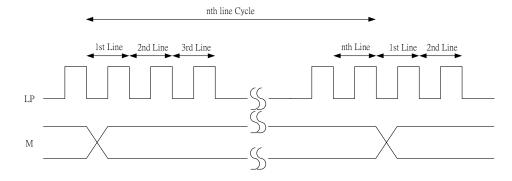

This register determines the Y-address of the display RAM corresponding to the display start line. The display RAM data that addressed Display Start Address register output to common driver start line. The actual common start line of LCD panel depend on Display Start Common register and SHIFT bit of Display Control register. The register are preset every timing of FLM signal variation in the display line counter. The line counter counts up being synchronized with LP input and generates line addresses which read out sequentially 288 bits data from display RAM to LCD drive circuit.

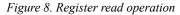

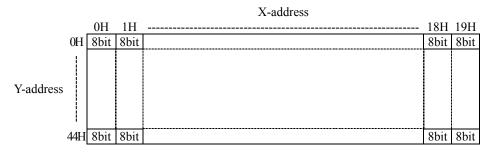

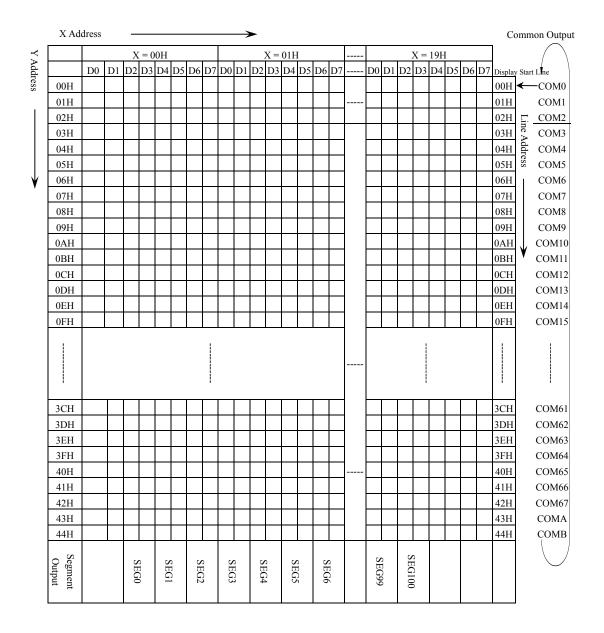

#### 7.5 Addressing of Display RAM

The EM65100 has built-in bit mapped display RAM. The display RAM consists of 208 bits in the X-direction and 69 bits in the Y-direction. In the gradation display mode, the EM65100 provides segment driver output for 4-gradation display using 2 bits. When connected to an STN LCD panel, the EM65100 can display 101\*69 pixels with 4-gradation display. The address area in the X-direction depends on the access bus size. When use 8-bits bus size, can access 00H to 19H address. In the X-direction, X Address register use to access; and in the Y-direction, Y Address register use to access. Do not specify any address outside the effective address area in each access mode because it is not permitted.

#### In Gradation Display Mode (MON="0")

8-bits bus size access

The addresses, X Address and Y Address are possible to be set up so that they can increment automatically with the address control register. The increment is made every time display RAM is read or written from MPU. In the Y-direction, 208 bits of data are read out to the display data latch circuit by internal operation when the LP rises in a one-line cycle. They are output from the display data latch circuit when the LP fails. When FLM signals being output in one frame cycle are at "H", the values in the display starting line register are preset in the line counter and the line counter counts up at the falling of LP signals. The display line address counter is synchronized with each timing signal of the LCD system to operate and is independent of address counters X and Y.

#### 7.6 Display RAM Data and LCD (only monochrome mode)

One bit of display RAM data corresponds to one dot of LCD. Normal display and reverse display by REV register are set up as follows.

Normal display (REV=0): RAM data = "0" not lighted RAM data = "1" lighted Reverse display (REV=1): RAM data = "0" lighted RAM data = "1" not lighted

#### 7.7 Segment Display Output Order/Reverse Set up

The order of display output, SEG0 to SEG100 can be reversed. If REF control bit set to "1", display by reversing access to display RAM from MPU by using REF register, lessen the limitation in placing IC when assembling an LCD panel module.

#### 7.8 Relationship between Display RAM and Address

The Display RAM block diagram shows in the figure below:

Figure 10. The Display RAM block diagram

The EM65100 execute address conversion that depends on control register setting. In case of auto increment mode, usually AX register is added one. For instance when REF and AXI are both "1", AX register is added one, but effective X address seems decrement because of address conversion. The effective Y address use AY register values as it is.

#### (1) Monochrome mode, 8-bits Access mode

|           | X Addre        | ess |    |      |      |      |   |      |    |      | $\rightarrow$ |      |      |      |    |      |    |           |    |        |     |     |   |    |    |         |              |           |              |

|-----------|----------------|-----|----|------|------|------|---|------|----|------|---------------|------|------|------|----|------|----|-----------|----|--------|-----|-----|---|----|----|---------|--------------|-----------|--------------|

|           | REF=1          |     |    | , ,  | X =( | )CH  | [ |      |    |      |               |      | X =( | )BH  | [  |      |    |           |    | 2      | K = | 00H | [ |    |    |         |              |           |              |

| ΥA        | REF=0          |     |    | 2    | X =  | 00H  | [ |      |    |      |               | 2    | X =  | 01H  | [  |      |    |           |    |        |     | 0CH |   |    |    |         | Co           | ommon Ou  | tput         |

| Y Address | Note 1         | D6  | D7 |      |      |      |   | D0   | D1 | D6   | D7            | D4   | D5   | D2   | D3 | D0   | D1 | <br>D6    | D7 |        |     |     |   | D0 | D1 |         |              | $\bigcap$ | $\backslash$ |

| SS        | Note 2         |     |    |      |      |      |   |      |    | D0   |               |      |      |      |    |      |    |           |    |        |     |     |   |    |    | Display | / Star       | t Line    |              |

|           | 00H            |     |    |      |      |      |   |      |    |      |               |      |      |      |    |      |    |           |    |        |     |     |   |    |    |         |              | -COM0     |              |

|           | 01H            |     |    |      |      |      |   |      |    |      |               |      |      |      |    |      |    |           |    |        |     |     |   |    |    | 01H     |              | COM1      |              |

|           | 02H            |     |    |      |      |      |   |      |    |      |               |      |      |      |    |      |    |           |    |        |     |     |   |    |    | 02H     | Ŀ            | COM2      |              |

|           | 03H            |     |    |      |      |      |   |      |    |      |               |      |      |      |    |      |    |           |    |        |     |     |   |    |    | 03H     | ne A         | COM3      |              |

|           | 04H            |     |    |      |      |      |   |      |    |      |               |      |      |      |    |      |    |           |    |        |     |     |   |    |    | 04H     | Line Address | COM4      |              |

| V         | 05H            |     |    |      |      |      |   |      |    |      |               |      |      |      |    |      |    |           |    |        |     |     |   |    |    | 05H     | ess          | COM5      |              |

| •         | 06H            |     |    |      |      |      |   |      |    |      |               |      |      |      |    |      |    |           |    |        |     |     |   |    |    | 06H     | T            | COM6      |              |

|           | 07H            |     |    |      |      |      |   |      |    |      |               |      |      |      |    |      |    |           |    |        |     |     |   |    |    | 07H     |              | COM7      |              |

|           | 08H            |     |    |      |      |      |   |      |    |      |               |      |      |      |    |      |    |           |    |        |     |     |   |    |    | 08H     |              | COM8      |              |

|           | 09H            |     |    |      |      |      |   |      |    |      |               |      |      |      |    |      |    |           |    |        |     |     |   |    |    | 09H     |              | COM9      |              |

|           | 0AH            |     |    |      |      |      |   |      |    |      |               |      |      |      |    |      |    |           |    |        |     |     |   |    |    | 0AH     | $\downarrow$ | COM10     |              |

|           | 0BH            |     |    |      |      |      |   |      |    |      |               |      |      |      |    |      |    |           |    |        |     |     |   |    |    | 0BH     | v            | COM11     |              |

|           | 0CH            |     |    |      |      |      |   |      |    |      |               |      |      |      |    |      |    |           |    |        |     |     |   |    |    | 0CH     |              | COM12     |              |

|           | 0DH            |     |    |      |      |      |   |      |    |      |               |      |      |      |    |      |    |           |    |        |     |     |   |    |    | 0DH     |              | COM13     |              |

|           | 0EH            |     |    |      |      |      |   |      |    |      |               |      |      |      |    |      |    |           |    |        |     |     |   |    |    | 0EH     |              | COM14     |              |

|           | 0FH            |     |    |      |      |      |   |      |    |      |               |      |      |      |    |      |    |           |    |        |     |     |   |    |    | 0FH     |              | COM15     |              |

|           |                |     |    |      |      |      |   |      |    |      |               |      |      |      |    |      |    |           |    |        |     |     |   |    |    |         |              |           |              |

|           | 3CH            |     |    |      |      |      |   |      |    |      |               |      |      |      |    |      |    |           |    |        |     |     |   |    |    | 3CH     |              | COM61     |              |

|           | 3DH            |     |    |      |      |      |   |      |    |      |               |      |      |      |    |      |    |           |    |        |     |     |   |    |    | 3DH     |              | COM62     |              |

|           | 3EH            |     |    |      |      |      |   |      |    |      |               |      |      |      |    |      |    |           |    |        |     |     |   |    |    | 3EH     |              | COM63     |              |

|           | 3FH            |     |    |      |      |      |   |      |    |      |               |      |      |      |    |      |    |           |    |        |     |     |   |    |    | 3FH     |              | COM64     |              |

|           | 40H            |     |    |      |      |      |   |      |    |      |               |      |      |      |    |      |    |           |    |        |     |     |   |    |    | 40H     |              | COM65     |              |

|           | 41H            |     |    |      |      |      |   |      |    |      |               |      |      |      |    |      |    |           |    |        |     |     |   |    |    | 41H     |              | COM66     |              |

|           | 42H            |     |    |      |      |      |   |      |    |      |               |      |      |      |    |      |    |           |    |        |     |     |   |    |    | 42H     |              | COM67     |              |

|           | 43H            |     |    |      |      |      |   |      |    |      |               |      |      |      |    |      |    |           |    |        |     |     |   |    |    | 43H     |              | COMA      |              |

|           | 44H            |     |    |      |      |      |   |      |    |      |               |      |      |      |    |      |    |           |    |        |     |     |   |    |    | 44H     |              | COMB      |              |

|           | Segment Output |     |    | SEG0 |      | SEG1 |   | SEG2 |    | SEG3 |               | SEG4 |      | SEGO |    | SEG6 |    | <br>SEC99 |    | SEG100 |     |     |   |    |    |         |              |           | )            |

Note1: REF=1 Note2: REF=0

(2)Gradation mode, 8 bits access mode, REF = 0

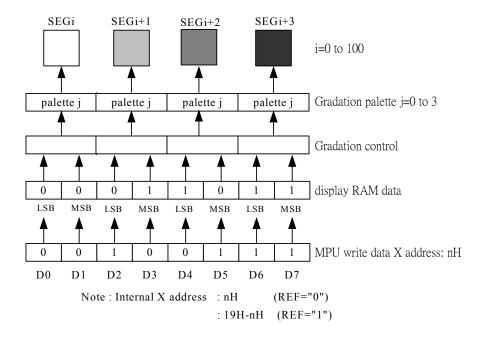

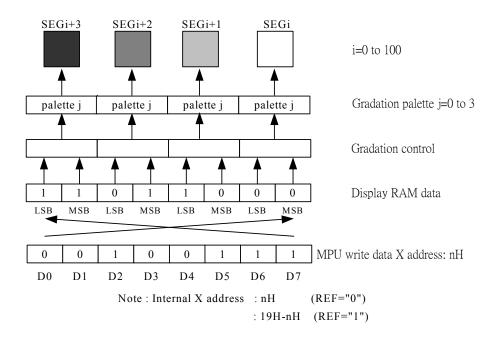

#### 7.9 Display Data Structure and Gradation Control

For the purpose of gradation control, one pixel requires multiple bits of display RAM. The EM65100 has 2-bit data per output to achieve the gradation display.

The EM65100 is connected to an STN LCD panel. It can display 101\*69 pixels with 4-gray level. In this case, since the gradation display data is processed by a single access to the memory, the data can be rewritten fast and naturally.

The weighting for each data bit is dependent on the status of the REF bit that is selected when data is written to the display RAM.

• REF=0

• REF=1

#### 7.10 Gradation Palette

The EM65100 has two gradation display modes, the gradation fixed display mode and the gradation variable display mode. Select either of the two modes using the gradation display mode register.

PWM = "0": Selects the variable display mode using 4 gradation selected from 16 gradation.

PWM = "1": Selects the fixed display mode using specific 4 gradation.

To select the best gradation level suited to the LCD panel, use the gradation palette register among the 16-level gradation palettes in the gradation variable display mode. The segment driver output is set up by the selected 4-levels of gradation palettes.

Each register consists of a 2-bit register, selecting 4-gradations from the pattern for 16-gradations.

Initial values on gradation palette register

| _ |           |            |                     |               |

|---|-----------|------------|---------------------|---------------|

|   | (MSB) RAM | data (LSB) | Register Name       | Initial value |

|   | 0         | 0          | Gradation Palette 0 | 0000          |

|   | 0         | 1          | Gradation Palette 1 | 0101          |

|   | 1         | 0          | Gradation Palette 2 | 1010          |

|   | 1         | 1          | Gradation Palette 3 | 1111          |

[Three groups of palettes WAj~WDj, LAj~LDj, DAj~DDj, and BAj~BDj are available]

Gradation level table (PWM = "0", variable mode)

| ETT1 C 1 44                 | $\mathbf{W}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 2)              |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| I I hree groups of palettes | s WAj~WDj, LAj~LDj, DAj~DDj, and BAj~BDjand Cj (j=0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | - 1 are available |

| I mee groups of parenes     | $\mathcal{O}$ |                   |

|                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                   |

| Palette | Gradation level | Remark              |