# PB51 • PB51A

HTTP://WWW.APEXMICROTECH.COM (800) 546-APEX (800) 546-2739

### **FEATURES**

- WIDE SUPPLY RANGE ±15V to ±150V

- HIGH OUTPUT CURRENT

- 1.5A Continuous (PB51), 2.0A Continuous (PB51A)

- VOLTAGE AND CURRENT GAIN

- HIGH SLEW 50V/µs Minimum (PB51) 75V/µs Minimum (PB51A)

- PROGRAMMABLE OUTPUT CURRENT LIMIT

- HIGH POWER BANDWIDTH 320 kHz Minimum

- LOW QUIESCENT CURRENT 12mA Typical

- EVALUATION KIT EK29

## **APPLICATIONS**

- HIGH VOLTAGE INSTRUMENTATION

- ELECTROSTATIC TRANSDUCERS & DEFLECTION

- PROGRAMMABLE POWER SUPPLIES UP TO 280V P-P

### **DESCRIPTION**

The PB51 is a high voltage, high current amplifier designed to provide voltage and current gain for a small signal, general purpose op amp. Including the power booster within the feedback loop of the driver amplifier results in a composite amplifier with the accuracy of the driver and the extended output voltage range and current capability of the booster. The PB51 can also be used without a driver in some applications, requiring only an external current limit resistor to function properly.

The output stage utilizes complementary MOSFETs, providing symmetrical output impedance and eliminating second breakdown limitations imposed by Bipolar Transistors. Internal feedback and gainset resistors are provided for a pin-strapable gain of 3. Additional gain can be achieved with a single external resistor. Compensation is not required for most driver/gain configurations, but can be accomplished with a single external capacitor. Enormous flexibility is provided through the choice of driver amplifier, current limit, supply voltage, voltage gain, and compensation.

This hybrid circuit utilizes a beryllia (BeO) substrate, thick film resistors, ceramic capacitors and semiconductor chips to maximize reliability, minimize size and give top performance. Ultrasonically bonded aluminum wires provide reliable interconnections at all operating temperatures. The 12-pin Power SIP package is electrically isolated.

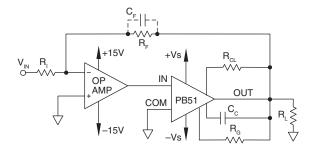

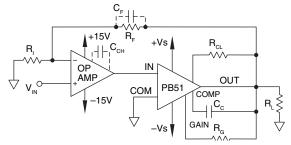

### TYPICAL APPLICATION

12-PIN SIP

PACKAGE STYLE DP

Formed leads available. See package styles ED & EE

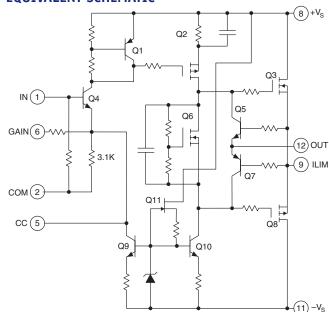

## **EQUIVALENT SCHEMATIC**

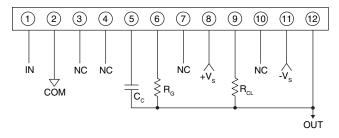

### **EXTERNAL CONNECTIONS**

## PB51 • PB51A

### **ABSOLUTE MAXIMUM RATINGS**

SUPPLY VOLTAGE,  $+V_{_{\rm S}}$  to  $-V_{_{\rm S}}$  OUTPUT CURRENT, within SOA 300V 2.0A POWER DISSIPATION, internal at  $T_C = 25^{\circ}C^{1}$ 83W INPUT VOLTAGE, referred to COM ±15V TEMPERATURE, pin solder—10s max. 260°C TEMPERATURE, junction<sup>1</sup> 175°C TEMPERATURE RANGE, storage -40 to +85°C OPERATING TEMPERATURE RANGE, case -25 to +85°C

### **SPECIFICATIONS**

| 31 ECTITIONS                                                                                                                                                                                     |                                                                                                                                                                                         |                                     | PB51                                                        |                                 |                 | PB51A                             |                |                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-------------------------------------------------------------|---------------------------------|-----------------|-----------------------------------|----------------|-----------------------------------------------|

| PARAMETER                                                                                                                                                                                        | TEST CONDITIONS <sup>2</sup>                                                                                                                                                            | MIN                                 | TYP                                                         | MAX                             | MIN             | TYP                               | MAX            | UNITS                                         |

| INPUT OFFSET VOLTAGE, initial OFFSET VOLTAGE, vs. temperature INPUT IMPEDANCE, DC INPUT CAPACITANCE CLOSED LOOP GAIN RANGE GAIN ACCURACY, internal Rg, Rf GAIN ACCURACY, external Rf PHASE SHIFT | Full temperature range <sup>3</sup> AV = 3  AV = 10  f = 10kHz, AVC <sub>L</sub> = 10, CC = 22pF f = 200kHz, AVC <sub>L</sub> = 10, CC = 22pF                                           | 25<br>3                             | ±.75<br>-4.5<br>50<br>3<br>10<br>±10<br>±15<br>10           | ±1.75<br>-7<br>25<br>±15<br>±25 | *               | * * * * * * * * *                 | ±1.0 * * * * * | V<br>mV/°C<br>k<br>pF<br>V/V<br>%             |

| OUTPUT  VOLTAGE SWING  VOLTAGE SWING  VOLTAGE SWING  CURRENT, continuous  SLEW RATE  CAPACITIVE LOAD  SETTLING TIME to .1%  POWER BANDWIDTH  SMALL SIGNAL BANDWIDTH  SMALL SIGNAL BANDWIDTH      | Io = 1.5A (PB58), 2A (PB58A) Io = 1A Io = .1A  Full temperature range Full temperature range RL = 100, 2V step VC = 100 Vpp CC = 22pF, AV = 25, Vcc = ±100 CC = 22pF, AV = 3, Vcc = ±30 | VS-11<br>VS-10<br>VS-8<br>1.5<br>50 | VS-8<br>VS-7<br>VS-5<br>100<br>2200<br>2<br>320<br>100<br>1 |                                 | VS-15  * 2.0 75 | VS-11 * * * * * * * * * * * * * * |                | V<br>V<br>A<br>V/µs<br>pF<br>µs<br>kHz<br>kHz |

| POWER SUPPLY<br>VOLTAGE, ±VS <sup>4</sup><br>CURRENT, quiescent                                                                                                                                  | Full temperature range<br>$VS = \pm 15$<br>$VS = \pm 60$<br>$VS = \pm 150$                                                                                                              | ±15 <sup>6</sup>                    | ±60<br>11<br>12<br>14                                       | ±150                            | *               | * * *                             | *              | V<br>mA<br>mA<br>mA                           |

| THERMAL RESISTANCE, AC junction to case5 RESISTANCE, DC junction to case RESISTANCE, junction to air TEMPERATURE RANGE, case                                                                     | Full temp. range, f > 60Hz Full temp. range, f < 60Hz Full temperature range Meets full range specifications                                                                            | -25                                 | 1.2<br>1.6<br>30<br>25                                      | 1.3<br>1.8<br>85                | *               | *<br>*<br>*                       | * *            | °C/W<br>°C/W<br>°C/W                          |

- The specification of PB51A is identical to the specification for PB51 in applicable column to the left.

- 1. Long term operation at the maximum junction temperature will result in reduced product life. Derate internal power dissipation to achieve high MTTF (Mean Time to Failure).

- The power supply voltage specified under typical (TYP) applies,  $T_C = 25$ °C unless otherwise noted.

- 3. Guaranteed by design but not tested.

- +V<sub>s</sub> and -V<sub>s</sub> denote the positive and negative supply rail respectively.

- 5. Rating applies if the output current alternates between both output transistors at a rate faster than 60Hz.

- 6. +V<sub>S</sub>/-V<sub>S</sub> must be at least 15V above/below COM.

**CAUTION** The PB51 is constructed from MOSFET transistors. ESD handling procedures must be observed.

The internal substrate contains beryllia (BeO). Do not break the seal. If accidentally broken, do not crush, machine, or subject to temperatures in excess of 850°C to avoid generating toxic fumes.

# PB51 • PB51A

### **GENERAL**

Please read Application Note 1 "General Operating Considerations" which covers stability, supplies, heat sinking, mounting, current limit. SOA interpretation, and specification interpretation. Visit www.apexmicrotech.com for design tools that help automate tasks such as calculations for stability, internal power dissipation, current limit; heat sink selection; Apex's complete Application Notes library; Technical Seminar Workbook; and Evaluation Kits.

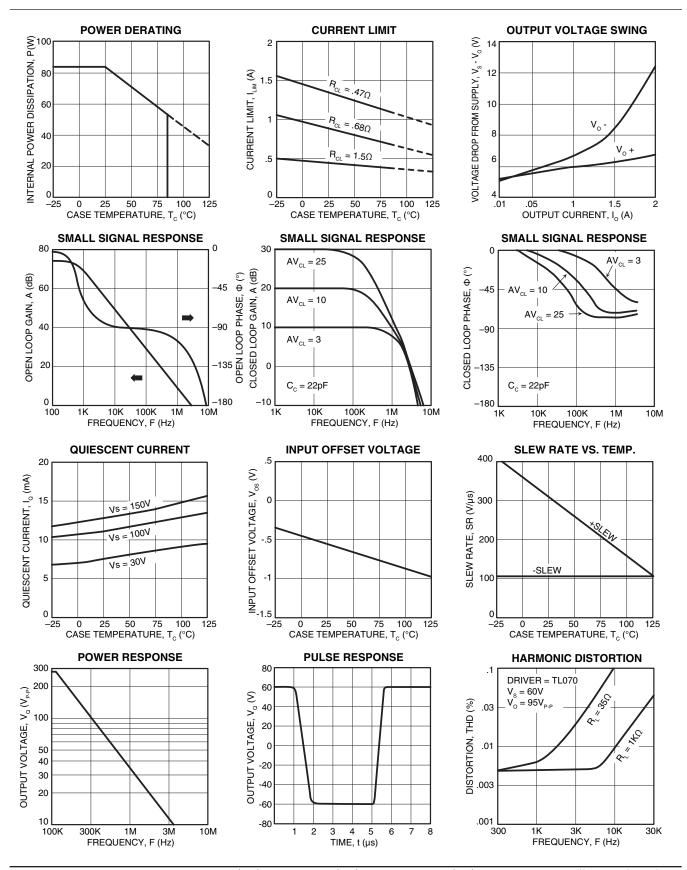

### **CURRENT LIMIT**

For proper operation, the current limit resistor (R<sub>CI</sub>) must be connected as shown in the external connection diagram. The minimum value is 0.33 with a maximum practical value of 47. For optimum reliability the resistor value should be set as high as possible. The value is calculated as follows:

$$+I_{L}=.65/R_{CL}+.010, -I_{L}=.65/R_{CL}.$$

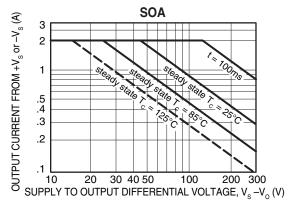

### SAFE OPERATING AREA

NOTE: The output stage is protected against transient flyback. However, for protection against sustained, high energy flyback, external fast-recovery diodes should be used.

### COMPOSITE AMPLIFIER CONSIDERATIONS

Cascading two amplifiers within a feedback loop has many advantages, but also requires careful consideration of several amplifier and system parameters. The most important of these are gain, stability, slew rate, and output swing of the driver. Operating the booster amplifier in higher gains results in a higher slew rate and lower output swing requirement for the driver, but makes stability more difficult to achieve.

### **GAIN SET**

$$R_G = [(Av-1) \cdot 3.1K] - 6.2K$$

$$Av = \frac{R_G + 6.2K}{3.1K} + 1$$

The booster's closed-loop gain is given by the equation above. The composite amplifier's closed loop gain is determined by the feedback network, that is: -Rf/Ri (inverting) or 1+Rf/Ri (non-inverting). The driver amplifier's "effective gain" is equal to the composite gain divided by the booster gain.

Example: Inverting configuration (figure 1) with R i = 2K, R f = 60K, R g = 0:

Av (booster) =

$$(6.2K/3.1K) + 1 = 3$$

Av (composite) =  $60K/2K = -30$

Av (driver) =  $-30/3 = -10$

### **STABILITY**

Stability can be maximized by observing the following quidelines:

- 1. Operate the booster in the lowest practical gain.

- 2. Operate the driver amplifier in the highest practical effective

- 3. Keep gain-bandwidth product of the driver lower than the closed loop bandwidth of the booster.

- 4. Minimize phase shift within the loop.

A good compromise for (1) and (2) is to set booster gain from 3 to 10 with total (composite) gain at least a factor of 3 times booster gain. Guideline (3) implies compensating the driver as required in low composite gain configurations. Phase shift within the loop (4) is minimized through use of booster and loop compensation capacitors Cc and Cf when required. Typical values are 5pF to 33pF.

Stability is the most difficult to achieve in a configuration where driver effective gain is unity (ie; total gain = booster gain). For this situation, Table 1 gives compensation values for optimum square wave response with the op amp drivers listed.

| DRIVER                                                                 | C <sub>CH</sub> | C <sub>F</sub> | C <sub>C</sub> | FPBW  | SR  |  |  |  |

|------------------------------------------------------------------------|-----------------|----------------|----------------|-------|-----|--|--|--|

| OP07                                                                   | _               | 22p            | 22p            | 4kHz  | 1.5 |  |  |  |

| 741                                                                    | -               | 18p            | 10p            | 20kHz | 7   |  |  |  |

| LF155                                                                  | -               | 4.7p           | 10p            | 60kHz | >60 |  |  |  |

| LF156                                                                  | -               | 4.7p           | 10p            | 80kHz | >60 |  |  |  |

| TL070                                                                  | 22p             | 15p            | 10p            | 80kHz | >60 |  |  |  |

| For: R <sub>F</sub> = 33K, R <sub>I</sub> = 3.3K, R <sub>G</sub> = 22K |                 |                |                |       |     |  |  |  |

TABLE 1.TYPICAL VALUES FOR CASE WHERE OP AMP EFFECTIVE GAIN = 1.

FIGURE 2. NON-INVERTING COMPOSITE AMPLIFIER.

### **SLEW RATE**

The slew rate of the composite amplifier is equal to the slew rate of the driver times the booster gain, with a maximum value equal to the booster slew rate.

### **OUTPUT SWING**

The maximum output voltage swing required from the driver op amp is equal to the maximum output swing from the booster divided by the booster gain. The Vos of the booster must also be supplied by the driver, and should be subtracted from the available swing range of the driver. Note also that effects of Vos drift and booster gain accuracy should be considered when calculating maximum available driver swing.