# V•I Chip<sup>™</sup> – VTM Voltage Transformation Module

- 48 V to 3 V V•I Chip Converter

- 70 A (105 A for 1 ms)

- High density 284 A/in<sup>3</sup>

- Small footprint 60 A/in<sup>2</sup>

- Low weight 0.5 oz (14 g)

- Pick & Place / SMD

- 125°C operation

- 1 µs transient response

- 3.5 million hours MTBF

- Typical efficiency 94%

- No output filtering required

- Surface mount BGA or J-Lead packages

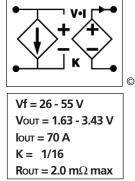

# V048K030T070

K indicates BGA configuration. For other

mounting options see Part Numbering below.

Actual size

# ROUT = 2.0 ms2 m

## **Product Description**

The V048K030T070 V•I Chip Voltage Transformation Module (VTM) breaks records for speed, density and efficiency to meet the demands of advanced DSP, FPGA, and ASIC at the point of load (POL) while providing isolation from input to output. It achieves a response time of less than 1  $\mu$ s and delivers up to 70 A in a volume of less than 0.25 in<sup>3</sup> with unprecedented efficiency. It may be paralleled to deliver hundreds of amps at an output voltage settable from 1.63 to 3.43 Vdc.

The VTM V048K030T070's nominal output voltage is 3 Vdc from a 48 Vdc input Factorized Bus, Vf, and is controllable from 1.63 to 3.43 Vdc at no load, and from 1.49 to 3.29 Vdc at full load, over a Vf input range of 26 to 55 Vdc. It can be operated either open- or closedloop depending on the output regulation needs of the application. Operating open-loop, the output voltage tracks its Vf input voltage with a transformation ratio, K = 1/16, for applications requiring a programmable output voltage at high current and high efficiency. Closing the loop back to an input Pre-Regulation Module (PRM) or DC-DC converter enables tight load regulation.

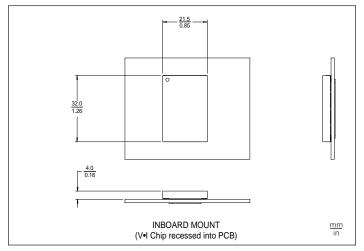

The 3 V VTM achieves break-through current density of 284 A/in<sup>3</sup> in a V•I Chip package compatible with standard pick-and-place and surface mount assembly processes. The V•I Chip BGA package supports in-board mounting with a low profile of 0.16" (4 mm) over the board. A J-lead package option supports on-board surface mounting with a profile of only 0.25" (6 mm) over the board. The VTM's fast dynamic response and low noise eliminate the need for bulk capacitance at the load, substantially increasing the POL density while improving reliability and decreasing cost.

# **Absolute Maximum Ratings**

| Parameter                                     | Values                   | Unit     | Notes                  |

|-----------------------------------------------|--------------------------|----------|------------------------|

| +In to -In                                    | -1.0 to 60               | Vdc      |                        |

| +In to -In                                    | 100                      | Vdc      | For 100 ms             |

| PC to -In                                     | -0.3 to 7.0              | Vdc      |                        |

| VC to -In                                     | -0.3 to 19.0             | Vdc      |                        |

| +Out to -Out                                  | -0.1 to 6.0              | Vdc      |                        |

| Isolation voltage                             | 2,250                    | Vdc      | Input to Output        |

| Output current                                | 70                       | А        | Continuous             |

| Peak output current                           | 105                      | А        | For 1 ms               |

| Output power                                  | 210                      | W        | Continuous             |

| Peak output power                             | 315                      | W        | For 1 ms               |

| Case temperature                              | 208                      | °C       | During reflow          |

| Operating junction temperature <sup>(1)</sup> | -40 to 125<br>-55 to 125 | °C<br>°C | T - Grade<br>M - Grade |

| Storage temperature                           | -40 to 150               | °C       | T - Grade              |

|                                               | -65 to 150               | °C       | M - Grade              |

#### Note:

The referenced junction is defined as the semiconductor having the highest temperature. This temperature is monitored by a shutdown comparator.

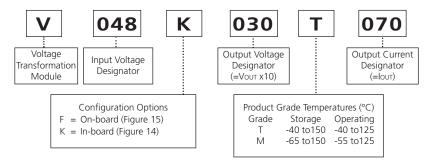

# **Part Numbering**

VICOR

vicorpower.com 800-735-6200 V•I Chip Voltage Transformation Module V048K030T070

Rev. 1.0

# **Electrical Specifications**

Input Specs (Conditions are at 48 Vin, full load, and 25°C ambient unless otherwise specified)

| Parameter                      | Min | Тур | Мах  | Unit   | Note                                            |

|--------------------------------|-----|-----|------|--------|-------------------------------------------------|

| Input voltage range            | 26  | 48  | 55   | Vdc    | Operable down to zero V with VC voltage applied |

| Input dV/dt                    |     |     | 1    | V/µs   |                                                 |

| Input overvoltage turn-on      | 55  |     |      | Vdc    |                                                 |

| Input overvoltage turn-off     |     |     | 60   | Vdc    |                                                 |

| Input current                  |     |     | 4.8  | Adc    |                                                 |

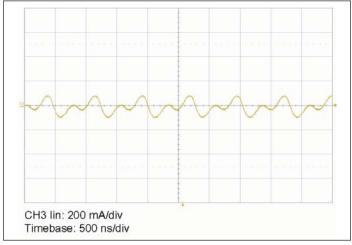

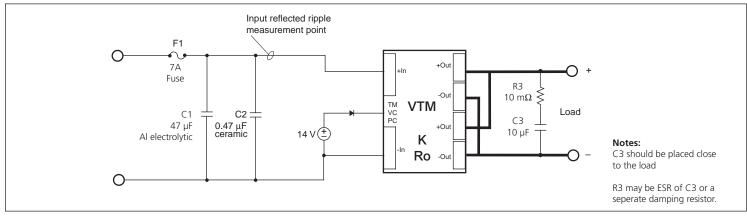

| Input reflected ripple current |     | 182 |      | mA p-p | Using test circuit in Figure 16; See Figure 1   |

| No load power dissipation      |     | 3.3 | 4.56 | W      |                                                 |

| Internal input capacitance     |     | 4   |      | μF     |                                                 |

| Internal input inductance      |     | 20  |      | nH     |                                                 |

#### Output Specs (Conditions are at 48 Vin, full load, and 25°C ambient unless otherwise specified)

| Parameter                     | Min    | Тур  | Мах    | Unit | Note                                                               |

|-------------------------------|--------|------|--------|------|--------------------------------------------------------------------|

| Output voltage                | 1.63   |      | 3.43   | Vdc  | No load                                                            |

| Output voltage                | 1.49   |      | 3.29   | Vdc  | Full load                                                          |

| Rated DC current              | 0      |      | 70     | Adc  |                                                                    |

| Peak repetitive current       |        |      | 105    | А    | Max pulse width 1ms, max duty cycle 10%, baseline power 50%        |

| DC current limit              | 71.4   | 87.1 | 94.5   | Adc  | Module will shut down when current limit is reached<br>or exceeded |

| Current share accuracy        |        | 5    | 10     | %    | See Parallel Operation on Page 10                                  |

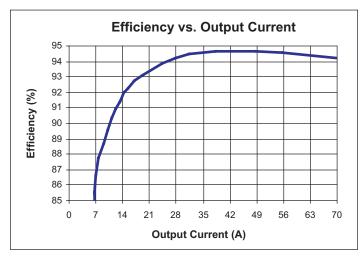

| Efficiency                    |        |      |        |      |                                                                    |

| Half load                     | 94.0   | 94.5 |        | %    | See Figure 3                                                       |

| Full load                     | 93.5   | 94.1 |        | %    | See Figure 3                                                       |

| Internal output inductance    |        | 1.1  |        | nH   |                                                                    |

| Internal output capacitance   |        | 254  |        | μF   | Effective value                                                    |

| Output overvoltage setpoint   | 3.4    |      |        | Vdc  |                                                                    |

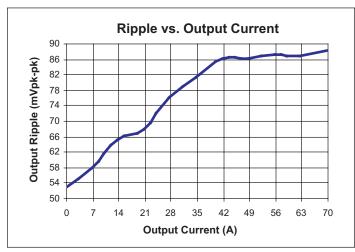

| Output ripple voltage         |        |      |        |      |                                                                    |

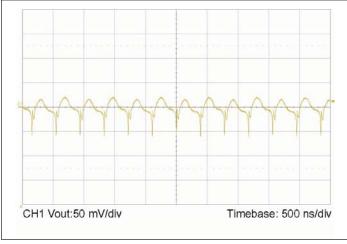

| No external bypass            |        | 80   | 100    | mV   | See Figures 2 and 5                                                |

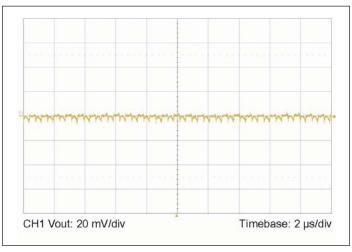

| 10 µF bypass capacitor        |        | 8.6  |        | mV   | See Figure 6                                                       |

| Effective switching frequency | 2.5    | 2.6  | 2.8    | MHz  | Fixed, 1.3 MHz per phase                                           |

| Line regulation               |        |      |        |      |                                                                    |

| K                             | 0.0619 | 1/16 | 0.0631 |      | Vou⊤ = K•VıN at no load                                            |

| Load regulation               |        |      |        |      |                                                                    |

| Rout                          |        | 1.8  | 2.0    | mΩ   | See Figure 19                                                      |

| Transient response            |        |      |        |      |                                                                    |

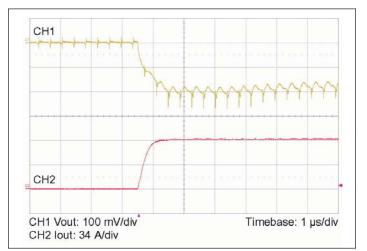

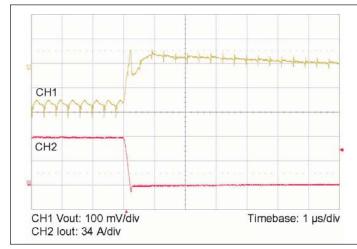

| Voltage overshoot             |        | 66   |        | mV   | 70 A load step with 100 $\mu F$ CIN; See Figures 7 and 8           |

| Response time                 |        | 200  |        | ns   | See Figures 7 and 8                                                |

| Recovery time                 |        | 1    |        | μs   | See Figures 7 and 8                                                |

## Electrical Specifications (continued)

### Waveforms

Figure 1— Input reflected ripple current at full load and 48 Vf.

Figure 3— Efficiency vs. output current at 48 Vf.

*Figure 5*— Output voltage ripple at full load and 3 Vout; without any external bypass capacitor.

*Figure 2*— Output voltage ripple vs. output current at 3 Vout with no POL bypass capacitance.

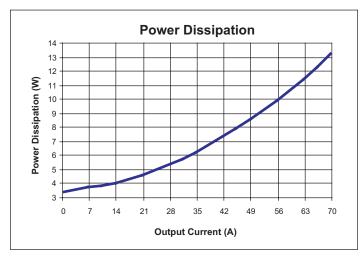

Figure 4—Power dissipation as a function of output current at 48 Vf.

**Figure 6**—Output voltage ripple at full load and 3 Vout with 10  $\mu$ F ceramic external bypass capacitance and 20 nH distribution inductance.

# Electrical Specifications (continued)

**Figure 7**— 0-70 A step load change with 47  $\mu$ F input capacitance and no output capacitance.

V•I Chip Voltage Transformation Module

**Figure 8**— 70-0 A step load change with 47  $\mu$ F input capacitance and no output capacitance.

# General

| Parameter                  | Min   | Тур        | Мах | Unit    | Note                                      |

|----------------------------|-------|------------|-----|---------|-------------------------------------------|

| MTBF                       |       |            |     |         |                                           |

| MIL-HDBK-217F              |       | 3.5        |     | Mhrs    | 25°C, GB                                  |

| Isolation specifications   |       |            |     |         |                                           |

| Voltage                    | 2,250 |            |     | Vdc     | Input to Output                           |

| Capacitance                |       | 3,000      |     | pF      | Input to Output                           |

| Resistance                 | 10    |            |     | MΩ      | Input to Output                           |

| Agency approvals (pending) |       | cTÜVus     |     |         | UL/CSA 60950, EN 60950                    |

|                            |       | CE Mark    |     |         | Low voltage directive                     |

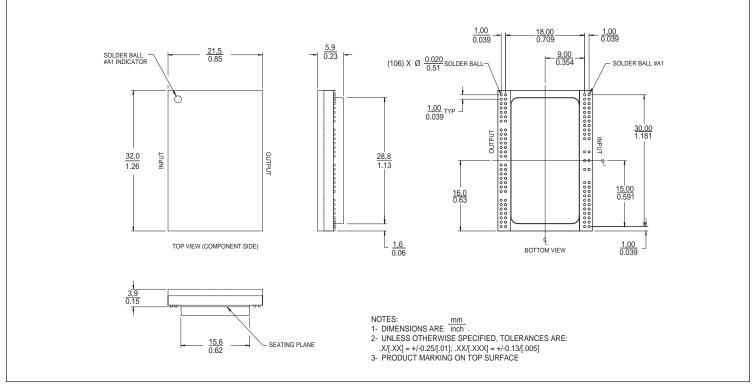

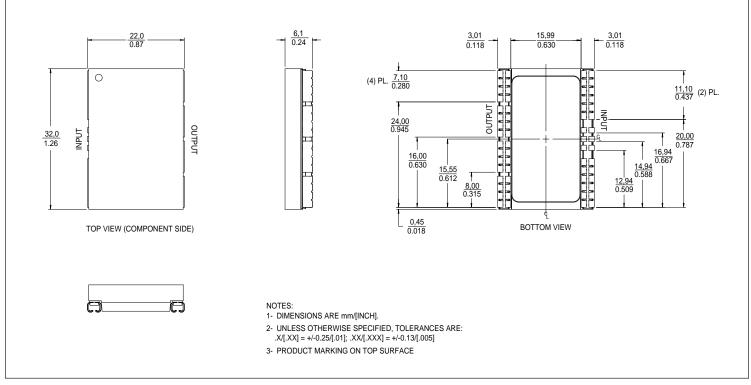

| Mechanical parameters      |       |            |     |         | See Mechanical Drawing, Figures 10 and 12 |

| Weight                     |       | 0.5/14.0   |     | oz / g  |                                           |

| Dimensions(BGA version)    |       |            |     |         |                                           |

| Length                     |       | 1.26 / 32  |     | in / mm |                                           |

| Width                      |       | 0.85/21.5  |     | in / mm |                                           |

| Height                     |       | 0.23 / 5.9 |     | in / mm |                                           |

Auxiliary Pins (Conditions are at 48 Vin, full load, and 25°C ambient unless otherwise specified)

| Parameter               | Min  | Тур  | Мах  | Unit | Note                                                       |

|-------------------------|------|------|------|------|------------------------------------------------------------|

| rimary Control (PC)     |      |      |      |      |                                                            |

| DC voltage              | 4.8  | 5.0  | 5.2  | Vdc  |                                                            |

| Module disable voltage  | 2.4  | 2.5  |      | Vdc  |                                                            |

| Module enable voltage   |      | 2.5  | 2.6  | Vdc  | VC voltage must be applied when module is enabled using PC |

| Current limit           | 2.4  | 2.5  | 2.9  | mA   | Source only                                                |

| Disable delay time      |      | 10   |      | μs   | PC low to Vout low                                         |

| /TM Control (VC)        |      |      |      |      |                                                            |

| External boost voltage  | 12.0 | 14.0 | 19.0 | Vdc  | Required for VTM start up without PRM                      |

| External boost duration |      | 10   |      | ms   | Vin > 26 Vdc. VC must be applied continuously              |

|                         |      |      |      |      | if Vin < 26 Vdc.                                           |

# Electrical Specifications (continued)

# Thermal

| Symbol | Parameter                          | Min | Тур  | Max | Unit  | Note                 |

|--------|------------------------------------|-----|------|-----|-------|----------------------|

|        | Over temperature shutdown          | 125 | 130  | 135 | °C    | Junction temperature |

|        | Thermal capacity                   |     | 0.61 |     | Ws/°C |                      |

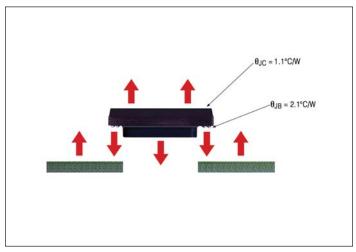

| Rejc   | Junction-to-case thermal impedance |     | 1.1  |     | °C/W  |                      |

| Rejb   | Junction-to-BGA thermal impedance  |     | 2.1  |     | °C/W  |                      |

| Reja   | Junction-to-ambient <sup>(1)</sup> |     | 6.5  |     | °C/W  |                      |

| Reja   | Junction-to-ambient <sup>(2)</sup> |     | 5.0  |     | °C/W  |                      |

#### Notes:

(1) V048K030T070 surface mounted in-board to a 2" x 2" FR4 board, 4 layers 2 oz Cu, 300 LFM.

(2) V048K030T070 with optional 0.25"H Pin Fins surface mounted on FR4 board, 300 LFM.

# **V•I Chip Stress Driven Product Qualification Process**

| Test                                                | Standard                                                | Environment                                                 |

|-----------------------------------------------------|---------------------------------------------------------|-------------------------------------------------------------|

| High Temperature Operational Life (HTOL)            | JESD22-A-108-B                                          | 125°C, Vmax, 1,008 hrs                                      |

| Temperature cycling                                 | JESD22-A-104B                                           | -55°C to 125°C, 1,000 cycles                                |

| High temperature storage                            | JESD22-A-103A                                           | 150°C, 1,000 hrs                                            |

| Moisture resistance                                 | JESD22-A113-B                                           | Moisture sensitivity Level 5                                |

| Temperature Humidity Bias Testing (THB)             | EIA/JESD22-A-101-B                                      | 85°C, 85% RH, Vmax, 1,008 hrs                               |

| Pressure cooker testing (Autoclave)                 | JESD22-A-102-C                                          | 121°C, 100% RH, 15 PSIG, 96 hrs                             |

| Highly Accelerated Stress Testing (HAST)            | JESD22-A-110B                                           | 130°C, 85% RH, Vmax, 96 hrs                                 |

| Solvent resistance/marking permanency               | JESD22-B-107-A                                          | Solvents A, B & C as defined                                |

| Mechanical vibration                                | JESD22-B-103-A                                          | 20g peak, 20-2,000 Hz, test in X, Y & Z directions          |

| Mechanical shock                                    | JESD22-B-104-A                                          | 1,500g peak 0.5 ms pulse duration, 5 pulses in 6 directions |

| Electro static discharge testing – human body model | EIA/JESD22-A114-A                                       | Meets or exceeds 2,000 Volts                                |

| Electro static discharge testing – machine model    | EIA/JESD22-A115-A                                       | Meets or exceeds 200 Volts                                  |

| Highly Accelerated Life Testing (HALT)              | Per Vicor Internal<br>Test Specification <sup>(1)</sup> | Operation limits verified, destruct margin determined       |

| Dynamic cycling                                     | Per Vicor internal test specification <sup>(1)</sup>    | Constant line, 0-100% load, -20°C to 125°C                  |

#### Note:

(1) For details of the test protocols see Vicor's website.

# **V•I Chip Ball Grid Array Interconnect Qualification**

| Test                          | Standard   | Environment                                        |

|-------------------------------|------------|----------------------------------------------------|

| BGA solder fatique evaluation | IPC-9701   | Cycle condition: TC3 (-40 to +125°C)               |

|                               | IPC-SM-785 | Test duration: NTC-B (500 failure free cycles)     |

| Solder ball shear test        | IPC-9701   | Failure through bulk solder or copper pad lift-off |

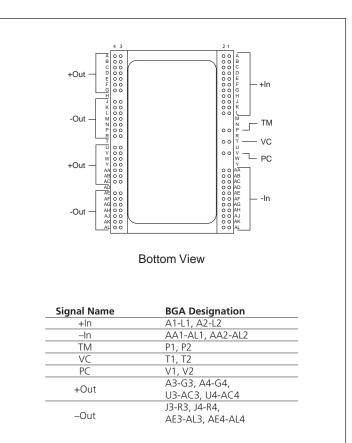

# **Pin/Control Functions**

#### V•I Chip Voltage Transformation Module

#### +IN/-IN DC Voltage Ports

The VTM input should not exceed the maximum specified. Be aware of this limit in applications where the VTM is being driven above its nominal output voltage. If less than 26 Vdc is present at the +In and -In ports, a continuous VC voltage must be applied for the VTM to process power. Otherwise VC voltage need only be applied for 10 ms after the voltage at the +In and -In ports has reached or exceeded 26 Vdc. If the input voltage exceeds the overvoltage turn-off, the VTM will shutdown. The VTM does not have internal input reverse polarity protection. Adding a properly sized diode in series with the positive input or a fused reverse-shunt diode will provide reverse polarity protection.

#### TM – For Factory Use Only

#### VC – VTM Control

The VC port is multiplexed. It receives the initial Vcc voltage from an upstream PRM, synchronizing the output rise of the VTM with the output rise of the PRM. Additionally, the VC port provides feedback to the PRM to compensate for the VTM output resistance. In typical applications using VTMs powered from PRMs, the PRM's VC port should be connected to the VTM VC port.

In applications where a VTM is being used without a PRM, 14 V must be supplied to the VC port for as long as the input voltage is below 26 V and for 10 ms after the input voltage has reached or exceeded 26 V. The VTM is not designed for extended operation below 26 V. The VC port should only be used to provide Vcc voltage to the VTM during startup.

#### PC – Primary Control

The Primary Control (PC) port is a multifunction port for controlling the VTM as follows:

Disable – If PC is left floating, the VTM output is enabled. To disable the output, the PC port must be pulled lower than 2.4 V, referenced to -In. Optocouplers, open collector transistors or relays can be used to control the PC port. Once disabled, 14 V must be re-applied to the VC port to restart the VTM.

Primary Auxiliary Supply – The PC port can source up to 2.4 mA at 5 Vdc.

#### +OUT/-OUT DC Voltage Output Ports

The output and output return are through two sets of contact locations. The respective +Out and –Out groups must be connected in parallel with as low an interconnect resistance as possible. Within the specified input voltage range, the Level 1 DC behavioral model shown in Figure 19 defines the output voltage of the VTM. The current source capability of the VTM is shown in the specification table.

To take full advantage of the VTM, the user should note the low output impedance of the device. The low output impedance provides fast transient response without the need for bulk POL capacitance. Limitedlife electrolytic capacitors required with conventional converters can be reduced or even eliminated, saving cost and valuable board real estate.

# **Mechanical Drawings**

Figure 10—VTM BGA mechanical outline; Inboard mounting

Figure 11— VTM BGA PCB land/VIA layout information; Inboard mounting

| <b>VICOR</b> | vicorpower.com | 800-735-6200 | V•I Chip Voltage Transformation Module | V048K030T070 | Rev. 1.0 |

|--------------|----------------|--------------|----------------------------------------|--------------|----------|

|--------------|----------------|--------------|----------------------------------------|--------------|----------|

## Mechanical Drawings (continued)

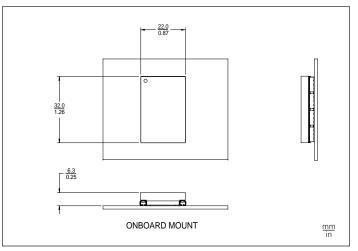

Figure 12—VTM J-Lead mechanical outline; Onboard mounting

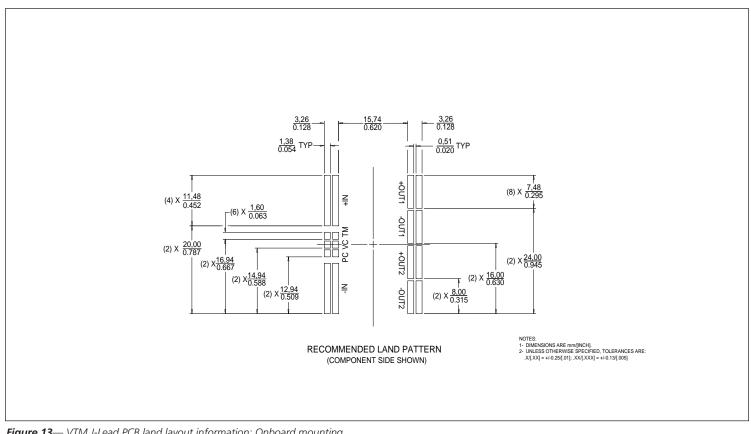

Figure 13— VTM J-Lead PCB land layout information; Onboard mounting

| VICOR | vicorpower.com | 800-735-6200 | V•I Chip Voltage Transformation Module | V048K030T070 | Rev. 1.0 |

|-------|----------------|--------------|----------------------------------------|--------------|----------|

|-------|----------------|--------------|----------------------------------------|--------------|----------|

۸ı

# **Configuration Option**

| Configuration                                 | <b>Inboard(1)</b><br>(Figure 14) | Onboard(1)<br>(Figure 15) | Inboard with 0.25"<br>Pin Fins <sup>(2)</sup> | Onboard with 0.25"<br>Pin Fins <sup>(2)</sup> |

|-----------------------------------------------|----------------------------------|---------------------------|-----------------------------------------------|-----------------------------------------------|

| Effective current density                     | 400 A/in <sup>3</sup>            | 250 A/in <sup>3</sup>     | 150 A/in <sup>3</sup>                         | 120 A/in <sup>3</sup>                         |

| Junction-Board<br>thermal resistance          | 2.1 °C/W                         | 2.4 °C/W                  | 2.1 °C/W                                      | 2.4 °C/W                                      |

| Junction-Case<br>thermal resistance           | 1.1 °C/W                         | 1.1 °C/W                  | N/A                                           | N/A                                           |

| Junction-Ambient<br>thermal resistance 300LFM | 6.5 °C/W                         | 6.8 °C/W                  | 5.0 °C/W                                      | 5.0 °C/W                                      |

#### Notes:

(1) Surface mounted to a 2" x 2" FR4 board, 4 layers 2 oz Cu

(2) Pin Fin heat sink available as a separate item

Figure 14—Inboard mounting – package K

Figure 15—Onboard mounting – package F

#### **CONFIGURATION OPTIONS** (continued)

Figure 16—VTM test circuit

# **Application Note**

#### **Parallel Operation**

In applications requiring higher current or redundancy, VTMs can be operated in parallel without adding control circuitry or signal lines. To maximize current sharing accuracy, it is imperative that the source and load impedance on each VTM in a parallel array be equal. If VTMs are being fed by an upstream PRM, the VC nodes of all VTMs must be connected to the PRM VC.

To achieve matched impedances, dedicated power planes within the PC board should be used for the output and output return paths to the array of paralleled VTMs. This technique is preferable to using traces of varying size and length.

The VTM power train and control architecture allow bi-directional power transfer when the VTM is operating within its specified ranges. Bi-directional power processing improves transient response in the event of an output load dump. The VTM may operate in reverse, returning output power back to the input source. It does so efficiently.

#### **Thermal Management**

The high efficiency of the VTM results in low power dissipation minimizing temperature rise, even at full output current. The heat generated within the internal semiconductor junctions is coupled through very low thermal resistances, R0<sub>JC</sub> and R0<sub>JB</sub> (see Figure 17), to the PC board allowing flexible thermal management.

CASE 1 Convection via optional Pin Fins to air (Pin Fins available as a separate item.)

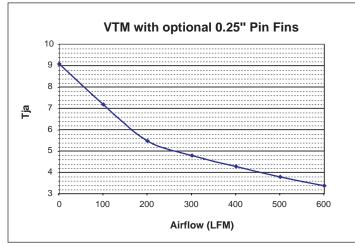

In an environment with forced convection over the surface of a PCB with 0.4" of headroom, a VTM with Pin Fins offers a simple thermal management option. The total Junction to Ambient thermal resistance of a surface mounted V048K030T070 with pin fins attached is 4.8 °C/W in 300 LFM airflow, (see Figure 18).

At 3 Vout and full rated current (70A), the VTM dissipates approximately 13 W per Figure 4. This results in a temperature rise of approximately 62 °C, allowing operation in an air temperature of 63 °C without exceeding the 125 °C max junction temperature.

CASE 2 Conduction via the PC board to air

The low Junction to BGA thermal resistance allows the use of the PC board as a means of removing heat from the VTM. Convection from the PC board to ambient, or conduction to a cold plate, enable flexible thermal management options.

With a VTM mounted on a 2.0 in<sup>2</sup> area of a multi-layer PC board with appropriate power planes resulting in 8 oz of effective copper weight, the Junction-to-BGA thermal resistance, R $\theta_{JA}$ , is 6.5 °C/W in 300 LFM of air. With a maximum junction temperature of 125 °C and 13 W of dissipation at full current of 70 A, the resulting temperature rise of 85 °C allows the VTM to operate at full rated current up to a 40 °C ambient temperature. See thermal resistances on Page 9 for additional details on this thermal management option.

Adding low-profile heat sinks to the PC board can lower the thermal resistance of the PC board surrounding the VTM. Additional cooling may be added by coupling a cold plate to the PC board with low thermal resistance stand offs.

CASE 3 Combined direct convection to the air and conduction to the PC board.

A combination of cooling techniques that utilize the power planes and dissipation to the air will also reduce the total thermal impedance. This is the most effective cooling method. To estimate the total effect of the combination, treat each cooling branch as one leg of a parallel resistor network.

<u>VICOR</u>

Figure 17—Thermal resistance

*Figure 18*—Junction-to-ambient thermal resistance of VTM with 0.25" Pin Fins. (Pin Fins are available as a separate item.)

# V•I Chip VTM Level 1 DC Behavioral Model for 48 V to 3 V, 70 A

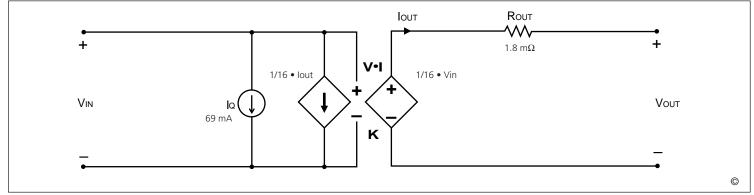

Figure 19—This model characterizes the DC operation of the V•I Chip VTM, including the converter transfer function and its losses. The model enables estimates or simulations of output voltage as a function of input voltage and output load, as well as total converter power dissipation or heat generation.

# V•I Chip VTM Level 2 Transient Behavioral Model for 48 V to 3 V, 70 A

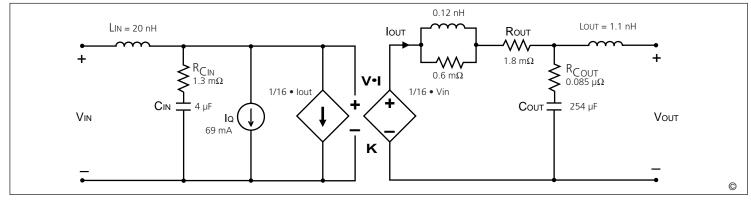

Figure 20—This model characterizes the AC operation of the V•I Chip VTM including response to output load or input voltage transients or steady state modulations. The model enables estimates or simulations of input and output voltages under transient conditions, including response to a stepped load with or without external filtering elements.

## Application Note (continued)

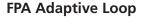

#### In Figures 21 – 23;

- K = VTM Transformation Ratio

- Ro = VTM Output Resistance

- Vf = PRM Output (Factorized Bus Voltage) Vo = VTM Output

- VL = Desired Load Voltage

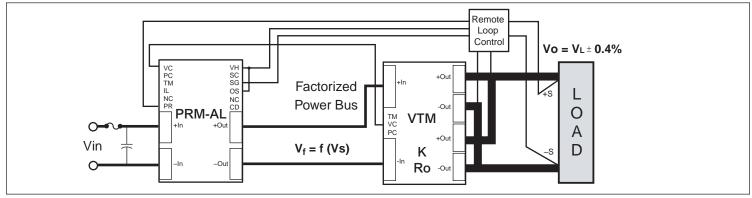

Figure 21 — The PRM controls the factorized bus voltage, V<sub>f</sub>, in proportion to output current to compensate for the output resistance, Ro, of the VTM. The VTM output voltage is typically within 1% of the desired load voltage (V<sub>L</sub>) over all line and load conditions.

#### FPA Non-isolated Remote Loop

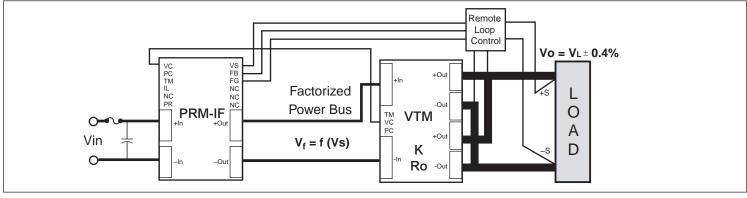

Figure 22 — An external error amplifier or Point-of-Load IC (POLIC) senses the load voltage and controls the PRM output – the Factorized Bus – as a function of output current, compensating for the output resistance of the VTM and for distribution resistance.

#### **FPA Isolated Remote Loop**

**Figure 23**—An external error amplifier or Point-of-Load IC (POLIC) senses the load voltage and controls the PRM output – the factorized bus – as a function of output current, compensating for the output resistance of the VTM and for distribution resistance. The Factorized Bus voltage (Vt) increases in proportion to load current. The remote feedback loop is isolated within the PRM to support galvanic isolation and hipot compliance at the system level.

## Application Note (continued)

#### **V**•I Chip soldering recommendations

V•I Chip modules are intended for reflow soldering processes. The following information defines the processing conditions required for successful attachment of a V•I Chip to a PCB. Failure to follow the recommendations provided can result in aesthetic or functional failure of the module.

#### Storage

V•I Chip modules are currently rated at MSL 5. Exposure to ambient conditions for more than 72 hours requires a 24 hour bake at 125°C to remove moisture from the package.

#### Solder paste stencil design

Solder paste is recommended for a number of reasons, including overcoming minor solder sphere co-planarity issues as well as simpler integration into overall SMD process.

63/37 SnPb, either no-clean or water-washable, solder paste should be used. Pb-free development is underway.

The recommended stencil thickness is 6 mils. The apertures should be 20 mils in diameter for the Inboard (BGA) application and 0.9-0.9:1 for the Onboard (J-Leaded).

#### Pick and place

Inboard (BGA) modules should be placed as accurately as possible to minimize any skewing of the solder joint; a maximum offset of 10 mils is allowable. Onboard (J-Leaded) modules should be placed within  $\pm 5$  mils.

To maintain placement position, the modules should not be subjected to acceleration greater than 500 in/sec<sup>2</sup> prior to reflow.

#### Reflow

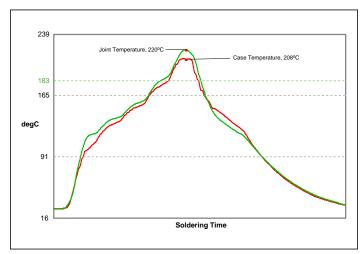

There are two temperatures critical to the reflow process; the solder joint temperature and the module's case temperature. The solder joint's temperature should reach at least 220°C, with a time above liquidus (183°C) of ~30 seconds.

The module's case temperature must not exceed 208  $^{\circ}\mathrm{C}$  at anytime during reflow.

Because of the  $\Delta T$  needed between the pin and the case, a forced-air convection oven is preferred for reflow soldering. This reflow method generally transfers heat from the PCB to the solder joint. The module's large mass also reduces its temperature rise. Care should be taken to prevent smaller devices from excessive temperatures. Reflow of modules onto a PCB using Air-Vac-type equipment is not recommended due to the high temperature the module will experience.

#### Inspection

For the BGA-version, a visual examination of the post-reflow solder joints should show relatively columnar solder joints with no bridges. An inspection using x-ray equipment can be done, but the module's materials may make imaging difficult.

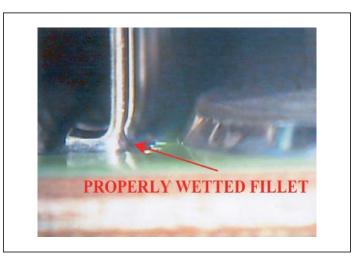

The J-Lead versions solder joints should conform to IPC 12.2

- Properly wetted fillet must be evident.

- Heel fillet height must exceed lead thickness plus solder thickness.

#### **Removal and rework**

V•I Chip modules can be removed from PCBs using special tools such as those made by Air-Vac. These tools heat a very localized region of the board with a hot gas while applying a tensile force to the component (using vacuum). Prior to component heating and removal, the entire board should be heated to 80-100°C to decrease the component heating time as well as local PCB warping. If there are adjacent moisture-sensitive components, a 125°C bake should be used prior to component removal to prevent popcorning. V•I Chip modules should not be expected to survive a removal operation.

Figure 24—Thermal profile diagram

Figure 25— Properly reflowed V•I Chip J-Lead

M VICOR

vicorpower.com 800-735-6200 V•I Chip Voltage Transformation Module V048K030T070 Rev. 1.0

## Application Note (continued)

#### Input Impedance Recommendations

To take full advantage of the VTM's capabilities, the impedance of the source (input source plus the PC board impedance) must be low over a range from DC to 5 MHz. The input of the VTM (factorized bus) should be locally bypassed with a 8  $\mu$ F low Q aluminum electrolytic capacitor. Additional input capacitance may be added to improve transient performance or compensate for high source impedance. The VTM has extremely wide bandwidth so the source response to transients is usually the limiting factor in overall output response of the VTM.

Anomalies in the response of the source will appear at the output of the VTM, multiplied by its K factor of 1/16. The DC resistance of the source should be kept as low as possible to minimize voltage deviations on the input to the VTM. If the VTM is going to be operating close to the high limit of its input range, make sure input voltage deviations will not trigger the input overvoltage turn-off threshold.

#### **Input Fuse Recommendations**

V•I Chips are not internally fused in order to provide flexibility in configuring power systems. However, input line fusing of V•I Chips must always be incorporated within the power system. A fast acting fuse is required to meet safety agency Conditions of Acceptability. The input line fuse should be placed in series with the +In port.

## Warranty

Vicor products are guaranteed for two years from date of shipment against defects in material or workmanship when in normal use and service. This warranty does not extend to products subjected to misuse, accident, or improper application or maintenance. Vicor shall not be liable for collateral or consequential damage. This warranty is extended to the original purchaser only.

EXCEPT FOR THE FOREGOING EXPRESS WARRANTY, VICOR MAKES NO WARRANTY, EXPRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO, THE WARRANTY OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE.

Vicor will repair or replace defective products in accordance with its own best judgement. For service under this warranty, the buyer must contact Vicor to obtain a Return Material Authorization (RMA) number and shipping instructions. Products returned without prior authorization will be returned to the buyer. The buyer will pay all charges incurred in returning the product to the factory. Vicor will pay all reshipment charges if the product was defective within the terms of this warranty.

Information published by Vicor has been carefully checked and is believed to be accurate; however, no responsibility is assumed for inaccuracies. Vicor reserves the right to make changes to any products without further notice to improve reliability, function, or design. Vicor does not assume any liability arising out of the application or use of any product or circuit; neither does it convey any license under its patent rights nor the rights of others. Vicor general policy does not recommend the use of its components in life support applications wherein a failure or malfunction may directly threaten life or injury. Per Vicor Terms and Conditions of Sale, the user of Vicor components in life support applications assumes all risks of such use and indemnifies Vicor against all damages.

# Vicor's comprehensive line of power solutions includes high density AC-DC and DC-DC modules and accessory components, fully configurable AC-DC and DC-DC power supplies, and complete custom power systems.

Information furnished by Vicor is believed to be accurate and reliable. However, no responsibility is assumed by Vicor for its use. Vicor components are not designed to be used in applications, such as life support systems, wherein a failure or malfunction could result in injury or death. All sales are subject to Vicor's Terms and Conditions of Sale, which are available upon request.

#### Specifications are subject to change without notice.

#### **Intellectual Property Notice**

Vicor and its subsidiaries own Intellectual Property (including issued U.S. and Foreign Patents and pending patent applications) relating to the products described in this data sheet. Interested parties should contact Vicor's Intellectual Property Department.

Vicor Corporation 25 Frontage Road

Andover, MA, USA 01810 Tel: 800-735-6200 Fax: 978-475-6715

email

Vicor Express: vicorexp@vicr.com Technical Support: apps@vicr.com

vicorpower.com 800-735-6200 Vel Chip Voltage Transformation Module V048K030T070 Rev. 1.0