## **1.0 General Description**

The AMIS-42675 CAN transceiver is the interface between a controller area network (CAN) protocol controller and the physical bus. It may be used in both 12V and 24V systems. The transceiver provides differential transmit capability to the bus and differential receive capability to the CAN controller.

The AMIS-42675 is the low power member of the CAN high-speed transceiver family and offers the following additional features:

- Ideal passive behaviour when supply voltage is removed

- Wake-up over bus

- Extremely low current standby mode

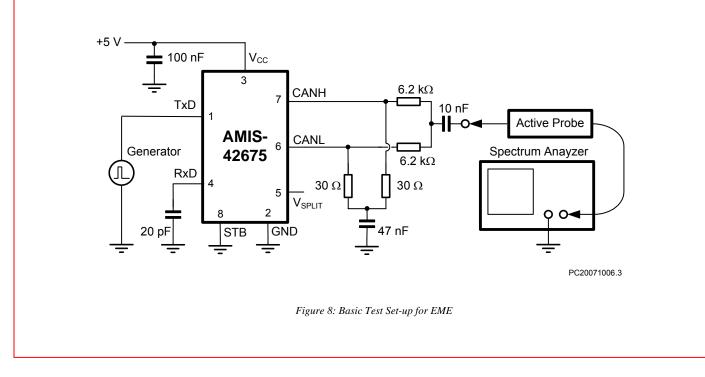

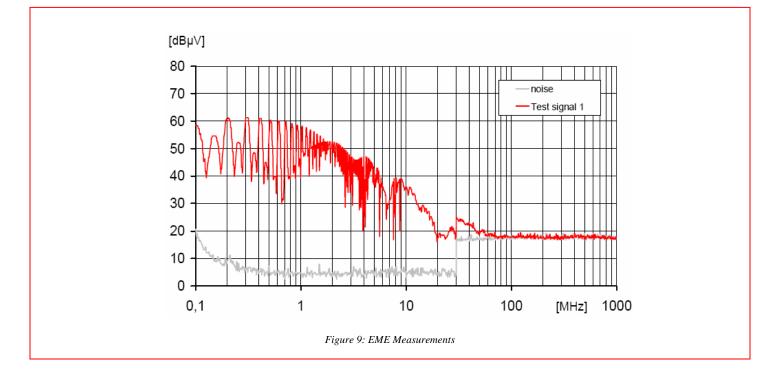

Due to the wide common-mode voltage range of the receiver inputs, the AMIS-42675 is able to reach outstanding levels of electromagnetic susceptibility (EMS). Similarly, extremely low electromagnetic emission (EME) is achieved by the excellent matching of the output signals.

The AMIS-42675 is the industrial version of the AMIS-42665 and primarily for applications where long network lengths are mandatory. Examples are elevators, in-building networks, process control and trains. To cope with the long bus delay the communication speed needs to be low. AMIS-42675 allows low transmit data rates down 10 Kbit/s or lower.

# 2.0 Key Features

- Compatible with the ISO 11898 standard (ISO 11898-2, ISO 11898-5 and SAE J2284)

- Wide range of bus communication speed (0 up to 1 Mbit/s)

- · Ideally suited for 12V and 24V industrial and automotive applications

- Allows low transmit data rate in networks exceeding 1 km

- · Extremely low current standby mode with wake-up via the bus

- Low electromagnetic emission (EME): common-mode choke is no longer required

- Differential receiver with wide common-mode range (+/- 35V) for high EMS

- Voltage source via V<sub>SPLIT</sub> pin for stabilizing the recessive bus level (further EMC improvement)

- No disturbance of the bus lines with an un-powered node

- Thermal protection

- · Bus pins protected against transients

- · Power down mode in which the transmitter is disabled

- Bus and V<sub>SPLIT</sub> pins short circuit proof to supply voltage and ground

- Logic level inputs compatible with 3.3V devices

- At least 110 nodes can be connected to the same bus

# **3.0 Ordering Information**

| Table 1: Ordering Information |                      |                |              |             |

|-------------------------------|----------------------|----------------|--------------|-------------|

| Ordering Code (Tubes)         | Ordering Code (Tape) | Marketing Name | Package      | Temp. Range |

| 0ICAA-001-XTD                 | 0ICAA-001-XTP        | AMIS 42675AGA  | SOIC-8 GREEN | -40°C125°C  |

# 4.0 Technical Characteristics

| Symbol                       | Parameter                                         | Conditions                                                     | Min. | Max.            | Unit |

|------------------------------|---------------------------------------------------|----------------------------------------------------------------|------|-----------------|------|

| V <sub>CC</sub>              | Power supply voltage                              |                                                                | 4.75 | 5.25            | V    |

| V <sub>STB</sub>             | DC voltage at pin STB                             |                                                                | -0.3 | V <sub>cc</sub> | V    |

| V <sub>TxD</sub>             | DC voltage at pin TxD                             |                                                                | -0.3 | Vcc             | V    |

| V <sub>RxD</sub>             | DC voltage at pin RxD                             |                                                                | -0.3 | V <sub>cc</sub> | V    |

| V <sub>CANH</sub>            | DC voltage at pin CANH                            | $0 < V_{cc} < 5.25V$ ; no time limit                           | -35  | +35             | V    |

| V <sub>CANL</sub>            | DC voltage at pin CANL                            | $0 < V_{cc} < 5.25V$ ; no time limit                           | -35  | +35             | V    |

| V <sub>SPLIT</sub>           | DC voltage at pin V <sub>SPLIT</sub>              | $0 < V_{CC} < 5.25V$ ; no time limit                           | -35  | +35             | V    |

| V <sub>O(dif)(bus_dom)</sub> | Differential bus output voltage in dominant state | 42.5Ω < R <sub>LT</sub> < 60Ω                                  | 1.5  | 3               | V    |

| CM-range                     | Input common-mode range for comparator            | Guaranteed differential receiver threshold and leakage current | -35  | +35             | V    |

| V <sub>CM-peak</sub>         | Common-mode peak                                  | Note                                                           | -500 | 500             | mV   |

| Cload                        | Load capacitance on IC outputs                    |                                                                |      | 15              | pF   |

| t <sub>pd(rec-dom)</sub>     | Propagation delay TxD to RxD                      | See Figure 5                                                   | 70   | 230             | ns   |

| t <sub>pd(dom-rec)</sub>     | Propagation delay TxD to RxD                      | See Figure 5                                                   | 100  | 245             | ns   |

| V <sub>CM-step</sub>         | Common-mode step                                  | Note                                                           | -150 | 150             | mV   |

| T <sub>junc</sub>            | Junction temperature                              |                                                                | -40  | 150             | °C   |

Note: The parameters  $V_{CM-peak}$  and  $V_{CM-step}$  guarantee low EME.

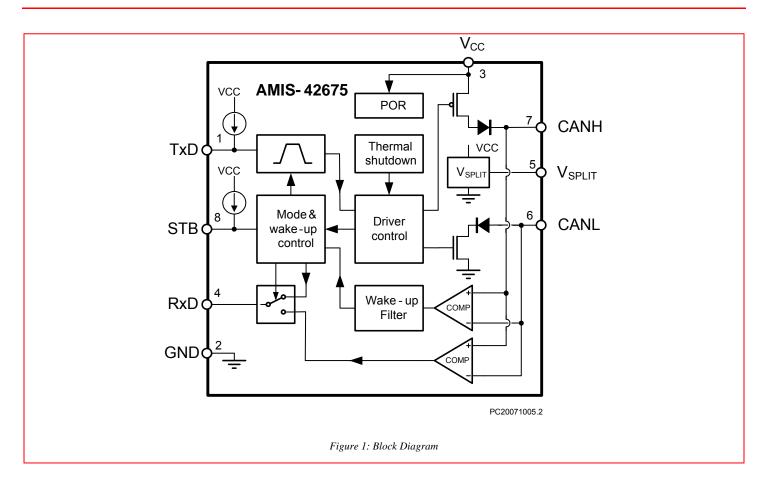

## 5.0 Block Diagram

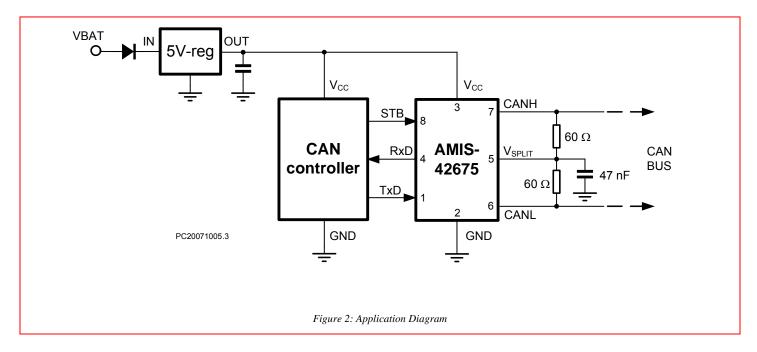

## **6.0 Typical Application**

## **6.1 Application Schematic**

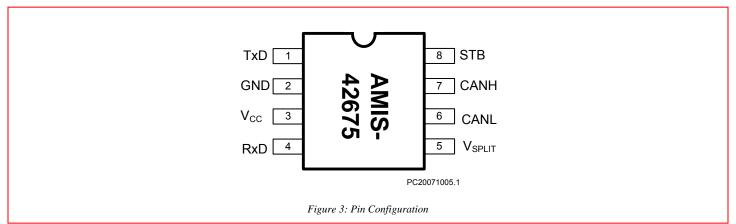

## 6.2 Pin Description

| Table 3 | 3: Pin Out         |                                                                             |

|---------|--------------------|-----------------------------------------------------------------------------|

| Pin     | Name               | Description                                                                 |

| 1       | TxD                | Transmit data input; low input => dominant driver; internal pull-up current |

| 2       | GND                | Ground                                                                      |

| 3       | V <sub>cc</sub>    | Supply voltage                                                              |

| 4       | RxD                | Receive data output; dominant transmitter => low output                     |

| 5       | V <sub>SPLIT</sub> | Common-mode stabilization output                                            |

| 6       | CANL               | Low-level CAN bus line (low in dominant mode)                               |

| 7       | CANH               | High-level CAN bus line (high in dominant mode)                             |

| 8       | STB                | Stand-by mode control input                                                 |

## 7.0 Functional Description

## 7.1 Operating Modes

AMIS-42675 provides two modes of operation as illustrated in Table 4. These modes are selectable through pin STB.

Table 4: Operating Modes

| Mode    | Pin STB | Pin RXD                  |                             |  |  |

|---------|---------|--------------------------|-----------------------------|--|--|

| Mode    | FIIISID | Low High                 |                             |  |  |

| Normal  | Low     | Bus dominant             | Bus recessive               |  |  |

| Standby | High    | Wake-up request detected | No wake-up request detected |  |  |

#### 7.1.1. Normal Mode

In the normal mode, the transceiver is able to communicate via the bus lines. The signals are transmitted and received to the CAN controller via the pins TxD and RxD. The slopes on the bus lines outputs are optimized to give extremely low EME.

#### 7.1.2. Stand-by Mode

In stand-by mode both the transmitter and receiver are disabled and a very low-power differential receiver monitors the bus lines for CAN bus activity. The bus lines are terminated to ground and supply current is reduced to a minimum, typically  $10\mu$ A. When a wake-up request is detected by the low-power differential receiver, the signal is first filtered and then verified as a valid wake signal after a time period of t<sub>BUS</sub>, the RxD pin is driven low by the transceiver to inform the controller of the wake-up request.

#### 7.2 Split Circuit

The  $V_{SPLIT}$  pin is operational only in normal mode. In standby mode this pin is floating. The  $V_{SPLIT}$  is connected as shown in Figure 2 and its purpose is to provide a stabilized DC voltage of 0.5 x  $V_{CC}$  to the bus avoiding possible steps in the common-mode signal therefore reducing EME. These unwanted steps could be caused by an un-powered node on the network with excessive leakage current from the bus that shifts the recessive voltage from its nominal 0.5 x  $V_{CC}$  voltage.

#### 7.3 Wake-up

Once a valid wake-up (dominant state longer than t<sub>BUS</sub>) has been received during the standby mode the RxD pin is driven low.

#### 7.4 Over-temperature Detection

A thermal protection circuit protects the IC from damage by switching off the transmitter if the junction temperature exceeds a value of approximately 160°C. Because the transmitter dissipates most of the power, the power dissipation and temperature of the IC is reduced. All other IC functions continue to operate. The transmitter off-state resets when pin TxD goes high. The thermal protection circuit is particularly needed when a bus line short circuits.

#### 7.5 High Communication Speed Range

The transceiver is primarily intended for industrial applications. It allows very low baud rates needed for long bus length applications. But also high speed communication is possible up to 1Mbit/s.

#### 7.6 Fail Safe Features

A current-limiting circuit protects the transmitter output stage from damage caused by accidental short circuit to either positive or negative supply voltage, although power dissipation increases during this fault condition.

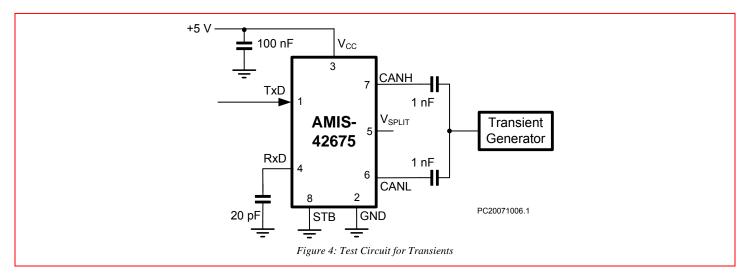

The pins CANH and CANL are protected from automotive electrical transients (according to ISO 7637; see Figure 4). Pins TxD and STB are pulled high internally should the input become disconnected. Pins TxD, STB and RxD will be floating, preventing reverse supply should the  $V_{CC}$  supply be removed.

## **8.0 Electrical Characteristics**

### **8.1 Definitions**

All voltages are referenced to GND (pin 2). Positive currents flow into the IC. Sinking current means the current is flowing into the pin; sourcing current means the current is flowing out of the pin.

#### 8.2 Absolute Maximum Ratings

Stresses above those listed in the following table may cause permanent device failure. Exposure to absolute maximum ratings for extended periods may affect device reliability.

| Symbol                    | Parameter                                   | Conditions                           | Min. | Max.                  | Unit |

|---------------------------|---------------------------------------------|--------------------------------------|------|-----------------------|------|

| V <sub>cc</sub>           | Supply voltage                              |                                      | -0.3 | +7                    | V    |

| V <sub>CANH</sub>         | DC voltage at pin CANH                      | $0 < V_{CC} < 5.25V$ ; no time limit | -50  | +50                   | V    |

| V <sub>CANL</sub>         | DC voltage at pin CANL                      | $0 < V_{CC} < 5.25V$ ; no time limit | -50  | +50                   | V    |

| V <sub>SPLIT</sub>        | DC voltage at pin VSPLIT                    | $0 < V_{CC} < 5.25V$ ; no time limit | -50  | +50                   | V    |

| V <sub>TxD</sub>          | DC voltage at pin TxD                       |                                      | -0.3 | V <sub>cc</sub> + 0.3 | V    |

| V <sub>RxD</sub>          | DC voltage at pin RxD                       |                                      | -0.3 | V <sub>cc</sub> + 0.3 | V    |

| V <sub>STB</sub>          | DC voltage at pin STB                       |                                      | -0.3 | V <sub>cc</sub> + 0.3 | V    |

| V <sub>tran(CANH)</sub>   | Transient voltage at pin CANH               | Note 1                               | -300 | +300                  | V    |

| V <sub>tran(CANL)</sub>   | Transient voltage at pin CANL               | Note 1                               | -300 | +300                  | V    |

| V <sub>tran(VSPLIT)</sub> | Transient voltage at pin VSPLIT             | Note 1                               | -300 | +300                  | V    |

| V <sub>esd(</sub>         | Electrostatic discharge voltage at all pins | Note 2                               | -5   | +5                    | kV   |

| 000(                      |                                             | Note 4                               | -750 | +750                  | V    |

| Latch-up                  | Static latch-up at all pins                 | Note 3                               |      | 120                   | mA   |

| T <sub>stg</sub>          | Storage temperature                         |                                      | -55  | +150                  | °C   |

| T <sub>amb</sub>          | Ambient temperature                         |                                      | -40  | +125                  | °C   |

| Tjunc                     | Maximum junction temperature                |                                      | -40  | +170                  | °C   |

Notes:

1) Applied transient waveforms in accordance with ISO 7637 part 3, test pulses 1, 2, 3a, and 3b (see Figure 4).

2) Standardized human body model electrostatic discharge (ESD) pulses in accordance to MIL883 method 3015.7.

3) Static latch-up immunity: Static latch-up protection level when tested according to EIA/JESD78.

4) Standardized charged device model ESD pulses when tested according to EOS/ESD DS5.3-1993.

### **8.3 Thermal Characteristics**

| Symbol                | nal Characteristics                                        | Conditions  | Value | Unit |

|-----------------------|------------------------------------------------------------|-------------|-------|------|

| R <sub>th(vj-a)</sub> | Thermal resistance from junction to ambient in SO8 package | In free air | 145   | K/W  |

| R <sub>th(vj-s)</sub> | Thermal resistance from junction to substrate of bare die  | In free air | 45    | K/W  |

## **8.4 Characteristics**

$V_{CC}$  = 4.75 to 5.25V;  $T_{junc}$  = -40 to +150°C;  $R_{LT}$  =60 $\Omega$  unless specified otherwise.

#### Table 7: Characteristics

| Symbol                        | Parameter                                                                   | Conditions                                                                  | Min.                  | Тур.    | Max.                   | Unit     |

|-------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------|---------|------------------------|----------|

| Supply (pin V <sub>cc</sub> ) |                                                                             |                                                                             |                       |         |                        |          |

| Icc                           | Supply current                                                              | Dominant; $V_{TxD} = 0V$<br>Recessive; $V_{TxD} = V_{CC}$                   |                       | 45<br>4 | 65<br>8                | mA<br>mA |

| I <sub>CCS</sub>              | Supply current in standby mode                                              | T <sub>junc,max</sub> = 100°C                                               |                       | 10      | 15                     | μA       |

|                               | a Input (pin TxD)                                                           |                                                                             |                       |         |                        |          |

| VIH                           | High-level input voltage                                                    | Output recessive                                                            | 2.0                   | -       | V <sub>CC</sub> + 0.3  | V        |

| V <sub>IL</sub>               | Low-level input voltage                                                     | Output dominant                                                             | -0.3                  | -       | +0.8                   | V        |

| Ін                            | High-level input current                                                    | V <sub>TxD</sub> =V <sub>CC</sub>                                           | -5                    | 0       | +5                     | μA       |

| liL                           | Low-level input current                                                     | $V_{TxD} = 0V$                                                              | -75                   | -200    | -350                   | μA       |

| Ci                            | Input capacitance                                                           | Not tested                                                                  | -                     | 5       | 10                     | pF       |

|                               | de Select (pin STB)                                                         |                                                                             | · · · ·               |         | •                      |          |

| Viн                           | High-level input voltage                                                    | Standby mode                                                                | 2.0                   | -       | V <sub>CC</sub> + 0.3  | V        |

| V <sub>IL</sub>               | Low-level input voltage                                                     | Normal mode                                                                 | -0.3                  | -       | +0.8                   | V        |

| ін                            | High-level input current                                                    | V <sub>STB</sub> =V <sub>CC</sub>                                           | -5                    | 0       | +5                     | μA       |

| IIL                           | Low-level input current                                                     | V <sub>STB</sub> = 0V                                                       | -1                    | -4      | -10                    | μA       |

| C <sub>i</sub>                | Input capacitance                                                           | Not tested                                                                  | -                     | 5       | 10                     | pF       |

|                               | Dutput (pin RxD)                                                            | I                                                                           |                       | -       | -                      | P        |

| V <sub>OH</sub>               | High-level output voltage                                                   | I <sub>RXD</sub> = -10mA                                                    | 0.6 x V <sub>cc</sub> |         | 0.75 x V <sub>cc</sub> | V        |

| Vol                           | Low-level output voltage                                                    | I <sub>RXD</sub> = 5mA                                                      |                       | 0.25    | 0.45                   | V        |

| oh                            | High-level output current                                                   | $V_0 = 0.7 \times V_{CC}$                                                   | -5                    | -10     | -15                    | mA       |

| I <sub>ol</sub>               | Low-level output current                                                    | $V_0 = 0.3 \times V_{CC}$                                                   | 5                     | 10      | 15                     | mA       |

|                               | CANH and CANL)                                                              |                                                                             |                       |         |                        |          |

| Vo(reces) (norm)              | Recessive bus voltage                                                       | V <sub>TxD</sub> = V <sub>CC</sub> ; no load<br>normal mode                 | 2.0                   | 2.5     | 3.0                    | V        |

| Vo(reces) (stby)              | Recessive bus voltage                                                       | $V_{TxD} = V_{CC}$ ; no load standby mode                                   | -100                  | 0       | 100                    | mV       |

| o(reces) (CANH)               | Recessive output current at pin CANH                                        | -35V <v<sub>CANH&lt; +35V;<br/>0V <v<sub>CC &lt; 5.25V</v<sub></v<sub>      | -2.5                  | -       | +2.5                   | mA       |

| o(reces) (CANL)               | Recessive output current at pin CANL                                        | -35V <v<sub>CANL &lt; +35V;<br/>0V <v<sub>CC &lt; 5.25V</v<sub></v<sub>     | -2.5                  | -       | +2.5                   | mA       |

| Vo(dom) (CANH)                | Dominant output voltage at pin CANH                                         | $V_{TxD} = 0V$                                                              | 3.0                   | 3.6     | 4.25                   | V        |

| V <sub>o(dom)</sub> (CANL)    | Dominant output voltage at pin CANL                                         | $V_{TxD} = 0V$                                                              | 0.5                   | 1.4     | 1.75                   | V        |

| V <sub>o(dif) (bus_dom)</sub> | Differential bus output voltage<br>(V <sub>CANH</sub> - V <sub>CANL</sub> ) | $V_{TxD}$ = 0V; dominant;<br>42.5 $\Omega$ < R <sub>LT</sub> < 60 $\Omega$  | 1.5                   | 2.25    | 3.0                    | V        |

| Vo(dif) (bus_rec)             | Differential bus output voltage<br>(V <sub>CANH</sub> - V <sub>CANL</sub> ) | $V_{TxD} = V_{CC}$ ; recessive;<br>no load                                  | -120                  | 0       | +50                    | mV       |

| o(sc) (CANH)                  | Short circuit output current at pin CANH                                    | $V_{CANH} = 0V; V_{TxD} = 0V$                                               | -45                   | -70     | -120                   | mA       |

| o(sc) (CANL)                  | Short circuit output current at pin CANL                                    | $V_{CANL} = 36V; V_{TxD} = 0V$                                              | 45                    | 70      | 120                    | mA       |

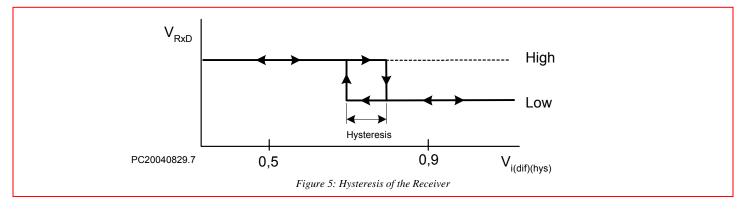

| Vi(dif) (th)                  | Differential receiver threshold voltage (see Figure 5)                      | -5V <v<sub>CANL &lt; +12V;<br/>-5V <v<sub>CANH &lt; +12V;</v<sub></v<sub>   | 0.5                   | 0.7     | 0.9                    | V        |

| Vihcm(dif) (th)               | Differential receiver threshold voltage for high common-mode (see Figure 5) | -35V <v<sub>CANL &lt; +35V;<br/>-35V <v<sub>CANH &lt; +35V;</v<sub></v<sub> | 0.40                  | 0.7     | 1.00                   | V        |

| V <sub>i(dif) (hys)</sub>     | Differential receiver input voltage hysteresis (see Figure 5                | -35V <v<sub>CANL &lt; +35V;<br/>-35V <v<sub>CANH &lt; +35V;</v<sub></v<sub> | 50                    | 70      | 100                    | mV       |

| Ri(cm) (CANH)                 | Common-mode input resistance at pin CANH                                    |                                                                             | 15                    | 26      | 37                     | KΩ       |

| Ri(cm) (CANL)                 | Common-mode input resistance at pin CANL                                    |                                                                             | 15                    | 26      | 37                     | KΩ       |

| Ri(cm) (m)                    | Matching between pin CANH and pin CANL common mode input resistance         | $V_{CANH} = V_{CANL}$                                                       | -3                    | 0       | +3                     | %        |

| Ri(dif)                       | Differential input resistance                                               |                                                                             | 25                    | 50      | 75                     | KΩ       |

| Ci(CANH)                      | Input capacitance at pin CANH                                               | $V_{TxD} = V_{CC}$ ; not tested                                             |                       | 7.5     | 20                     | pF       |

| Ci(CANL)                      | Input capacitance at pin CANL                                               | $V_{TxD} = V_{CC}$ ; not tested                                             |                       | 7.5     | 20                     | pF       |

| Ci(dif)                       | Differential input capacitance                                              | $V_{TxD} = V_{CC}$ ; not tested                                             |                       | 3.75    | 10                     | pF       |

# AMIS-42675 High-Speed Low Power CAN Transceiver For Long Networks

#### Table 8: Characteristics (continued)

| Symbol                            | Parameter                                               | Conditions                                                    | Min.                  | Тур. | Max.                  | Unit |

|-----------------------------------|---------------------------------------------------------|---------------------------------------------------------------|-----------------------|------|-----------------------|------|

| Common-mo                         | de Stabilization (pin V <sub>SPLIT</sub> )              |                                                               |                       |      |                       |      |

| V <sub>SPLIT</sub>                | Reference output voltage at pin V <sub>SPLIT</sub>      | Normal mode;<br>-500µA < I <sub>SPLIT</sub> < 500µA           | 0.3 x V <sub>CC</sub> | -    | 0.7 x V <sub>CC</sub> |      |

| I <sub>SPLIT(i)</sub>             | V <sub>SPLIT</sub> leakage current                      | Stand-by mode                                                 | -5                    |      | +5                    | μA   |

| SPLIT(lim)                        | V <sub>SPLIT</sub> limitation current                   | Normal mode                                                   | -3                    |      | +3                    | mA   |

| Power-on-Res                      | set (POR)                                               |                                                               |                       |      |                       |      |

| PORL                              | POR level                                               | CANH, CANL, V <sub>ref</sub> in tri-<br>state below POR level | 2.2                   | 3.5  | 4.7                   | V    |

| Thermal Shut                      | down                                                    |                                                               |                       |      |                       |      |

| T <sub>j(sd)</sub>                | Shutdown junction temperature                           |                                                               | 150                   | 160  | 180                   | °C   |

| <b>Timing Chara</b>               | cteristics (see Figure 4 and Figure 5)                  |                                                               |                       |      |                       |      |

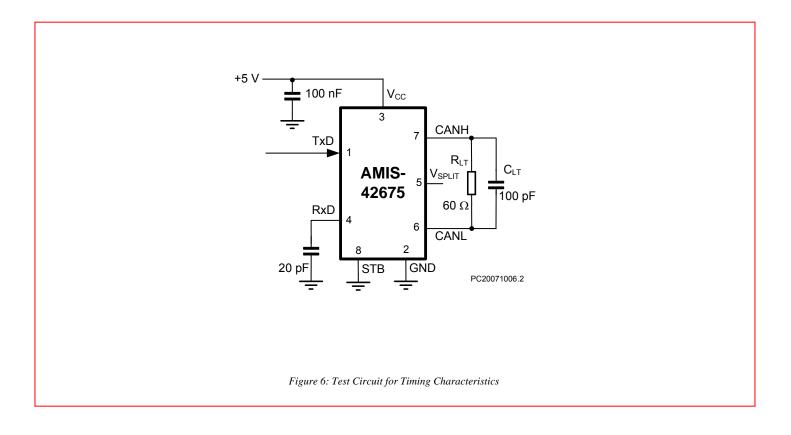

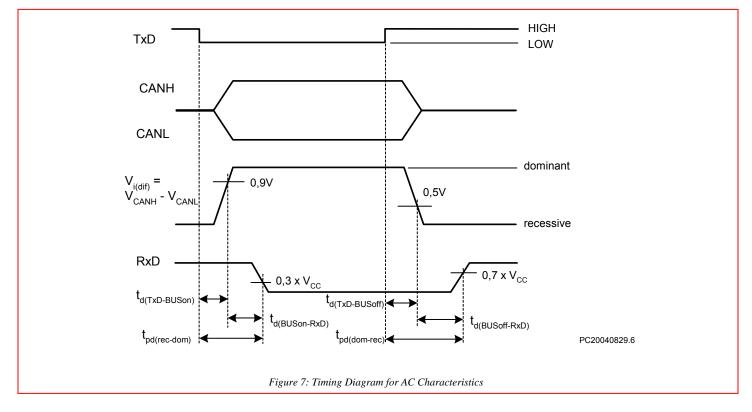

| $t_{\text{d}(\text{TxD-BUSon})}$  | Delay TXD to bus active                                 | C <sub>I</sub> = 100pF between<br>CANH to CANL                | 40                    | 85   | 105                   | ns   |

| $t_{\text{d}(\text{TxD-BUSoff})}$ | Delay TXD to bus inactive                               | C <sub>I</sub> = 100pF between<br>CANH to CANL                | 30                    | 60   | 105                   | ns   |

| t <sub>d(BUSon-RXD)</sub>         | Delay bus active to RXD                                 | C <sub>rxd</sub> = 15pF                                       | 25                    | 55   | 105                   | ns   |

| td(BUSoff-RXD)                    | Delay bus inactive to RXD                               | C <sub>rxd</sub> = 15pF                                       | 40                    | 100  | 105                   | ns   |

| t <sub>pd(rec-dom)</sub>          | Propagation delay TXD to RXD from recessive to dominant | C <sub>I</sub> = 100pF between<br>CANH to CANL                | 90                    |      | 230                   | ns   |

| $t_{\text{d(dom-rec)}}$           | Propagation delay TXD to RXD from dominant to recessive | C <sub>I</sub> = 100pF between<br>CANH to CANL                | 90                    |      | 245                   | ns   |

| t <sub>d(stb-nm)</sub>            | Delay standby mode to normal mode                       |                                                               | 5                     | 7.5  | 10                    | μs   |

| t <sub>dbus</sub>                 | Dominant time for wake-up via bus                       |                                                               | 0.75                  | 2.5  | 5                     | μs   |

### 8.5 Measurement Set-ups and Definitions

Data Sheet

# AMIS-42675 High-Speed Low Power CAN Transceiver For Long Networks

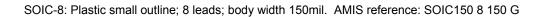

# 9.0 Package Outline

AMI AMI SEMICONDUCTOR

## **10.0 Soldering**

#### **10.1 Introduction to Soldering Surface Mount Packages**

This text gives a very brief insight to a complex technology. A more in-depth account of soldering ICs can be found in the AMIS "Data Handbook IC26; Integrated Circuit Packages" (document order number 9398 652 90011). There is no soldering method that is ideal for all surface mount IC packages. Wave soldering is not always suitable for surface mount ICs, or for printed-circuit boards (PCBs) with high population densities. In these situations re-flow soldering is often used.

#### 10.2 Re-flow Soldering

Re-flow soldering requires solder paste (a suspension of fine solder particles, flux and binding agent) to be applied to the PCB by screen printing, stencilling or pressure-syringe dispensing before package placement. Several methods exist for re-flowing; for example, infrared/convection heating in a conveyor type oven. Throughput times (preheating, soldering and cooling) vary between 100 and 200 seconds depending on heating method. Typical re-flow peak temperatures range from 215 to 250°C. The top-surface temperature of the packages should preferably be kept below 230°C.

#### 10.3 Wave Soldering

Conventional single wave soldering is not recommended for surface mount devices (SMDs) or PCBs with a high component density, as solder bridging and non-wetting can present major problems. To overcome these problems the double-wave soldering method was specifically developed. If wave soldering is used the following conditions must be observed for optimal results:

- Use a double-wave soldering method comprising a turbulent wave with high upward pressure followed by a smooth laminar wave.

- For packages with leads on two sides and a pitch (e):

- Larger than or equal to 1.27mm, the footprint longitudinal axis is preferred to be parallel to the transport direction of the PCB;

- Smaller than 1.27mm, the footprint longitudinal axis must be parallel to the transport direction of the PCB. The footprint must incorporate solder thieves at the downstream end.

- For packages with leads on four sides, the footprint must be placed at a 45° angle to the transport direction of the PCB. The footprint must incorporate solder thieves downstream and at the side corners.

During placement and before soldering, the package must be fixed with a droplet of adhesive. The adhesive can be applied by screen printing, pin transfer or syringe dispensing. The package can be soldered after the adhesive is cured. Typical dwell time is four seconds at 250°C. A mildly-activated flux will eliminate the need for removal of corrosive residues in most applications.

#### 10.4 Manual Soldering

Fix the component by first soldering two diagonally-opposite end leads. Use a low voltage (24V or less) soldering iron applied to the flat part of the lead. Contact time must be limited to 10 seconds at up to 300°C. When using a dedicated tool, all other leads can be soldered in one operation within two to five seconds between 270 and 320°C.

#### Table 9: Soldering Method

| Package                         | Soldering Method                  |                        |  |  |

|---------------------------------|-----------------------------------|------------------------|--|--|

| Fackage                         | Wave                              | Re-flow <sup>(1)</sup> |  |  |

| BGA, SQFP                       | Not suitable                      | Suitable               |  |  |

| HLQFP, HSQFP, HSOP, HTSSOP, SMS | Not suitable <sup>(2)</sup>       | Suitable               |  |  |

| PLCC <sup>(3)</sup> , SO, SOJ   | Suitable                          | Suitable               |  |  |

| LQFP, QFP, TQFP                 | Not recommended <sup>(3)(4)</sup> | Suitable               |  |  |

| SSOP, TSSOP, VSO                | Not recommended <sup>(5)</sup>    | Suitable               |  |  |

Notes:

1. All surface mount (SMD) packages are moisture sensitive. Depending upon the moisture content, the maximum temperature (with respect to time) and body size of the package, there is a risk that internal or external package cracks may occur due to vaporization of the moisture in them (the so called popcorn effect). For details, refer to the Drypack information in the Data Handbook IC26; Integrated Circuit Packages; Section: Packing Methods.

2. These packages are not suitable for wave soldering as a solder joint between the PCB and heatsink (at bottom version) can not be achieved, and as solder may stick to the heatsink (on top version).

3. If wave soldering is considered, then the package must be placed at a 45° angle to the solder wave direction. The package footprint must incorporate solder thieves downstream and at the side corners.

4. Wave soldering is only suitable for LQFP, TQFP and QFP packages with a pitch (e) equal to or larger than 0.8mm; it is definitely not suitable for packages with a pitch (e) equal to or smaller than 0.65mm.

5. Wave soldering is only suitable for SSOP and TSSOP packages with a pitch (e) equal to or larger than 0.65mm; it is definitely not suitable for packages with a pitch (e) equal to or smaller than 0.5mm.

# **11.0 Company or Product Inquiries**

For more information about AMI Semiconductor, our technology and our products, visit our Web site at http://www.amis.com.

## **12.0 Revision History**

| Date         | Revision | Change          |

|--------------|----------|-----------------|

| October 2007 | 1.0      | Initial release |

Devices sold by AMIS are covered by the warranty and patent indemnification provisions appearing in its Terms of Sale only. AMIS makes no warranty, express, statutory, implied or by description, regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. AMIS makes no warranty of merchantability or fitness for any purposes. AMIS reserves the right to discontinue production and change specifications and prices at any time and without notice. AMI Semiconductor's products are intended for use in commercial applications. Applications requiring extended temperature range, unusual environmental requirements, or high reliability applications, such as military, medical life-support or life-sustaining equipment, are specifically not recommended without additional processing by AMIS for such applications. Copyright ©2007 AMI Semiconductor, Inc.

AMI AMI SEMICONDUCTOR