DS3600-1.2 September 1992

# P10C68/P11C68

(Previously PNC10C68 and PNC11C68)

# CMOS/SNOS NVSRAM HIGH PERFORMANCE 8 K x 8 NON-VOLATILE STATIC RAM

(Supersedes DS3159-1.3, DS3160-1.3, DS3234-1.1, DS3235-1.1)

The P10C68 and P11C68 are fast static RAMs (35 and 45 ns) with a non-volatile electically-erasable PROM (EEPROM) cell incorporating in each static memory cell. The SRAM can be read and written an unlimited number of times while independent non-volatile data resides in PROM.

On the P10C68 data may easily be transferred from the SRAM to the EEPROM (STORE) and from the EEPROM back to the SRAM (RECALL) using the NE (bar) pin. The Store and Recall cycles are initiated through software sequences on the P11C68. These devices combine the high performance and ease of use of a fast SRAM with the data integrity of non-volatility.

The P10C68 and P11C68 feature the industry standard pinout for non-volatile RAMs in a 28-pin 0.3-inch plastic and ceramic dual-in-line packages.

#### **FEATURES**

- Non-Volatile Data Integrity

- 10 year Data Retention in EEPROM

- 35ns and 45ns Address and Chip Enable Access Times

- 20ns and 25ns Output Enable Access

- Unlimited Read and Write to SRAM

- Unlimited Recall Cycles from EEPROM

- 10<sup>4</sup> Store Cycles to EEPROM

- Automatic Recall on Power up

- Automatic Store Timing

- Hardware Store Protection

- Single 5V ± 10% Operation

- Available in Standard Package 28-pin 0.3-inch DIL plastic and ceramic

- Commercial and Industrial temperature ranges

#### ORDERING INFORMATION

(See back page)

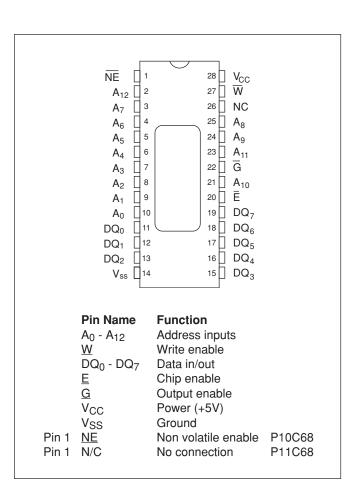

Figure 1. Pin connections - top view.

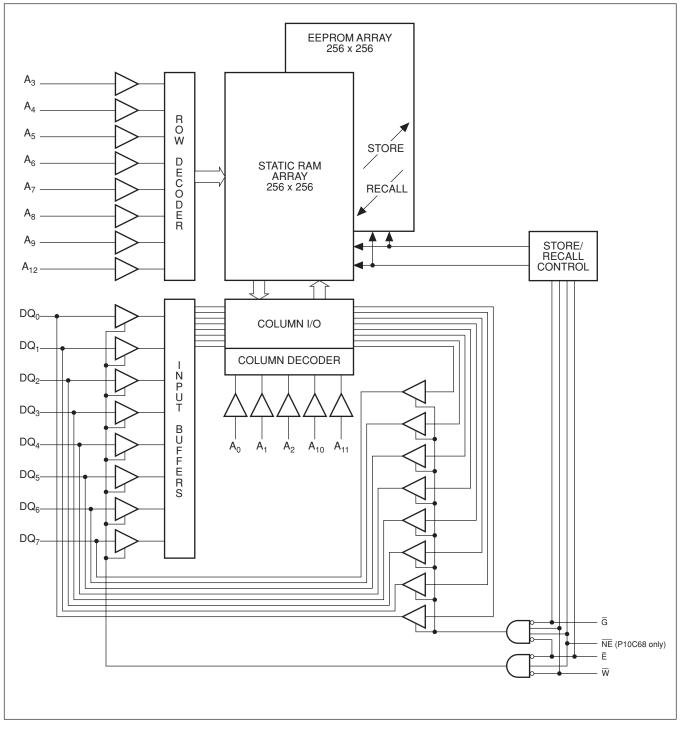

Figure 2. Logic block diagram.

# **ABSOLUTE MAXIMUM RATINGS**

| Voltage on typical input            |                       |

|-------------------------------------|-----------------------|

| relative to VSS                     | -0.6V to 7.0V         |

| Voltage on DQ0-7 and G(bar)         | -0.5V to (Vcc + 0.5V) |

| Temperature under Bias              | -55°C to + 125°C      |

| Storage temperature                 | -65°C to + 150°C      |

| Power dissipation                   | 1W                    |

| DC output current                   | 15mA                  |

| (one output at a time, one second d | uration)              |

NOTE

Stresses greater than those listed in the Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only; functional operation of the device at any other conditions than those indicated in the operational sections of the specification is not implied. Exposure to absolute maximum ratings conditions for extended periods may affect reliability.

# **DC OPERATING CONDITIONS**

| Parameter                                                                                             | Symbol                                                |                             | Value | Units                       | Conditions  |                          |  |

|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-----------------------------|-------|-----------------------------|-------------|--------------------------|--|

|                                                                                                       |                                                       | Min.                        | Тур.  | Max.                        |             |                          |  |

| Supply voltage<br>Input logic '1' voltage<br>Input logic '0' voltage<br>Ambient operating temperature | V <sub>CC</sub><br>V <sub>IH</sub><br>V <sub>IL</sub> | 2.2<br>V <sub>SS</sub> -0.5 | 5.0   | V <sub>CC</sub> +0.5<br>0.8 | V<br>V<br>V | All inputs<br>All inputs |  |

| commercial<br>industrial                                                                              | T <sub>amb</sub><br>T <sub>amb</sub>                  | 0<br>-40                    |       | +70<br>+85                  | °C<br>℃     |                          |  |

# **DC ELECTRICAL CHARACTERISTICS**

# **Commercial temperature range**

Test conditions (unless otherwise stated):

Tamb =  $0^{\circ}$ C to  $70^{\circ}$ C, Vcc = +5V (See notes 1, 2 and 3)

| Characteristic                                                                                                                  | Symbol                                             | Va   | lue             | Units              | Conditions                                                                                                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|------|-----------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                 |                                                    | Min. | Max.            |                    |                                                                                                                                                                                        |

| Average power supply current                                                                                                    | I <sub>CC1</sub>                                   |      | 75<br>65        | mA<br>mA           | $t_{AVAV} = 35ns$<br>$t_{AVAV} = 45ns$                                                                                                                                                 |

| Average power supply current<br>during STORE cycle                                                                              | I <sub>CC2</sub>                                   |      | 50              | mA                 | All inputs at $V_{IN} \le 0.2V$                                                                                                                                                        |

| Average power supply current (standby, cycling TTL input levels)                                                                | I <sub>SB1</sub>                                   |      | 23<br>20        | mA<br>mA           | $\begin{array}{l} t_{AVAV} = 35 ns \\ t_{AVAV} = 45 ns \\ E(bar) \geq V_{IH}, \ all \ other \ inputs \\ cycling \end{array}$                                                           |

| Average power supply current (standby, stable CMOS input levels)                                                                | I <sub>SB2</sub>                                   |      | 1               | mA                 | E (bar) $\geq$ (V <sub>CC</sub> -0.2V), all other inputs at V <sub>IN</sub> $\leq$ 0.2V or $\geq$ (V <sub>CC</sub> - 0.2V)                                                             |

| Input leakage current (any input)<br>Off state output leakage current<br>Output logic '1' voltage<br>Output voltage '0' voltage | I <sub>ILK</sub><br>Iolk<br>Voh<br>V <sub>OL</sub> | 2.4  | ±1<br>±5<br>0.4 | μΑ<br>μΑ<br>V<br>V | $\label{eq:VCC} \begin{array}{l} V_{CC} = max,  V_{IN} = V_{SS} \text{ to } V_{CC} \\ V_{CC} = max,  V_{IN} = V_{SS} \text{ to } V_{CC} \\ I_{OUT} = 4mA \\ I_{OUT} = 8mA \end{array}$ |

# NOTES

I<sub>CC1</sub> is dependent on output loading and cycle rate. The specified values are obtained with outputs unloaded. 1.

Bringing E (bar)  $\geq$  V<sub>IH</sub> will not produce standby currents levels until any non-volatile cycle in progress has timed out. See 2. Mode Selection table.

I<sub>CC2</sub> is the average current required for the duration of the STORE cycle (t<sub>STORE</sub>) after the sequence that initiates the 3. cycle.

# Industrial temperature range

#### Test conditions (unless otherwise stated):

Tamb =  $-40^{\circ}$ C to  $70^{\circ}$ C, Vcc =  $+5V \pm 10\%$  (See notes 4, 5 and 6)

| Characteristic                                                                                                                  | Symbol                                             | Va   | alue            | Units              | Conditions                                                                                                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|------|-----------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                 | - cymzer                                           | Min. | Max.            |                    |                                                                                                                                                                                        |

| Average power supply current                                                                                                    | I <sub>CC1</sub>                                   |      | 80<br>75        | mA<br>mA           | $t_{AVAV} = 35ns$<br>$t_{AVAV} = 45ns$                                                                                                                                                 |

| Average power supply current<br>during STORE cycle                                                                              | I <sub>CC2</sub>                                   |      | 50              | mA                 | All inputs at $V_{IN} \le 0.2V$                                                                                                                                                        |

| Average power supply current (standby, cycling TTL input levels)                                                                | I <sub>SB1</sub>                                   |      | 27<br>23        | mA<br>mA           | $\begin{array}{l} t_{AVAV} = 35 ns \\ t_{AVAV} = 45 ns \\ E(bar) \geq V_{IH}, \mbox{ all other inputs} \\ cycling \end{array}$                                                         |

| Average power supply current (standby, stable CMOS input levels)                                                                | I <sub>SB2</sub>                                   |      | 1               | mA                 | E (bar) $\geq$ (V <sub>CC</sub> -0.2V), all other inputs at V <sub>IN</sub> $\leq$ 0.2V or $\geq$ (V <sub>CC</sub> - 0.2V)                                                             |

| Input leakage current (any input)<br>Off state output leakage current<br>Output logic '1' voltage<br>Output voltage '0' voltage | I <sub>ILK</sub><br>I <sub>OLK</sub><br>Voh<br>Vol | 2.4  | ±1<br>±5<br>0.4 | μΑ<br>μΑ<br>V<br>V | $\label{eq:VCC} \begin{array}{l} V_{CC} = max,  V_{IN} = V_{SS} \text{ to } V_{CC} \\ V_{CC} = max,  V_{IN} = V_{SS} \text{ to } V_{CC} \\ I_{OUT} = 4mA \\ I_{OUT} = 8mA \end{array}$ |

#### NOTES

- 4. I<sub>CC1</sub> is dependent on output loading and cycle rate. The specified values are obtained with outputs unloaded.

- Bringing E (bar) ≥ V<sub>IH</sub> will not produce standby currents levels until any non-volatile cycle in progress has timed out. See Mode Selection table.

- I<sub>CC2</sub> is the average current required for the duration of the STORE cycle (t<sub>STORE</sub>) after the sequence that initiates the cycle.

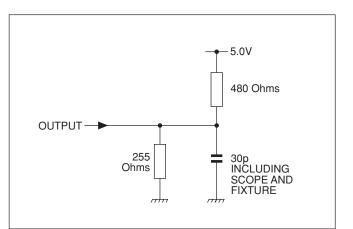

# **AC TEST CONDITIONS**

| Input pulse levels<br>Input rise and fall times<br>Input and output timing reference levels<br>Output load | V <sub>SS</sub> to 3V<br>≤5ns<br>1.5V<br>See Figure 3 |  |

|------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--|

| Output load                                                                                                | See Figure 3                                          |  |

**CAPACITANCE**  $T_{amb} = 25^{\circ}C$ , f = 1.0MHz (see note 7)

| Parameter          | Symbol           | Max. | Units | Conditions         |

|--------------------|------------------|------|-------|--------------------|

| Input capacitance  | C <sub>IN</sub>  | 5    | pF    | $\Delta V=0$ to 3V |

| Output capacitance | C <sub>OUT</sub> | 7    | pF    | $\Delta V=0$ to 3V |

# NOTE

7. These parameters are characterised but not 100% tested.

Figure 3. AC output loading.

# SRAM MEMORY OPERATION Test conditions (unless otherwise stated): Commercial and Industrial Temperature Range Tamb = -40°C to + 85°C, Vcc = + 5V ± 10%

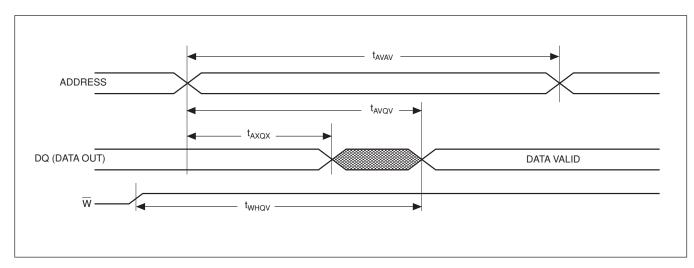

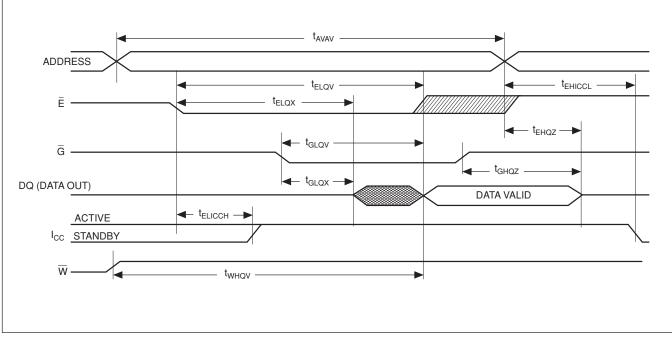

# READ CYCLES 1 AND 2 (See note 8)

| Syn                 | nbol            | Parameter                         |      | P10C68-35<br>P11C68-35 |      | P10C68-45<br>P11C68-45 |    | Notes |

|---------------------|-----------------|-----------------------------------|------|------------------------|------|------------------------|----|-------|

| Standard Alternativ |                 |                                   | Min. | Max.                   | Min. | Max.                   |    |       |

| t <sub>ELQV</sub>   | tACS            | Chip enable access time           |      | 35                     |      | 45                     | ns |       |

| tAVAV               | t <sub>RC</sub> | Read cycle time                   | 35   |                        | 45   |                        | ns | 9     |

| tAVQV               | t <sub>AA</sub> | Address access time               |      | 35                     |      | 45                     | ns | 10    |

| tGLQV               | toe             | Output enable to data valid       |      | 20                     |      | 25                     | ns |       |

| tAXQX               | tон             | Output hold after address change  | 5    |                        | 5    |                        | ns |       |

| t <sub>ELQX</sub>   | tLZ             | Chip enable to output active      | 5    |                        | 5    |                        | ns |       |

| tEHQZ               | tohz            | Chip disable to output inactive   |      | 20                     |      | 25                     | ns | 11    |

| tGLQX               | toLZ            | Output enable to output active    | 0    |                        | 0    |                        | ns |       |

| tGHQZ               | t <sub>HZ</sub> | Outout disable to output inactive |      | 15                     |      | 20                     | ns | 11    |

| telicch             | tPA             | Chip enable to power active       | 0    |                        | 0    |                        | ns | 12    |

| <sup>t</sup> EHICCL | tPS             | Chip disable to power standby     |      | 25                     |      | 25                     | ns | 12    |

| twhqv               | twR             | Write recovery time               |      | 45                     |      | 55                     | ns |       |

### NOTES

8. E (bar), G (bar) and W (bar) must make the transition between VIH(min) to VIL(max), or VIL(max) to VIH(min) in a monotonic fashion. NE (bar) must be ≥ VIH during entire cycle.

- 9. For READ CYCLE 1 and 2, W (bar) and NE (bar) must be high for entire cycle.

- 10. Device is continuously selected with E (bar) low, and G (bar) low.

- 11. Measured ±200mV from steady state output voltage. Load capacitance is 5pF.

- 12. Parameter guaranteed but not tested.

Figure 4. READ CYCLE 1 timing diagram (see notes 9 and 10).

Figure 5. READ CYCLE 2 timing diagram (see note 9).

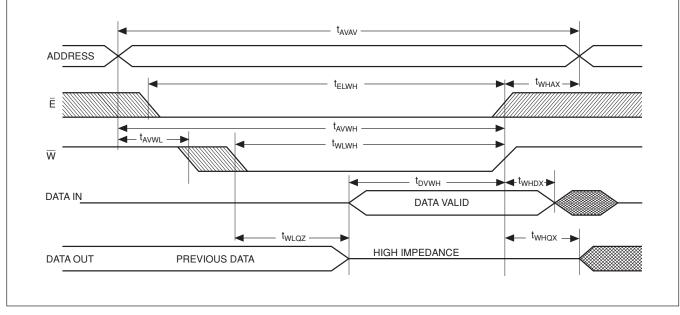

# WRITE CYCLE 1 : W (BAR) CONTROLLED (See notes 8 and 13) Commercial and Industrial Temperature Range

| Syr               | nbol            | Parameter                        |        | P10C68-35<br>P11C68-35 |      | P10C68-45<br>P11C68-45 |    | Notes  |  |

|-------------------|-----------------|----------------------------------|--------|------------------------|------|------------------------|----|--------|--|

| Standard          | Alternative     |                                  | Min. I |                        | Min. | Max.                   |    |        |  |

| tAVAV             | twc             | Write cycle time                 | 45     |                        | 45   |                        | ns |        |  |

| twLWH             | t <sub>WP</sub> | Write pulse width                | 35     |                        | 35   |                        | ns |        |  |

| <sup>t</sup> ELWH | tcw             | Chip enable to end of write      | 35     |                        | 35   |                        | ns |        |  |

| tрумн             | t <sub>DW</sub> | Data set-up to end of write      | 30     |                        | 30   |                        | ns |        |  |

| twhdx             | tDH             | Data hold after end of write     | 0      |                        | 0    |                        | ns |        |  |

| tavwh             | tAW             | Address set-up to end of write   | 35     |                        | 35   |                        | ns |        |  |

| tAVWL             | t <sub>AS</sub> | Address set-up to start of write | 0      |                        | 0    |                        | ns |        |  |

| tWHAX             | twR             | Address hold after end of write  | 0      |                        | 0    |                        | ns |        |  |

| twlqz             | t <sub>WZ</sub> | Write enable to output disable   |        | 35                     |      | 35                     | ns | 11, 14 |  |

| twhqz             | tow             | Output active after end of write | 5      |                        | 5    |                        | ns |        |  |

# NOTES

13. E (bar) or W (bar) must be  $\geq$  VIH during address transitions.

14. If W (bar) is low when E (bar) goes low, the outputs remain in the high impedance state.

Figure 6. WRITE CYCLE 1: W (bar) controlled timing diagram (see notes 8 and 13).

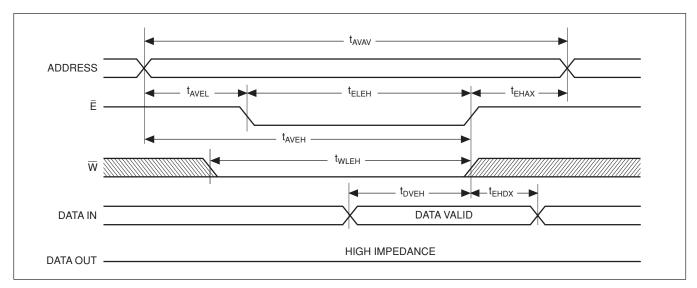

# WRITE CYCLE 2 : E (BAR) CONTROLLED (See notes 8 and 13)

| Syn<br>Standard   | nbol            | Parameter                        |      | P10C68-35<br>P11C68-35 |      | P10C68-45<br>P11C68-45 |    | Notes |

|-------------------|-----------------|----------------------------------|------|------------------------|------|------------------------|----|-------|

|                   | Alternative     |                                  | Min. | Max.                   | Min. | Max.                   |    |       |

| t <sub>AVAV</sub> | twc             | Write cycle time                 | 45   |                        | 45   |                        | ns |       |

| tWLEH             | twp             | Write pulse width                | 35   |                        | 35   |                        | ns |       |

| tELEH             | tcw             | Chip enable to end of write      | 35   |                        | 35   |                        | ns |       |

| <sup>t</sup> DVEH | t <sub>DW</sub> | Data set-up to end of write      | 30   |                        | 30   |                        | ns |       |

| t <sub>EHDX</sub> | t <sub>DH</sub> | Data hold after end of write     | 0    |                        | 0    |                        | ns |       |

| tAVEH             | taw             | Address set-up to end of write   | 35   |                        | 35   |                        | ns |       |

| tEHAX             | twn             | Address hold after end of write  | 0    |                        | 0    |                        | ns |       |

| tAVWL             | tAS             | Address set-up to start of write | 0    |                        | 0    |                        | ns |       |

Figure 7. WRITE CYCLE 2: E (bar) controlled timing diagram (see notes 8 and 13).

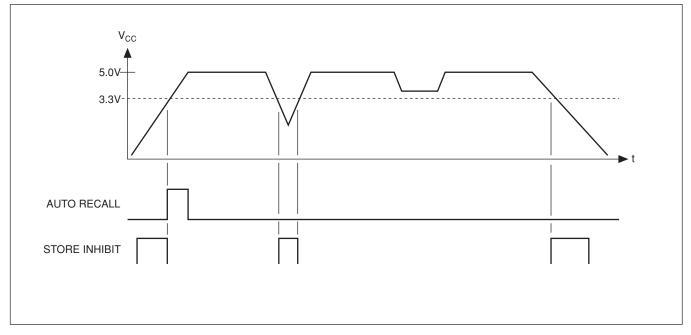

Figure 8. Automatic RECALL and STORE inhibit.

# NON-VOLATILE MEMORY OPERATION OF P10C68 MODE SELECTION

| E | W | <u>G</u> | NE | Mode                          | Power            |

|---|---|----------|----|-------------------------------|------------------|

| Н | Х | Х        | Х  | Not selected                  | Standby          |

| L | Н | L        | Н  | Read RAM                      | Active           |

| L | L | Х        | Н  | Write RAM                     | Active           |

| L | Н | L        | L  | Non-volatile recall (Note 15) | Active           |

| L | L | Н        | L  | Non-volatile store            | I <sub>CC2</sub> |

| L | L | L        | L  | No operation                  | Active           |

| L | Н | Н        | Х  |                               |                  |

# NOTE

An automatic RECALL also takes place on chip power-up, starting when Vcc exceeds 3.3V, and taking t<sub>RECALL</sub> from the time at which Vcc exceeds 3.3V. Vcc must not drop below 3.3V once it has exceeded it for the RECALL to function properly.

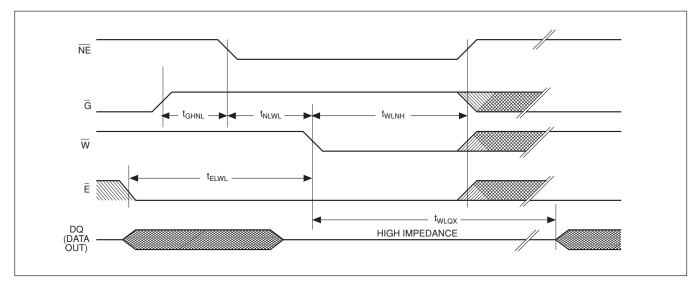

# STORE CYCLE 1 : W (BAR) CONTROLLED (See note 16)

| Syn            | nbol               | Parameter                                                                            | P10C         | 68-35 | P10C         | 68-45 | Units          | Notes |

|----------------|--------------------|--------------------------------------------------------------------------------------|--------------|-------|--------------|-------|----------------|-------|

| Standard       | Alternative        |                                                                                      | Min.         | Max.  | Min.         | Max.  |                |       |

| twlqx<br>tghnl | t <sub>STORE</sub> | Store cycle time<br>Output disable set-up to NE (bar) fall                           | 0            | 10    | 0            | 10    | ms<br>ns       | 17    |

|                | twc                | Non-volatile set-up to write low<br>Write low to NE (bar) rise<br>Chip enable SET-UP | 0<br>45<br>0 |       | 0<br>45<br>0 |       | ns<br>ns<br>ns | 18    |

| LVVL           |                    |                                                                                      |              |       |              |       | 110            |       |

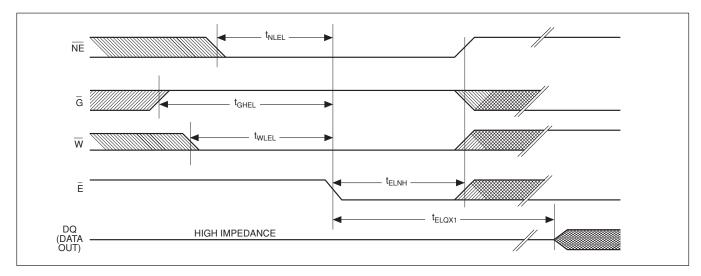

# STORE CYCLE 2 : E (BAR) CONTROLLED (See note 13)

| Syn                                                         | nbol               | Parameter                                                                                                   | P100         | 68-35 | P100         | C68-45 | Units          | Notes |

|-------------------------------------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------|--------------|-------|--------------|--------|----------------|-------|

| Standard                                                    |                    |                                                                                                             | Min.         | Max.  | Min.         | Max.   |                |       |

| tELQX1<br>t <sub>NLEL</sub>                                 | <sup>t</sup> STORE | Store cycle time<br>NE (bar) set-up to chip enable                                                          | 0            | 10    | 0            | 10     | ms<br>ns       | 17    |

| <sup>t</sup> WLEL<br><sup>t</sup> ELNH<br><sup>t</sup> GHEL | twc                | Write enable wet-up to chip enable<br>Chip enable to NE (bar) rise<br>Output disable set-up to E (bar) fall | 0<br>45<br>0 |       | 0<br>45<br>0 |        | ns<br>ns<br>ns | 18    |

### NOTES

16. E (bar), G (bar), NE (bar) and W (bar) must make the transition between VIH(max) to VIL(max), or VIL(max) to VIH(min) in a monotonic fashion.

17. Measured with W (bar) and NE (bar) both returned high, and G (bar) returned low. Note that store cycles are inhibited/aborted by Vcc <3.3V (STORE inhibit).

18. Once two has been satisfied by NE (bar), G (bar), W (bar) and E (bar) the store cycle is completed automatically, ignoring all inputs. Any of NE (bar), G (bar), W (bar) or E (bar) may be used to terminate the store initiation cycle.

Figure 9. STORE CYCLE 1: W (bar) controlled timing diagram (see note 16).

Figure 10. STORE CYCLE 2: E (bar) controlled timing diagram (see note 16).

# P10C68/P11C68

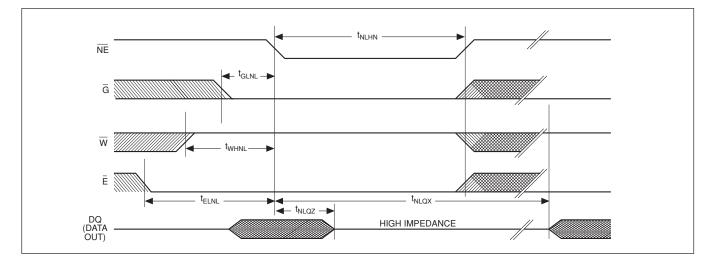

# P10C68 RECALL CYCLE 1 : NE (BAR) CONTROLLED (See note 16)

| Symbol                                             |                | Parameter                                                                                                                                                  | P10C68-35         |          | P10C68-45         |          | Units                            | Notes    |

|----------------------------------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------|-------------------|----------|----------------------------------|----------|

| Standard                                           | Alternative    |                                                                                                                                                            | Min.              | Max.     | Min.              | Max.     |                                  |          |

| tnlqx<br>tnlnh<br>tglnl<br>twhnl<br>telnl<br>tnlqz | trecall<br>trc | Recall cycle time<br>Recall initiation cycle time<br>Output enable set-up<br>Write enable set-up<br>Chip enable set-up<br>NE (bar) fall to output inactive | 25<br>0<br>0<br>0 | 20<br>25 | 25<br>0<br>0<br>0 | 20<br>25 | μs<br>μs<br>ns<br>ns<br>ns<br>ns | 19<br>20 |

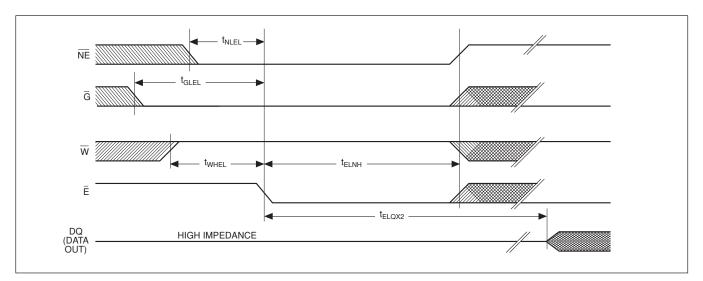

# P10C68 RECALL CYCLE 2 : E (BAR) CONTROLLED (See note 16)

| Symbol                                                 |                | Parameter                                                                                                           | P10C68-35         |      | P10C68-45         |      | Units                      | Notes    |

|--------------------------------------------------------|----------------|---------------------------------------------------------------------------------------------------------------------|-------------------|------|-------------------|------|----------------------------|----------|

| Standard                                               | Alternative    |                                                                                                                     | Min.              | Max. | Min.              | Max. |                            |          |

| t <sub>ELQX2</sub><br>telnh<br>tnlel<br>tglel<br>twhel | tRECALL<br>tRC | Recall cycle time<br>Recall initiation cycle time<br>NE (bar) set-up<br>Output enable set-up<br>Write enable set-up | 25<br>0<br>0<br>0 | 20   | 25<br>0<br>0<br>0 | 20   | μs<br>ns<br>ns<br>ns<br>ns | 19<br>20 |

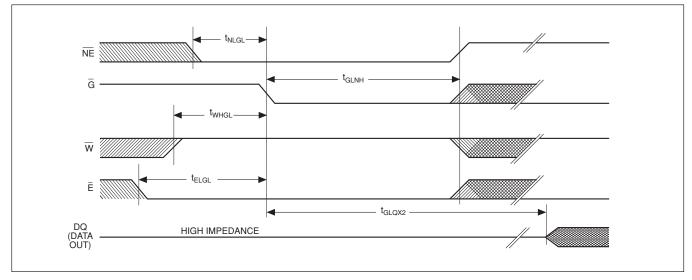

# P10C68 RECALL CYCLE 3 : G (BAR) CONTROLLED (See note 16)

| Symbol                                                                                                 |                                        | Parameter                                                                                                         | P10C68-35         |      | P10C68-45         |      | Units                      | Notes    |

|--------------------------------------------------------------------------------------------------------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------|-------------------|------|-------------------|------|----------------------------|----------|

| Standard                                                                                               | Alternative                            |                                                                                                                   | Min.              | Max. | Min.              | Max. |                            |          |

| <sup>t</sup> GLQX2<br><sup>t</sup> GLNH<br><sup>t</sup> NLGL<br><sup>t</sup> WHGL<br><sup>t</sup> ELGL | <sup>t</sup> RECALL<br><sup>t</sup> RC | Recall cycle time<br>Recall initiation cycle time<br>NE (bar) set-up<br>Write enable set-up<br>Chip enable set-up | 25<br>0<br>0<br>0 | 20   | 25<br>0<br>0<br>0 | 20   | μs<br>ns<br>ns<br>ns<br>ns | 19<br>20 |

# NOTES

19. Measured with W (bar) and NE (bar) both returned high, and G (bar) returned low. Address transitions may not occur on any address pin during this time.

20. Once t<sub>RC</sub> has been satisfied by NE (bar), G (bar), W (bar) and E (bar) the RECALL cycle is completed automatically. Any of NE (bar), G (bar) or E (bar) may be used to terminate the RECALL initiation cycle.

Figure 11. P10C68 RECALL CYCLE 1: NE (bar) controlled timing diagram (see note 16).

Figure 12. P10C68 RECALL CYCLE 2: E (bar) controlled timing diagram (see note 16).

Figure 13. P10C68 RECALL CYCLE 3: E (bar) controlled timing diagram (see note 16).

# NON-VOLATILE MEMORY OPERATION OF P11C68 MODE SELECTION

| _ |   |                                       |                     |               |                  | 1      |

|---|---|---------------------------------------|---------------------|---------------|------------------|--------|

| E | W | A <sub>12</sub> -A <sub>0</sub> (hex) | Mode                | I/O           | Power            | Notes  |

| Н | Х | Х                                     | Not selected        | Output High Z | Standby          |        |

| L | Н | Х                                     | Read RAM            | Output data   | Active           | 22     |

| L | L | Х                                     | Write RAM           | Input Data    | Active           |        |

| L | Н | 0000                                  | Read RAM            | Output Data   | Active           | 21, 22 |

|   |   | 1555                                  | Read RAM            | Output Data   |                  | 21, 22 |

|   |   | 0AAA                                  | Read RAM            | Output Data   |                  | 21, 22 |

|   |   | 1FFF                                  | Read RAM            | Output Data   |                  | 21, 22 |

|   |   | 10F0                                  | Read RAM            | Output Data   |                  | 21, 22 |

|   |   | 0F0F                                  | Non-volatile STORE  | Output High Z | I <sub>CC2</sub> | 20     |

| L | Н | 0000                                  | Read RAM            | Output Data   | Active           | 21, 22 |

|   |   | 1555                                  | Read RAM            | Output Data   |                  | 21, 22 |

|   |   | 0AAA                                  | Read RAM            | Output Data   |                  | 21, 22 |

|   |   | 1FFF                                  | Read RAM            | Output Data   |                  | 21, 22 |

|   |   | 10F0                                  | Read RAM            | Output Data   |                  | 21, 22 |

|   |   | 0F0E                                  | Non-volatile RECALL | Output High Z |                  | 21     |

#### NOTES

- 21. The six consecutive addresses must be in order listed (0000, 1555, 0AAA, 1FFF, 10F0, 0F0F) for a STORE cycle or (0000, 1555, 0AAA, 1FFF, 10F0, 0F0E) for a RECALL cycle. W (bar) must be high during all six consecutive cycles. See STORE CYCLE and RECALL CYCLE tables and diagrams for further details.

- 22. I/O state assumes that G (bar)  $\ge$  V<sub>IL</sub>. Activation of non-volatile cycles does not depend on the state of G (bar).

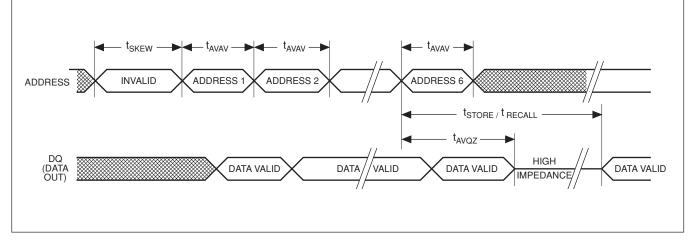

# STORE / RECALL CYCLES 1 AND 2 (See notes 24 and 29)

| Symbol            |                  | Parameter                                       | P11C68-35 |      | P11C68-45 |      | Units | Notes  |

|-------------------|------------------|-------------------------------------------------|-----------|------|-----------|------|-------|--------|

| Standard          | Alternative      |                                                 | Min.      | Max. | Min.      | Max. |       |        |

| t <sub>avav</sub> | t <sub>ACS</sub> | Read cycle time                                 | 35        |      | 45        |      | ns    |        |

| t <sub>AXAV</sub> | tSKEW            | Skew between sequentially<br>adjacent addresses |           | 5    |           | 5    | ns    | 23     |

| tavoz             | tELQZ            | Address valid to output inactive                |           | 75   |           | 75   | ns    | 25     |

|                   | tSTORE           | Store cycle time                                |           | 10   |           | 10   | ms    | 26     |

|                   | tRECALL          | Recall cycle time                               |           | 20   |           | 20   | μs    | 26, 30 |

| <b>t</b> AVEL     | tAE              | Address set-up to chip enable                   | 0         |      | 0         |      | ns    | 27     |

| tELEH             | t <sub>EP</sub>  | Chip enable pulse width                         | 35        |      | 45        |      | ns    | 27     |

| tEHAX             | t <sub>EA</sub>  | Chip disable to address change                  | 0         |      | 0         |      | ns    | 27     |

# NOTES

- 23. Skew spec may be avoided by using E (bar) (STORE/RECALL CYCLE 2).

- 24. W (bar)  $\ge$ V<sub>IH</sub> during entire address sequence to initiate a non-volatile cycle. Required address sequences are shown in the Mode Selection table.

- 25. Once the software STORE or RECALL cycle is initiated, it completes automatically, ignoring all inputs.

- 26. Measured with W (bar) high, G (bar) low and E (bar) low. Note that STORE cycles (but not RECALLS) are aborted by Vcc < 3.3V (STORE Inhibit).

- 27. E (bar) must make the transition between VIH(max) to VIL(max), or VIL(max) to VIH(min) in a monotonic fashion.

- 28. Chip is continuously selected with E (bar) low.

- 29. Addresses 1 through 6 are found in the Mode Selection table. Address 6 determines whether the P11C68 performs a STORE or RECALL. A RECALL cycle is performed automatically at power up when V<sub>CC</sub> exceeds 3.3V. V<sub>CC</sub> must not drop below 3.3V once it has exceeded it for the RECALL to function properly, t<sub>RECALL</sub> is measured from the point at which V<sub>CC</sub> exceeds 3.3V.

- 30. Address transitions may not occur on any address pin during this time.

Figure 14. STORE/RECALL cycle 1. Address controlled timing diagram (see notes 22, 26 and 27).

Figure 15. STORE/RECALL cycle 2. E (bar) controlled timing diagram (see notes 22, 25 and 27).

#### **OPERATING NOTES**

Note: References to NE (bar) should be taken as applying to P10C68 only and can be ignored for P11C68.

The devices have two separate modes of operation: SRAM mode and non-volatile mode. In SRAM mode, the memory operates as an ordinary static RAM. While in non-volatile mode, data is transferred in parallel from SRAM to EEPROM or from EEPROM to SRAM.

#### SRAM READ

The devices perform a read cycle when ever E (bar) and G (bar) are LOW and NE (bar) and W (bar) are HIGH. The address specified by the thirteen address pins  $A_{0.12}$  determine which of the 8192 data bytes will be accessed. When the READ is initiated by an address transistion, the outputs will be valid after a delay of  $t_{AVQV}$  (READ CYCLE 1).

If the READ is initiated by E (bar) or G (bar), the outputs will be valid at  $t_{ELOV}$  or  $t_{GLQV}$ , whichever is later. (READ CYCLE 2). The data outputs will repeatedly respond to address changes within the  $t_{AVQV}$  access time without the need for transitions on any control input pins and will remain valid until another address change or until E (bar) or G (bar) is brought HIGH or W (bar) or NE (bar) is brought LOW.

#### **SRAM WRITE**

A write cycle is performed whenever E (bar) and W (bar) are LOW and NE (bar) is HIGH. The address inputs must be stable prior to entering the WRITE cycle and must remain stable until either E (bar) or W (bar) go HIGH at the end of the cycle. The data on the eight pins  $DQ_{0-7}$ , will be written into the memory location specified by the address inputs if valid  $t_{\text{DVWH}}$  before the end of a W (bar) controlled WRITE or  $t_{\text{DVEH}}$  before the end of an E (bar) controlled WRITE.

It is recommended that G (bar) be kept HIGH during the entire WRITE cycle to avoid data bus contention on the common I/O lines. If G (bar) is left LOW, internal circuitry will turn off the output buffers  $t_{WHOZ}$  after W (bar) goes LOW.

#### Non-Volatile STORE - P10C68

A STORE cycle is performed when NE, (bar) E (bar) and W (bar) are LOW and G (bar) is HIGH. While any sequence to achieve this state will initiate a STORE, only W(bar) initiation (STORE CYCLE 1) and E (bar) initiation (STORE CYCLE 2) are practical without risking an unintentional SRAM WRITE that would disturb SRAM data. During the STORE cycle, previous non-volatile data is erased and the SRAM contents are then programmed into non-volatile elements. Once a STORE cycle is initiated, further input and output is disabled and the DQ<sub>0-7</sub> pins are tri-stated until the cycle is completed.

If E (bar) and G (bar) are LOW and W (bar) and NE (bar) are HIGH at the end of the cycle, a READ will be performed and the outputs will go active, signalling the end of the STORE.

The P10C68 will not be activated into either a STORE or RECALL cycle by the software sequence required for the P11C68.

### Hardware Protect - P10C68

The P10C68 offers two levels of protection to suppress inadvertent STORE cycles. If the clock signals remain in the STORE condition at the end of a STORE cycle, a second STORE cycle will not be started. The STORE will be initiated only after a HIGH to LOW transition on NE (bar)Because the STORE cycle is initiated by an NE (bar) transition, poweringup the chip with NE (bar) Low will not initiate a STORE cycle either.

In addition to multi-trigger protection, the P10C68 offers hardware protection through Vcc Sense. A STORE cycle will not be initiated, and one in progress will discontinue, if Vcc goes below 3.3V.

#### Non-Volatile RECALL - P10C68

A RECALL cycle is performed when E (bar), G (bar) and NE (bar) are LOW and W (bar) is HIGH. Like the STORE cycle, RECALL is initiated when the last of the four clock signals goes to the RECALL state. Once initiated, the RECALL cycle will take  $t_{NLQX}$  to complete, during which all inputs are ignored. When the RECALL completes, any READ or WRITE state on the input pins will take effect.

Internally, RECALL is a two step procedure. First the SRAM data is cleared and second, the non-volatile information is transferred into the SRAM cells. The RECALL operation in no way alters the data in the non-volatile cells. The non-volatile data can be recalled an unlimited number of times. Address transitions may not occur during the RECALL cycle. Like the STORE cycle, a transition must occur on the NE (bar) pin to cause a RECALL, preventing inadvertent multi-triggering. On power-up, once Vcc exceeds Vcc sense voltage of 3.3V, a RECALL cycle is automatically initiated. The voltage on the Vcc pin must not drop below 3.3V once it has risen above it in order for the RECALL to operate properly. Due to the automatic RECALL, SRAM operation cannot commence until  $t_{NLOX}$  after Vcc exceeds 3.3V.

The P11C68 STORE cycle is initiated by executing sequential READ cycles from six specific address locations. By relying on READ cycles only, the P11C68 implements non-volatile operation while remaining pin-for-pin compatible with standard 8Kx8 SRAMs. During the STORE cycle, an erase of the previous non-volatile data is first performed, followed by a program of the non-volatile elements. The program operation copies the SRAM data into non-volatile storage. Once a STORE cycle is initiated, further input and output are disabled until the cycle is completed. Because a sequence of addresses is used for STORE initiation, it is critical that no invalid address states intervene in the sequence or the sequence will be aborted. The maximum skew between address inputs A0-12 for each address state is  $t_{SKEW}$  (STORE CYCLE 1).

If  $t_{SKEW}$  is exceeded it is possible that the transitional data state will be interpreted as a valid address and the sequence will be aborted. If E (bar) controlled READ cycles are used for the sequence (STORE CYCLE 2), address skew is no longer a concern.

To enable the STORE cycle the following READ sequence must be performed.

- 1. Read address 0000 (hex) Valid READ

- 2. Read address 1555 (hex) Valid READ

- 3. Read address 0AAA (hex) Valid READ

- 4. Read address 1FFF (hex) Valid READ

- 5. Read address 10F0 (hex) Valid READ

- 6. Read address 0F0F (hex) Initiate STORE Cycle

Once the sixth address in the sequence has been entered, the STORE cycle will commence and the chip will be disabled. It is important that READ cycles and not WRITE cycles be used in the sequence, although it is not necessary that G (bar) be LOW for the sequence to be valid. After the  $t_{\text{STORE}}$  cycle time has been fulfilled, the SRAM will again be activated for READ and WRITE operation.

Once the first of the six reads has taken place, the read sequence must either complete or terminate with an incorrect address (other than 0000 hex) before it may be started anew.

The P11C68 offers hardware protection against inadvertent STORE cycles through Vcc Sense. A STORE cycle will not be initiated, and one in progress will discontinue, if Vcc goes below 3.3V.

A RECALL of the EEPROM data into the SRAM is initiated with a sequence of READ operations in a manner similar to the STORE initiation. To initiate the RECALL cycle the following sequence of READ operations must be performed:

- 1. Read address 0000 (hex) Valid READ

- 2. Read address 1555 (hex) Valid READ

- 3. Read address 0AAA (hex) Valid READ

- 4. Read address 1FFF (hex) Valid READ

- 5. Read address 10F0 (hex) Valid READ

- 6. Read address 0F0E (hex) Initiate RECALL Cycle

Internally, RECALL is a two step procedure. First, the SRAM data is cleared and second the non-volatile information is transferred into the SRAM cells. The RECALL operation in no way alters the data in the EEPROM cells. The non-volatile data can be recalled an unlimited number of times. Address transitions may not occur during the RECALL cycle.

On power-up, once Vcc exceeds the Vcc sense voltage of 3.3V, a RECALL cycle is automatically initiated. The voltage on the Vcc pin must not drop below 3.3V once it has risen above it in order for the RECALL to operate properly. Due to this automatic RECALL, SRAM operation cannot commence until  $t_{\text{RECALL}}$  after Vcc exceeds 3.3V.

The automatic RECALL feature can be adversely affected by factors such as supply rise time, temperature and elapsed time since the last STORE cycle. For this reason it is recommended that the user initiate a RECALL cycle after power-up for critical applications.

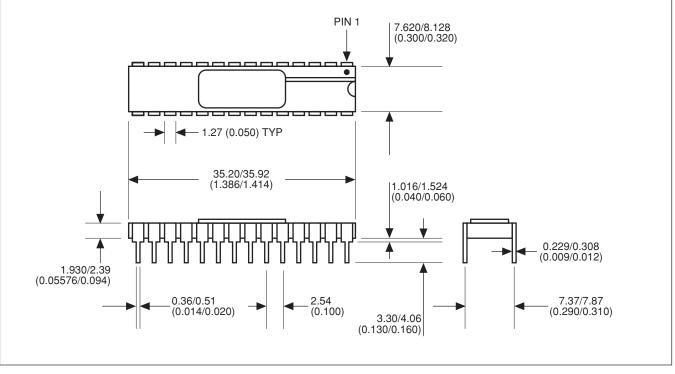

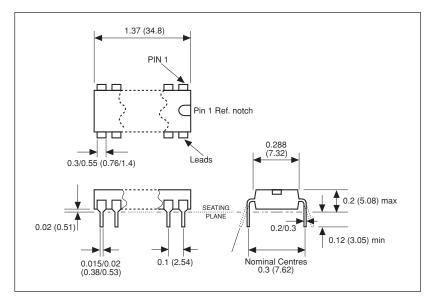

# PACKAGE DETAILS

Dimensions are shown thus: mm (in). For further package information please contact your local Customer Service Centre.

Figure 16, 28-lead sidebrazed ceramic DIL (0.3in) DCB

Figure 17. 28 plastic DIL Package (0.3in) DPB

#### **ORDERING INFORMATION**

# PxxC68 - xx / xG / DxBS Device number eg. 10 = hardware store/recall 11 = software store/recall Temperature range C = Commercial I = Industrial

#### Speed Grade -35 = 35ns

-45 = 45ns

#### HEADQUARTERS OPERATIONS GEC PLESSEY SEMICONDUCTORS

Cheney Manor, Swindon, Wiltshire SN2 2QW, United Kingdom. Tel: (0793) 518000 Tx: 449637 Fax: (0793) 518411

#### GEC PLESSEY SEMICONDUCTORS

Sequoia Research Park, 1500 Green Hills Road, Scotts Valley, California 95066, United States of America. Tel (408) 438 2900 ITT Telex: 4940840 Fax: (408) 438 5576 CUSTOMER SERVICE CENTRES

- FRANCE & BENELUX Les Ulis Cedex Tel: (1) 64 46 23 45 Tx: 602858F Fax : (1) 64 46 06 07

- GERMANY Munich Tel: (089) 3609 06-0 Tx: 523980 Fax : (089) 3609 06-55

- ITALY Milan Tel: (02) 66040867 Fax: (02) 66040993

- JAPAN Tokyo Tel: (03) 3296-0281 Fax: (03) 3296-0228

- NORTH AMERICA Integrated Circuits and Microwave Products, Scotts Valley, USA Tel (408) 438 2900 ITT Tx: 4940840 Fax: (408) 438 7023.

Hybrid Products, Farmingdale, USA Tel (516) 293 8686 Fax: (516) 293 0061.

- SOUTH EAST ASIA Singapore Tel: 2919291 Fax: 2916455

- SWEDEN Johanneshov Tel: 46 8 702 97 70 Fax: 46 8 640 47 36

- UNITED KINGDOM & SCANDINAVIA

- Swindon Tel: (0793) 518510 Tx: 444410 Fax : (0793) 518582

These are supported by Agents and Distributors in major countries world-wide.

© GEC Plessey Semiconductors Year Publication No. XX XXXX Issue No. X.X Month Year

This publication is issued to provide information only which (unless agreed by the Company in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. The Company reserves the right to alter without prior knowledge the specification, design or price of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any reduct any such information and to ensure that any publication or data used is up to date and has not been superseded. These products are not suitable for use in any medicat products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and service sprovided subject to the Company's conditions of sale, which are available on request.

http://www.mitelsemi.com

#### World Headquarters - Canada

Tel: +1 (613) 592 2122 Fax: +1 (613) 592 6909

#### North America

Tel: +1 (770) 486 0194 Fax: +1 (770) 631 8213

#### Asia/Pacific

Tel: +65 333 6193 Fax: +65 333 6192

# Europe, Middle East, and Africa (EMEA) Tel: +44 (0) 1793 518528 Fax: +44 (0) 1793 518581

Information relating to products and services furnished herein by Mitel Corporation or its subsidiaries (collectively "Mitel") is believed to be reliable. However, Mitel assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Mitel or licensed from third parties by Mitel, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Mitel, or non-Mitel furnished goods or services may infringe patents or other intellectual property rights owned by Mitel.

This publication is issued to provide information only and (unless agreed by Mitel in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Mitel without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or services (Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Mitel's conditions of sale which are available on request.

M Mitel (design) and ST-BUS are registered trademarks of MITEL Corporation Mitel Semiconductor is an ISO 9001 Registered Company Copyright 1999 MITEL Corporation All Rights Reserved Printed in CANADA

TECHNICAL DOCUMENTATION - NOT FOR RESALE