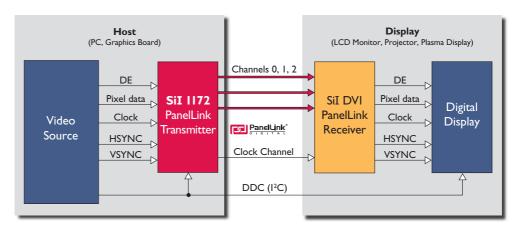

The Sil II72 is the world's first single-link TMDS™ transmitter to break the bandwidth barrier and support an amazing 225 MHz bandwidth. The latest addition to Sil's comprehensive Sil 1000 family of DVI solutions, the Sil II72 transmitter incorporates next-generation PanelLink® technology to support bandwidths of 25 to 225 MHz. As a result, the Sil II72 supports LCD monitors and projectors with resolutions that range from VGA to QXGA (2048 x 1536).

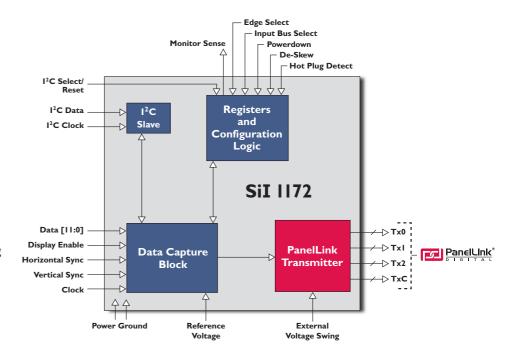

Three TMDS data channels for RGB send data at up to 2.25 Gbps per channel. The Sil II72 incorporates an industry-standard I2-bit (I/2 pixel per clock edge) interface for true color (I6.7 million) support. Built-in flexibility enables customers to use pins to configure settings or the I<sup>2</sup>C interface to program registers.

The Sil 1172 is available in a low-cost, easier-to-use, 48-pin TSSOP package with a 57% smaller footprint compared to other discrete DVI transmitters. By incorporating the most advanced PanelLink DVI technology available today, the Sil 1172 transmitter brings higher performance and guaranteed compatibility to single-link DVI applications while enabling faster time to market, smaller form factor designs and lower system costs.

#### **DVI-compliant Quality**

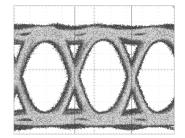

The DVI 1.0 specification defines the precise system-level signaling at the output of a DVI transmitter system and at the input of a DVI receiver system. As a result, any DVI-compliant host will always interoperate with any DVI-compliant display. The most comprehensive method to determine the quality and compliance of a DVI transmitter is to measure the TMDS "eye" diagram as defined by the DVI 1.0 specification and the DVI Test & Measurement Guide. Only high-performance PanelLink DVI transmitters, such as the Sil 1172, yield consistently robust differential signal "eyes" that exceed the minimum "eye" width & height requirements of the DVI specification throughout the full DVI bandwidth of 25-165 MHz. At bandwidths above 165 MHz, the Sil 1172 is interoperable with PanelLink receivers also rated to run over 165 MHz.

### **Applications**

- PC Motherboards

- · Graphics Boards

- Notebook PCs

Sil 1172 TMDS "eye" diagram measured at 225 MHz.

# Sil 1172 Features

#### PanelLink® Transmitter

- Scalable bandwidth from 25 to 225 MHz (VGA to QXGA)

- Three TMDS<sup>™</sup> data channels capable of transferring up to 2.25 Gbps per channel

- Inter-pair skew tolerance up to I input clock cycle (4.5 ns at 225 MHz)

- Adjustable TMDS low-voltage swing amplitude for long cable support

- DC-balanced signals for direct coupling to fiber-optic ready modules

- Operates with all DVI I.0-compliant receivers

- Supports Hot Plug Detect and Receiver Sensing

#### Input

- Flexible graphics controller interface:

I.0V I.9V (DVO) or 3.3V

(CMOS) interface voltages

- 12-bit input for true color (16.7 million) support

- De-skewing option to vary clock to data timing

- Supports dual-edge single clock or dual-edge differential clock

- Selectable primary edge of parallel data

- Programmable through I<sup>2</sup>C interface or configurable by pin settings

## **Power Management**

- 3.3V core provides low-power operation

- · Low-power standby mode

# Silicon Image's Sil 1172 Starter Kits

Sil 1172 starter kits are available for various motherboard and graphics chipset platforms. For details, please see Starter Kits/Reference Designs on the Silicon Image website at www.siliconimage.com

#### Part Number - Sill172CS48

©2003 Silicon Image, Inc. All rights reserved. Silicon Image, the Silicon Image logo, Sil, Sil 1172, PanelLink, the PanelLink logo and TMDS are trademarks or registered trademarks of Silicon Image, Inc. in the United States and other countries. Other trademarks are the property of their respective holders. Product specifications are subject to change without notice. Printed in the U.S.A. 6/03 Sil PB-0040

Silicon Image, Inc. 1060 E. Arques, Sunnyvale, CA 94085 T 408.616.4000 F 408.830.9530 www.siliconimage.com