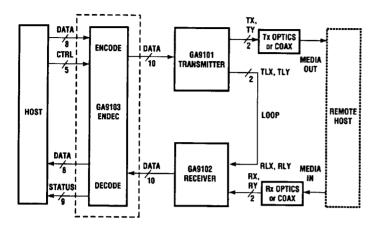

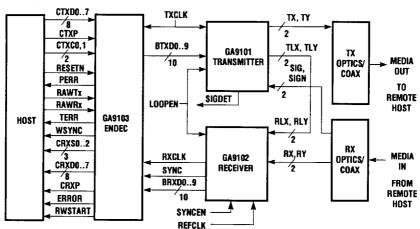

TriQuint's GA9103 is one of the three devices of the FC–265 chip set designed to support the requirements of Fiber Channel Standard X3T9.3. The GA9103 is an encoder/decoder (ENDEC) integrated circuit which implements the 8b/10b encoding/decoding scheme for data, ordered sets and line states associated with the Fiber Channel Physical Level Standard (FC-PH). In addition, the CMOS ENDEC chip performs 32-bit CRC and parity generate/check functions. It interfaces to TriQuint's GA9101 and GA9102 Transmitter and Receiver, respectively, and to either the fabric or the device link protocol controller.

The FC–265 (GA9101, GA9102 and GA9103) provides a comprehensive electrical and physical interface for Fiber Channel. These chips are designed to operate at 265.625 Megabaud, one of the operating speeds specified by the standard.

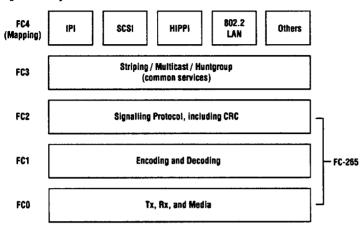

The Fiber Channel provides a transport vehicle for the upper layer Intelligent Peripheral Interface (IPI) and Small

Computer System Interface (SCSI) command sets, the High-Performance Parallel Interface (HIPPI) data link layer, and other user-defined command sets. The Fiber Channel is capable of replacing the SCSI, IPI, and HIPPI physical interfaces with a protocol-efficient alternative that provides performance improvements in distance and/or speed.

IPI and SCSI commands and HIPPI data link operations may all be intermixed on the Fiber Channel. Proprietary and other command sets may also use and share the Fiber Channel. See Figure 1.

The Fiber Channel is optimized for predictable transfers of large blocks of data such as those used in file transfers between processors (supercomputer, mainframe, super-mini, etc.), storage systems (disk and tape), communications, and output-only devices such as laser printers and raster-scan graphics terminals.

GA9103

# **265 Mbaud Fiber Channel ENDEC**

#### Features

- For Fiber Channel, point-topoint, network, and SCSI applications

- With fiber optics, the FC-265 chip set provides a complete FC-0. FC-1 solution

- 8b/10b Encode/Decode of data, ordered sets, and line states

- TTL-compatible 10-bit-wide Transmitter/Receiver interface with 26.5625 MHz byte clock

- CRC and Parity Generate/ Check

- Common chip for fabric and device adapters

- Multiplexed data/control 8-bit system interface

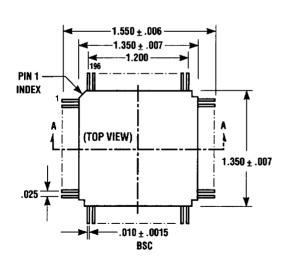

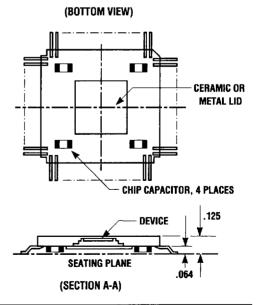

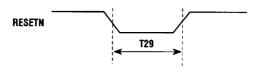

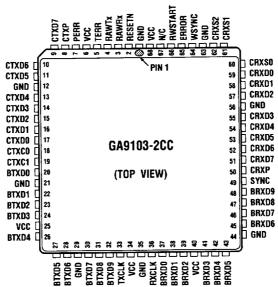

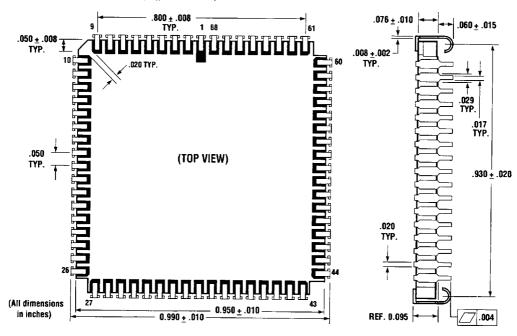

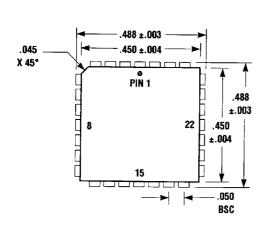

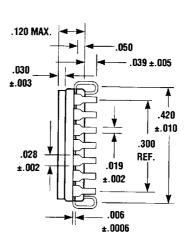

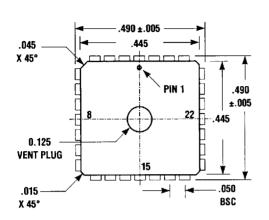

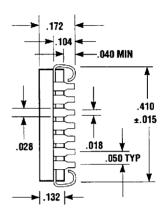

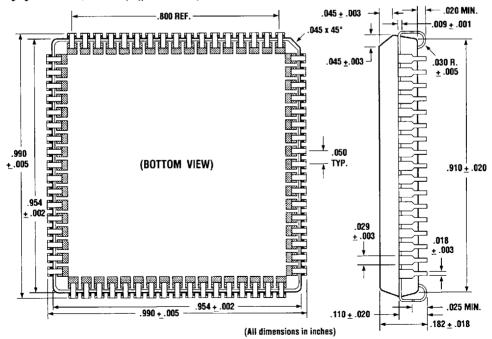

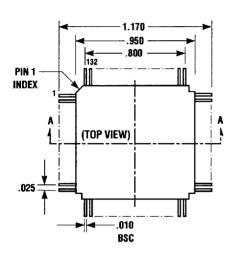

- 68-pin PLCC

The Transmitter/Receiver chips, designed with TriQuint's proprietary 0.7 micron One-Up™GaAs process, interface either directly to the electrical medium or to the fiber-optic interface. The chips implement parallel-to-serial conversion, bit clock generation, receive clock/data recovery, and serial-to-parallel conversion.

The Fiber Channel protocol is simple and economical and enhances system

throughput. The transmission medium is isolated from the control protocol so that implementation of point-to-point links, multi-drop buses, rings, crosspoint switches, or other special implementations may be made in a technology best suited to the usage environment. Fiber channel is organized into five layers as shown in Figure 1. With this standard, the user may communicate over distances up to 10 km

at baud rates of 132.8125 Megabaud to 1.0625 Gigabaud. This standard will support links over coaxial and fiber-optic cables.

Along with a fiber-optic module, this chipset will provide complete FC-0 and FC-1 solutions for a Fiber Channel data link.

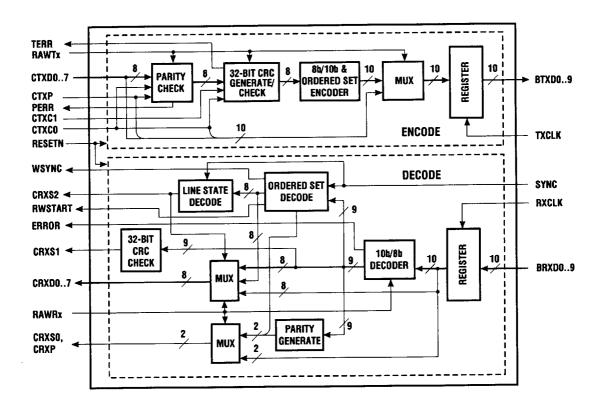

#### GA9103 ENDEC Block Diagram

Figure 1. Layers of Fiber Channel

#### **Functional Description**

The GA9103 has an 8-bit interface to the host side and a 10-bit interface to the Transmitter (Tx) and the Receiver (Rx). The device has two major independent functional blocks, the ENCODE and the DECODE. The ENCODE block interfaces with the Tx and the DECODE with the Rx. Below are the details of the two functional blocks.

#### Encode

The PARITY CHECK block compares the input odd parity with that of the incoming data, CTXDO..7 and CTXCO. If the number of ones in the input is an even number, CTXP will be HIGH. If the number of ones in the input data is odd, CTXP will be LOW. If there is a parity error, it is flagged through the PERR signal. In the pass-through mode (RAWTx=1), PERR is forced to zero.

The 32-bit Generate/Check CRC block either generates or checks the 32-bit CRC for the incoming 8-bit bus, CTXD0..7. The methodology, polynomials, and equations for the 32-bit CRC are the same as the

FDDI's Frame Check Sequence, as adopted by Fiber Channel. A 32-bit CRC is computed for every frame and the computation begins after the receipt of the Start-of-Frame (SOF) ordered set and finishes one byte before the End-of-Frame (EOF). The CRC corresponds to the ones complement of the remainder obtained by dividing the frame sequence polynomial H(x) by the following generator polynomial:

$$G(x) = X^{32} + X^{26} + X^{23} + X^{22} + X^{16} + X^{12} + X^{11} + X^{10} + X^{8} + X^{7} + X^{5} + X^{4} + X^{2} + X + 1$$

The frame sequence polynomial is formed as follows: the bits of the frame are treated as a coefficient of a polynomial D(x) of order k, where k is one degree less than the total number of bits. The polynomial H(x) is formed by multiplying D(x) by  $X^{32}$  and inverting the 32 terms of the resulting polynomial starting at the X(k+32) term. The order of computation within a byte is made starting with the least significant bit (CTXD0) and continuing through to the most significant bit (CTXD7). The CRC is

appended to the incoming data, starting with the most significant coefficient (X<sup>31</sup>) and continuing through to the least significant coefficient.

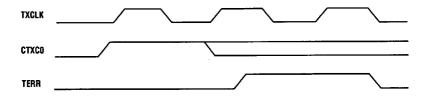

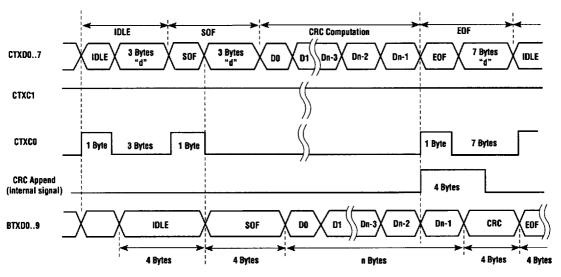

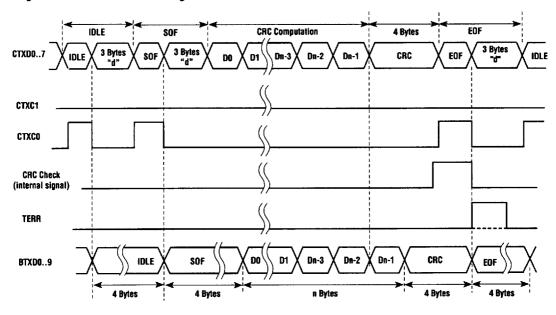

The CRC check is performed by checking the remainder at the end of the incoming frame against the expected value. If the incoming CRC is correct, the remainder should be "C704DD7B" (Hex), in the order of reception. If an error occurs, it is flagged by the TERR pin. In the pass-through mode, the CRC function is disabled. The Generate CRC function is enabled at the device interface and the Check CRC function is enabled at the fabric interface by means of the CTXC1 input signal. A logic HIGH on the CTXC1 pin indicates the Generate CRC function is selected, while a logic LOW indicates that the Check CRC is selected. When initiated, the Generate/Check CRC commences after the Start-of-Frame signal. and ends prior to the End-of-Frame signal. (See Figures 3 and 4.)

To start the computation of the 32-bit Generate CRC mode in the ENCODE block. the following conditions must be met: CTXC1 is HIGH, the previous encoded word was Start-of-Frame (SOF), and the CTXC0 signal goes from HIGH to LOW. The CRC computation is complete when the CTXC0 signal goes back HIGH. The CTXC0 signal must be HIGH for at least four byte clocks in order to append the CRC to the transmitted data. In the Generate CRC mode, the signal at the TERR pin (CRC Error) is LOW. The timing for the Generate CRC mode is shown in Figure 3. While the internal logic does check for parity during the CRC Append cycle, the four input bytes at CTXD0..7 are ignored.

To initiate the 32-bit Check CRC mode in the ENCODE block, the following state is required: the CTXC0 signal goes from HIGH to LOW, the previous encoded ordered set was SOF, and CTXC1 is LOW. When the CTXC0 signal goes back to HIGH, the CRC computation is complete. The computed value is compared to "C704DD7B" (Hex) to see if an error occurred. If there is a CRC error, it is flagged through the TERR pin going HIGH for one byte time at the End-of-Frame. The timing for the Check CRC mode is shown in the figure below and in Figure 4.

The 8b/10b and Ordered Set ENCODER encodes the data as per the Fiber Channel rules for encoding. The encoding of valid data and special characters are shown in Tables 1 and 2. The tables have two columns of encoded output based on the current Running Disparity (R<sub>D</sub>). The current Running Disparity may be positive or negative on power up, but on RESETN being activated, it is always negative. A new Running Disparity is calculated from the transmitted character. It is forced negative if: 1) Sig = 1, CTXC0 = 1, and the Ordered Set encode is a primitive, such as R-Rdy, etc., or 2) when the link exits the diagnostic (RAW) mode. The ordered sets are then encoded according to Table 3. Each ordered set is four bytes wide.

The ordered set encoding procedure is as follows: the ENCODER looks at the CXTD0..7 signal inputs while the Ordered Set, CXTC0, signal is HIGH and encodes four bytes, based on the contents of CTXD0..7. The contents of CTXD0..7 in the next three bytes are ignored.

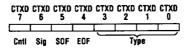

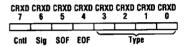

Figure 2. Data Fields for Fiber Channel Ordered Set Encoding

The fields within the first byte, CTXD0..7, of the word for the Ordered Set Encoding is shown in Figure 2. CTXD7 corresponds to the Cntl signal. The Cntl signal, when LOW, indicates Fiber Channel-defined ordered sets are being transmitted. When the Cntl signal is HIGH, undefined ordered sets are being transmitted. The Sig signal (CTXD6), when HIGH, indicates the Line State ordered set is being transmitted, and, when LOW, indicates an ordered set other than the Line State is being transmitted. SOF (CTXD5), when HIGH, indicates the Start-of-Frame ordered set is being transmitted, and EOF (CTXD4), when HIGH, indicates the End-of-Frame ordered set is being transmitted. Type (CTXD3..0) indicates the type of ordered sets within the SOF, EOF, Line States and Undefined categories that is being transmitted.

If PERR or TERR is HIGH within a frame,  $EOF_n$  and  $EOF_t$  for that particular frame are transmitted as  $EOF_{ni}$  (see Table 3). Similarly, if PERR or TERR is HIGH while  $EOF_{dt}$  is being transmitted, it is encoded as  $EOF_{dt}$ , to indicate an invalid condition at the node.

The MUX selects between the 8b/10b ENCODER output and the data inputs, CTXD0..7. When the RAWTx input signal is HIGH, the inputs CTXD0..7, CTXP, and CTXC0 are selected, and TERR = 0. When the RAWTx input is LOW, the ENCODER output is selected. The output of the MUX is 10 bits wide and is clocked into the REGISTER using the transmit byte clock, TXCLK, from the Transmitter chip, GA9101. The output of the REGISTER interface goes directly to the GA9101, the Transmitter I.C. of the FC-265.

The asynchronous RESETN input, when LOW, is used to clear all internal state machine registers. It will take up to five byte clocks to clear the internal state machines after the RESETN input goes back HIGH.

The bit ordering for transmission in the RAW mode is CTXD0..7, CTXP1 and CTXC0. It corresponds to mapping these signals to BTXD9..0, respectively.

#### **CRC Error Timing**

Figure 3. Generate CRC Mode Timing

<sup>&</sup>quot;n" is the data packet size. "n" is divisible by 4 "d" is "don't care," but parity is checked.

Figure 4. Check CRC Mode Timing

Table 1. Valid Data Characters - Encoding

| Data           |            | Bits           | Current          | RO -              | Corrent          | RD+               | Data<br>Byte   |            | Bits           | Current          | RD +              | Cerrent          | AD+                 |

|----------------|------------|----------------|------------------|-------------------|------------------|-------------------|----------------|------------|----------------|------------------|-------------------|------------------|---------------------|

| Byle<br>Name   | HGF        | EDCBA 1        | abodei           | ighj <sup>2</sup> | abcdel           | ighj <sup>2</sup> | Name           | HGF        | EDCBA 1        | abcdei           | tghj <sup>2</sup> | abcdei           | tghj ²              |

| D0.0           | 000        | 00000          | 100111           | 0100              | 011000           | 1011              | D9.2           | 010        | 01001          | 100101           | 0101              | 100101           | 0101                |

| D1.0           | 000        | 00001          | D11101           | 0100              | 100010           | 1011              | D10.2          | 010        | 01010          | 010101           | 0101              | 010101           | 0101                |

| D2.0           | 000        | 00010          | 101101           | 0100              | 010010           | 1011              | D11.2          | 010        | 01011          | 110100           | 0101              | 110100           | 0101                |

| D3.0           | 000        | 00011          | 110001           | 1011              | 110001           | 0100              | D12.2<br>D13.2 | 010<br>010 | 01100<br>01101 | 001101<br>101100 | 0101<br>0101      | 001101<br>101100 | 0101<br>0101        |

| D4.0           | 000        | 00100<br>00101 | 110101<br>101001 | 0100<br>1011      | 001010<br>101001 | 1011<br>0100      | D13.2          | 010        | 01110          | 011100           | 0101              | 011100           | 0101                |

| D5.0<br>D6.0   | 000        | 00101          | 011001           | 1011              | 011001           | 0100              | D15.2          | 010        | 01111          | 010111           | 0101              | 101000           | 0101                |

| D7.0           | 000        | 00111          | 111000           | 1011              | 000111           | 0100              | D16.2          | 010        | 10000          | 011011           | 0101              | 100100           | 0101                |

| D8.0           | 000        | 01000          | 111001           | 0100              | 000110           | 1011              | D17.2          | 010        | 10001          | 100011           | 0101              | 100011           | 0101                |

| D9.0           | 000        | 01001          | 100101           | 1011              | 100101           | 0100              | D18.2          | 010        | 10010          | 010011           | 0101              | 010011           | 0101                |

| D10.0          | 000        | 01010          | 010101           | 1011              | 010101           | 0100              | D19.2          | 010        | 10011          | 110010           | 0101              | 110010           | 0101                |

| D11.0          | 000        | 01011          | 110100           | 1011              | 110100           | 0100              | D20.2<br>D21.2 | 010        | 10100<br>10101 | 001011<br>101010 | 0101<br>0101      | 001011<br>101010 | 0101<br>0101        |

| D12.0<br>D13.0 | 000        | 01100<br>01101 | 001101<br>181100 | 1011              | 001101<br>101100 | 0100<br>0100      | D22.2          | 010        | 10110          | 011010           | 0101              | 011010           | 0101                |

| D14.0          | 000        | 01110          | 011100           | 1011              | 011100           | 0100              | D23.2          | 010        | 10111          | 111010           | 0101              | 000101           | 0101                |

| D15.0          | 000        | 01111          | 010111           | 0100              | 101000           | 1011              | D24.2          | 010        | 11000          | 110011           | 0101              | 001100           | 0101                |

| D16.0          | 000        | 10000          | 011011           | 0100              | 100100           | 1011              | D25.2          | 010        | 11001          | 100110           | 0101              | 100110           | 0101                |

| D17.0          | 600        | 10001          | 100011           | 1011              | 100011           | 0100              | D26.2          | 010        | 11010          | 010110           | 0101              | 010110           | 0101                |

| D18.0          | 000        | 10010          | 010011           | 1011              | 010011           | 0100              | D27.2          | 010        | 11011          | 110110           | 0101              | 001001           | 0101                |

| D19.0          | 000        | 10011          | 110010           | 1011              | 110010           | 0100              | D28.2<br>D29.2 | 010<br>010 | 11100<br>11101 | 001110<br>101110 | 0101<br>0101      | 001110<br>010001 | 0101<br>0101        |

| D20,0<br>D21.0 | 000        | 10100<br>10101 | 001011<br>101010 | 1011<br>1011      | 001011<br>101010 | 0100<br>0100      | D30.2          | 010        | 11110          | 011110           | 0101              | 100001           | 0101                |

| D22.0          | 000        | 10110          | 011010           | 1011              | 011010           | 0100              | D31.2          | 010        | 11111          | 101011           | 0101              | 010100           | 0101                |

| D23.0          | 000        | 10111          | 111010           | 0100              | 000101           | 1011              | D0.3           | 011        | 00000          | 100111           | 0011              | 011000           | 1100                |

| D24.0          | 000        | 11000          | 110011           | 0100              | 001100           | 1011              | D1.3           | 011        | 00001          | 011101           | 0011              | 100010           | 1100                |

| D25.0          | 000        | 11001          | 100110           | 1011              | 100110           | 0100              | D2.3           | 011        | 00010          | 101101           | 0011              | 010010           | 1100                |

| D26.0          | 000        | 11010          | 010110           | 1011              | 010110           | 0100              | D3.3           | 011        | 00011          | 110001           | 1100              | 110001           | 0011                |

| D27.0          | 000        | 11011          | 110110           | 0100              | 001001           | 1011              | D4.3<br>D5,3   | 011<br>011 | 00100<br>00101 | 110101<br>101001 | 0011<br>1100      | 001010<br>101001 | 1100                |

| D28.0<br>D29.0 | 000        | 11100<br>11101 | 001110<br>101110 | 1011<br>0100      | 001110<br>010001 | 0100<br>1011      | D6.3           | 011        | 00110          | 011001           | 1100              | 011001           | 0011                |

| D30.0          | 000        | 11110          | 011110           | 0100              | 100001           | 1011              | D7.3           | 011        | 00111          | 111000           | 1100              | 000111           | 0011                |

| D31.0          | 000        | 11111          | 101011           | 0100              | 010100           | 1011              | 08.3           | 011        | 01000          | 111001           | 0011              | 000110           | 1100                |

| D0.1           | 001        | 00000          | 100111           | 1001              | 011000           | 1001              | D9.3           | 011        | 01001          | 100101           | 1100              | 100101           | 0011                |

| D1.1           | 001        | 00001          | 011101           | 1001              | 10001D           | 1001              | D10.3          | 011        | D1010          | 010101           | 1100              | 010101           | 0011                |

| D2.1           | 001        | 00010          | 101101           | 1001              | 010010           | 1001              | D11.3          | 011        | D1011          | 110100           | 1100              | 110100           | 0011                |

| 03.1           | 001<br>001 | 00011          | 110001           | 1001<br>1001      | 110001           | 1001              | D12.3<br>D13.3 | 011<br>011 | 01100<br>01101 | 001101<br>101100 | 1100<br>1100      | 001101<br>101100 | 0011<br>0011        |

| D4.1<br>D5.1   | 001        | 00100<br>00101 | 110101<br>101001 | 1001              | 001010<br>101001 | 1001<br>1001      | D14.3          | 011        | 01110          | 011100           | 1100              | 011100           | 0011                |

| D6.1           | 001        | 00110          | 011001           | 1001              | 011001           | 1001              | D15.3          | 011        | 01111          | 010111           | 0011              | 101000           | 1100                |

| 07.1           | 001        | 00111          | 111000           | 1001              | 000111           | 1001              | D16.3          | 011        | 10000          | 011011           | 0011              | 100100           | 1100                |

| D8.1           | 001        | 01000          | 111001           | 1001              | 000110           | 1001              | D17.3          | 011        | 10001          | 100011           | 1100              | 100011           | 0011                |

| D9.1           | 001        | 01001          | 100101           | 1001              | 100101           | 1001              | D18.3          | 011        | 10010          | 010011           | 1100              | 010011           | 0011                |

| D10.1          | 001        | 01010          | 010101           | 1001              | 010101           | 1001              | D19.3          | 011        | 10011          | 110010<br>001011 | 1100              | 110010           | 0011                |

| D11.1<br>D12.1 | 001<br>001 | 01011<br>01100 | 110100<br>001101 | 1001<br>1001      | 110100<br>001101 | 1001<br>1001      | D20.3<br>D21.3 | 011<br>011 | 10100<br>10101 | 101010           | 1100<br>1100      | 001011<br>101010 | 0011<br>0011        |

| D13.1          | 001        | 01101          | 101100           | 1001              | 101100           | 1001              | D22.3          | 011        | 10110          | 011010           | 1100              | 011010           | 0011                |

| D14.1          | 001        | 01110          | 011100           | 1001              | 011100           | 1001              | D23.3          | 011        | 10111          | 111010           | 0011              | 000101           | 1100                |

| D15.1          | 001        | 01111          | 010111           | 1001              | 101000           | 1001              | D24.3          | 011        | 11000          | 110011           | 0011              | 001100           | 1100                |

| D16.1          | 001        | 10000          | 011011           | 1001              | 100100           | 1001              | D25.3          | 011        | 11001          | 100110           | 1100              | 100110           | 0011                |

| D17.1          | 001        | 10001          | 100011           | 1001              | 100011           | 1001              | D26.3          | 011        | 11010          | 010110           | 1100              | 010110           | 0011                |

| D18.1          | 001<br>001 | 10010<br>10011 | 010011           | 1001<br>1001      | 010011           | 1001<br>1001      | D27.3<br>D28.3 | 011<br>011 | 11011<br>11100 | 110110           | 0011<br>1100      | 001001<br>001110 | 1100                |

| D19.1<br>D20.1 | 001        | 10100          | 110010<br>001011 | 1001              | 110010<br>001011 | 1001              | D29.3          | ăii        | 11101          | 101110           | 0011              | 010001           | 1100                |

| D21.1          | 001        | 10101          | 101010           | 1001              | 101010           | 1001              | D30.3          | 011        | 11110          | 011110           | 0011              | 100001           | 1100                |

| D22.1          | 001        | 10110          | 011010           | 1001              | 011010           | 1001              | D31.3          | 011        | 11111          | 101011           | 0011              | 010100           | 1100                |

| D23.1          | 001        | 10111          | 111010           | 1001              | 000101           | 1001              | D0:4           | 100        | 00000          | 100111           | 0010              | 011000           | 1101                |

| 024.1          | 001        | 11000          | 110011           | 1001              | 001100           | 1001              | D1.4           | 100        | 00001          | 011101           | 0010              | 100010           | 1101                |

| 025.1          | 001        | 11001          | 100110           | 1001              | 100110           | 1001              | D2.4           | 100        | 00010          | 101101           | 0010              | 010010           | 1101                |

| 026.1          | 001        | 11010          | 010110           | 1001              | 010110           | 1001              | D3.4<br>D4.4   | 100<br>100 | 00011<br>00100 | 110001           | 1101<br>0010      | 110001<br>001010 | 0010                |

| D27.1<br>D28.1 | 001<br>001 | 11011          | 110110<br>001110 | 1001              | 001001           | 1001<br>1001      | D4.4<br>D5.4   | 100        | 00100          | 101001           | 1101              | 101001           | 1101<br>0010        |

| D29.1          | 001        | 13101          | 101110           | 1001              | Q01110<br>Q10001 | 1001              | D6.4           | 100        | 00110          | 011001           | 1101              | 011001           | 0010                |

| D30.1          | 001        | 11110          | 011110           | 1001              | 100001           | 1001              | D7.4           | 100        | 00111          | 111000           | 1101              | 000111           | 0010                |

| D31.1          | 001        | 11111          | 101011           | 1001              | 010100           | 1001              | D8.4           | 100        | 01000          | 111001           | 0010              | 000110           | 1101                |

| D0.2           | 010        | 00000          | 100111           | 0101              | 011000           | <b>0101</b>       | D9.4           | 100        | 01001          | 100101           | 1101              | 100101           | 0010                |

| D1.2           | 010        | 00001          | 011101           | 0101              | 100010           | 0101              | D10.4          | 100        | 01010          | 010101           | 1101              | 010101           | 0010                |

| D2.2           | 010        | 00010          | 101101           | 0101              | 010010           | 0101              | D11.4          | 100        | 01011          | 110100           | 1101              | 110100           | 0010                |

| D3.2           | 010        | 00011          | 110001           | 0101              | 110001           | 0101              | D12.4          | 100        | 01100          | 001101           | 1101              | 001101           | 0010                |

| D4.2           | 010        | 00100          | 110101           | 0101              | 001010           | 0101              | D13.4          | 100        | 01101          | 101100           | 1101              | 101100           | 0010                |

| D5.2<br>D6.2   | 010<br>010 | 00101<br>00110 | 101001<br>011001 | 0101<br>0101      | 101001           | 0101<br>0101      | D14.4<br>D15.4 | 100<br>100 | 01110<br>01111 | 011100<br>010111 | 1101<br>0010      | 011100<br>101000 | 0010<br>1101        |

| D6.2<br>D7.2   | 010        | 00110          | 111000           | 0101              | 011001<br>000111 | Q101<br>Q101      | D16.4          | 100        | 10000          | 011011           | 0010              | 100100           | 1101                |

|                | WIN.       | 01000          | 22.12000         | - P (V)           | <b> </b>         | acade0886153838   | D17.4          | 100        | 10001          | 100011           | 1101              | 100011           | 49 99 100 100 100 1 |

Table 1. Valid Data Characters – Encoding (cont.)

| Data<br>Byla   |            | Bits           | Current          | RD-               | Current          | RD+               |

|----------------|------------|----------------|------------------|-------------------|------------------|-------------------|

| Name<br>Name   | HGF        | EDCBA 7        | abodei           | fghj <sup>2</sup> | abedai           | fyhj <sup>2</sup> |

| 018.4          | 100        | 10010          | 010011           | 1101              | 010011           | 0010              |

| 319.4          | 100        | 10011          | 110010           | 1101              | 110010           | 0010              |

| 20.4           | 100        | 10100<br>10101 | 001011           | 1101              | 001011<br>101010 | 0010<br>0010      |

| D21.4<br>D22.4 | 100<br>100 | 10110          | 101010<br>011010 | 1101              | 011010           | 0010              |

| 023.4          | 100        | 10111          | 111010           | 0010              | 000101           | 1101              |

| 024.4          | 100        | 11000          | 110011           | 0010              | 001100           | 1101              |

| 025.4<br>026.4 | 100<br>100 | 11001<br>11010 | 100110           | 1101<br>1101      | 100110           | 0010<br>0010      |

| D27.4          | 100        | 11011          | 110110           | 0010              | 001001           | 1101              |

| 026.4          | 100        | 11100          | 001110           | 1101              | 001110           | 0010              |

| 029.4          | 100        | 11101          | 101110<br>011110 | 0010<br>0010      | 010001           | 1101<br>1101      |

| D30.4<br>D31.4 | 100<br>100 | 11110<br>11111 | 101011           | 0010              | 010100           | 1101              |

| D0.5           | 101        | 00000          | 100111           | 1010              | 011000           | 1010              |

| D1.5           | 101        | 00001          | 011101           | 1010              | 100010           | 1010              |

| D2.5<br>D3.5   | 101<br>101 | 00010<br>00011 | 101101<br>110001 | 1010<br>1010      | 010010<br>110001 | 1010<br>1010      |

| D3.5<br>D4.5   | 101        | 00100          | 110101           | 1010              | 001010           | 1010              |

| D5.5           | 101        | 00101          | 101001           | 1010              | 101001           | 1010              |

| D6.5           | 101<br>101 | 00110          | 011001<br>111000 | 1010              | 011001<br>000111 | 1010<br>1010      |

| D7.5<br>D8.5   | 101        | 00111<br>01000 | 111000           | 1010<br>1010      | 000111           | 1010              |

| D9.5           | 101        | 01001          | 100101           | 1010              | 100101           | 1010              |

| 010.5          | 101        | 01010          | 010101           | 1010              | 010101           | 1010              |

| D11.5<br>D12.5 | 101<br>101 | 01011<br>01100 | 110100<br>001101 | 1010<br>1010      | 110100<br>001101 | 1010              |

| 013.5          | 101        | 01101          | 101100           | 1010              | 101100           | 1010              |

| Q14.5          | 101        | 01110          | 011100           | 1010              | 011100           | 1010              |

| D15.5<br>D16.5 | 101<br>101 | 01111          | 010111           | 1010<br>1010      | 101000<br>100100 | 1010<br>1010      |

| D17.5          | 101        | 10001          | 100011           | 1010              | 100011           | 1010              |

| D18.5          | 101        | 10010          | 010011           | 1010              | 010011           | 1010              |

| 019.5          | 101        | 10011          | 110010           | 1010              | 110010           | 1010              |

| D20.5<br>D21.5 | 101<br>101 | 10100<br>10101 | 001011<br>101010 | 1010<br>1010      | 001011<br>101010 | 1010<br>1010      |

| D22.5          | 101        | 10110          | 011010           | 1010              | 011010           | 1010              |

| D23.6          | 101        | 10111          | 111010           | 1010              | 000101           | 1010              |

| D24.5          | 101<br>101 | 11000<br>11001 | 110011           | 1010<br>1010      | 001100<br>100110 | 1010              |

| D25.5<br>D26.5 | 101        | 11010          | 010110           | 1010              | 010110           | 1010              |

| D27.5          | 101        | 11011          | 110110           | 1010              | 001001           | 1010              |

| D28.5          | 101        | 11100          | 101110           | 1010<br>1010      | 001110<br>010001 | 1010<br>1010      |

| D29.5<br>D30.5 | 101<br>101 | 11101<br>11110 | 011110           | 1010              | 100001           | 1010              |

| D31.5          | 101        | 11111          | 101011           | 1010              | 010100           | 1010              |

| 3.0G           | 118        | 00000          | 100111           | 0110              | 011000           | 0110              |

| D1.6<br>D2.6   | 118<br>110 | 00001<br>00010 | 011101           | 0110<br>0110      | 100010           | 0110<br>0130      |

| 03.6           | 110        | 00011          | 110001           | 0110              | 110001           | 0110              |

| 04.6           | 110        | 00100          | 110101           | 0110              | 001010           | 0110              |

| D5.6           | 110<br>110 | 00101<br>00110 | 101001<br>011001 | 0110<br>0110      | 101001<br>011001 | 0110              |

| D6.6<br>D7.6   | 110        | 00110          | 111000           | 0110              | 000111           | 0110              |

| 08.6           | 110        | 01000<br>01001 | 111001           | 0110              | 000110           | 0110              |

| D9.6           | 110        | 01001          | 100101           | 0110              | 100101<br>010101 | 0110              |

| 010.6<br>D11.6 | 110<br>110 | 01010<br>01011 | 010101           | 0110<br>0110      | 110100           | 0110              |

| D12.6          | 110        | 01100          | 001101           | 0110              | 001101           | 0110              |

| D13.6          | 110        | 01101          | 101100           | 0110              | 101100           | 011(              |

| D14.6<br>D15.6 | 110<br>110 | 01110<br>01111 | 011100<br>010111 | 011D<br>011D      | 011100<br>101000 | 0110<br>0110      |

| D16.6          | 110        | 10000          | 011011           | 0110              | 100100           | 0110              |

| D17.6          | 110        | 10001          | 100011           | 0110              | 100011           | 0110              |

| D18.6          | 110        | 10010          | 010011           | 0110              | 010011           | 0110              |

| D19.6<br>D20.6 | 110<br>110 | 10011<br>10100 | 110010<br>001011 | 0110<br>0110      | 110010<br>001011 | 0110<br>0110      |

| 021.6          | 110        | 10101          | 101010           | 0110              | 101010           | 0110              |

| D22.6          | 110        | 10110          | 011010           | 0110              | 011010           | 0110              |

| D23.6          | 110        | 10111          | 111010           | 0110              | 000101           | 0110              |

| D24.6<br>D25.6 | 110<br>110 | 11000<br>11001 | 10011            | 0110<br>0110      | 100110           | 0110<br>0110      |

| D26.6          | 110        | 11010          | 010110           | 0110              | 010110           | 0110              |

| Data         |       | Nis                       | Cerrent | RD -              | Gurrent | RD+    |

|--------------|-------|---------------------------|---------|-------------------|---------|--------|

| Byte<br>Name | HGF   | HTS<br>EDCBA <sup>1</sup> | abodei  | fghj <sup>2</sup> | abedel  | lghj 2 |

| D27.6        | 110   | 11011                     | 110110  | 0110              | 001001  | 0110   |

| D28.6        | 110   | 11100                     | 001110  | 0110              | 001110  | 0110   |

| D29.6        | 110   | 11101                     | 101110  | 0110              | 010001  | 0110   |

| D30.6        | 110   | 11110                     | 011110  | 0110              | 100001  | 0110   |

| D31.6        | 110   | 11111                     | 101011  | 0110              | 010100  | 0110   |

| D0.7         | 111   | 00000                     | 100111  | 0001              | 011000  | 1110   |

| D1.7         | 111   | 00001                     | 011101  | 0001              | 100010  | 1110   |

| D2.7         | 111   | 00010                     | 101101  | 0001              | 010010  | 1110   |

| D3.7         | 111   | 00011                     | 110001  | 1110              | 110001  | 0001   |

| D4.7         | 111   | 00100                     | 110101  | 0001              | 001010  | 1110   |

| D5.7         | 111   | 00101                     | 101001  | 1110              | 101001  | 0001   |

| D6.7         | 111   | 00110                     | 011001  | 1110              | 011001  | 0001   |

| D7.7         | 111   | 00111                     | 111000  | 1110              | 000111  | 0001   |

| D8.7         | 111   | 01000                     | 111001  | 0001              | 000110  | 1110   |

| D9.7         | 111   | 01001                     | 100101  | 1110              | 100101  | 0001   |

| D10.7        | 111   | 01010                     | 010101  | 1110              | 010101  | 0001   |

| 011.7        | 111   | 01011                     | 110100  | 1110              | 110100  | 1000   |

| D12.7        | 111   | 01100                     | 001101  | 1110              | 001101  | 0001   |

| D13.7        | 111   | 01101                     | 101100  | 1110              | 101100  | 1000   |

| D14.7        | 111   | 01110                     | 011100  | 1110              | 011100  | 1000   |

| D15.7        | 111   | 01111                     | 010111  | 0001              | 101000  | 1110   |

| D16.7        | 111   | 10000                     | 011011  | 0001              | 100100  | 1110   |

| D17.7        | 111   | 10001                     | 100011  | 0111              | 100011  | 0001   |

| D18.7        | 111   | 10010                     | 010011  | 0111              | 010011  | 0001   |

| D19.7        | 111   | 10011                     | 110010  | 1110              | 110010  | 0001   |

| D20.7        | 111   | 10100                     | 001011  | 0111              | 001011  | 0001   |

| D21.7        | 111   | 10101                     | 101010  | 1110              | 101010  | 0001   |

| 022.7        | 111   | 10110                     | 011010  | 1110              | 011010  | 0001   |

| D23.7        | * 111 | 10111                     | 111010  | 0001              | 000101  | 7110   |

| D24.7        | 111   | 11000                     | 110011  | 0001              | 001100  | 1110   |

| D25.7        | 111   | 11001                     | 100110  | 1110              | 100110  | 0001   |

| D26.7        | 111   | 11010                     | 010110  | 1110              | 010110  | 0001   |

| 027.7        | 111   | 11011                     | 110110  | 0001              | 001001  | 1110   |

| D28.7        | 111   | 11100                     | 001110  | 1110              | 001110  | 0001   |

| D29.7        | 111   | 11101                     | 101110  | 0001              | 010001  | 1110   |

| D30.7        | 111   | 11110                     | 011110  | 0001              | 100001  | 1110   |

| D31.7        | 111   | 11111                     | 101011  | 0001              | 010100  | 1116   |

Table 2. Valid Special Characters - Encoding

| Special      | Curren | 11 <b>RO</b> –    | Curre  | nt RD+            |

|--------------|--------|-------------------|--------|-------------------|

| Code<br>Name | abcdei | fghj <sup>2</sup> | abcdel | fghj <sup>2</sup> |

| K28.0        | 001111 | 0100              | 110000 | 1011              |

| K28.1        | 001111 | 1001              | 110000 | 0110              |

| K28.2        | 001111 | 0101              | 110000 | 1010              |

| K28.3        | 001111 | 0011              | 110000 | 1100              |

| K28.4        | 001111 | 0010              | 110000 | 1101              |

| K28.5        | 001111 | 1010              | 110000 | 0101              |

| K28.6        | 001111 | 0110              | 110000 | 1001              |

| K28.7        | 001111 | 1000              | 110000 | 0111              |

| K23.7        | 111010 | 1000              | 000101 | 0111              |

| K27.7        | 110110 | 1000              | 001001 | 0111              |

| K29.7        | 101110 | 1000              | 010001 | 0111              |

| K30,7        | 011110 | 1000              | 100001 | 0111              |

NOTES: 1. "HGF EDCBA" correspond to Data Inputs CTXD7..0, in that order.

"a" is to be transmitted first, followed by "b", "c", ..., "j". "abcdeifghj", in that order, correspond to BTXD9... BTXD0.

Table 3. Ordered Set Encoding - Fiber Channel

|                     | 0.000.000 |        |     | U1  | HINGHAUG C  | Signals ( Mod                   | ic, naw j                                                          |                                 |        |                                                                                                        |

|---------------------|-----------|--------|-----|-----|-------------|---------------------------------|--------------------------------------------------------------------|---------------------------------|--------|--------------------------------------------------------------------------------------------------------|

|                     |           |        |     | lnj | iuts ( CTxl | 070)                            |                                                                    |                                 |        | 87x D 90                                                                                               |

| Function            |           | Byte 1 |     |     |             | Byte 2                          | Byte 3                                                             | Byte 4                          | Begin. | Output (4 Encoded Bytes)                                                                               |

|                     | Cntl      | Sig    | SOF | EOF | Type        |                                 |                                                                    |                                 | RD     | Byte 1-Byte 2-Byte 3-Byte 4                                                                            |

| SOFn13              | 0         | 0      | 1   | 0   | 0001        | _1                              | _1                                                                 | _1                              | Neg    | (K28.5-021.5-023.1-023.1                                                                               |

| SOFn2               | 0         | 0      | . 1 | 0   | 0010        | _1                              | _1                                                                 | _1                              | Neg    | (K28.5-D21.5-D21.1-D21.1                                                                               |

| SOFn3               | 0         | 0      | 1   | 0   | 0011        | - 1                             | _1                                                                 | _1                              | Neg    | (K28.5-D21.5-D22.1-D22.                                                                                |

| SOFit               | 0         | 0      | 1   | 0   | 0101        | _1                              | _1                                                                 | 1                               | Neg    | (K28.5-D21.5-D23.2-D23.                                                                                |

| SOFI2               | 0         | 0      | 1   | 0   | 0110        | _1                              | _1                                                                 | _1                              | Neg    | (K28.5-D21.5-D21.2-D21.2                                                                               |

| SOFi3               | 0         | 0      | 1   | 0   | 0111        | _1                              |                                                                    | _1                              | Neg    | (K28.5-D21.5-D22.2-D22.2                                                                               |

| SOFc1               | 0         | 0      | 1   | 0   | 1101        | _1                              | _1                                                                 | _t                              | Neg    | (K28.5-D21.5-D23.0-D23.0                                                                               |

| SOF                 | 0         | 0      | 1   | 0   | 1000        | _1                              | _1                                                                 |                                 | Neg    | (K28.5-D21.5-D24.2-D24.2                                                                               |

| EOFn <sup>4,5</sup> | 0         | 0      | 0   | 1   | 0000        | _1                              | _1                                                                 | _1                              | Neg    | (K28.5-D21.4-D21.6-D21.6                                                                               |

|                     |           |        |     |     |             |                                 |                                                                    |                                 | Pos    | (K28.5-D21.5-D21.6-D21.0                                                                               |

| EOFt <sup>5</sup>   | 0         | D      | 0   | 1   | 0100        | _1                              | _1                                                                 | _1                              | Neg    | (K28.5-D21.4-D21.3-D21.3                                                                               |

|                     |           |        |     |     |             |                                 |                                                                    |                                 | Pos    | (K28.5-D21.5-D21.3-D21.3                                                                               |

| EOFdt <sup>6</sup>  | 0         | 0      | 0   | 1   | 1100        | _1                              | _1                                                                 | _1                              | Neg    | (K28.5-D21.4-D21.4-D21.                                                                                |

|                     |           |        |     |     |             |                                 |                                                                    | <del></del>                     | Pos    | (K28.5-D21.5-D21.4-D21.4                                                                               |

| EOFa                | 0         | 0      | 0   | 1   | 1001        | 1                               | _1                                                                 | 1                               | Neg    | (K28.5-D21.4-D21.7-D21.7                                                                               |

|                     |           |        |     |     |             |                                 | _                                                                  |                                 | Pos    | (K28.5-D21.5-D21.7-D21.7                                                                               |

| EOFni               | 0         | 0      | 0   | 1   | 0001        | 1                               | 1                                                                  | 1                               | Nea    | (K28.5-D10.4-D21.6-D21.6                                                                               |

|                     |           |        |     |     |             |                                 |                                                                    |                                 | Pos    | (K28.5-D10.5-D21.6-D21.6                                                                               |

| EOFdti              | 0         | 0      | 0   | 1   | 1101        | _1                              | _1                                                                 | _1                              | Neg    | (K28.5-D10.4-D21.4-D21.4                                                                               |

|                     |           |        |     |     |             | <u> </u>                        |                                                                    |                                 | Pos    | (K28.5-D10.5-D21.4-D21.4                                                                               |

| ldle                | 0         | 1      | 0   | 0   | 0000        | _1                              | 1                                                                  | 1                               | Neg    | (K28.5-D21.4-D21.5-D21.9                                                                               |

| R-Rdy               | 0         | 1      | 0   | 0   | 0110        | 71                              | ī                                                                  | _1                              | Nea    | (K28.5-D21.4-D10.2-D10.2                                                                               |

| NOS                 | 0         | 1      | 0   | 0   | 1000        |                                 | 1                                                                  | 71                              | Nea    | (K28.5-D21.2-D31.5-D5.2                                                                                |

| OLS                 | 0         | 1      | 0   | 0   | 1001        |                                 | -1                                                                 | ٦,                              | Neg    | (K28.5-D21.1-D10.4-D21.2                                                                               |

| LR                  | 0         | 4      | 0   | 0   | 1010        | _i                              | _1                                                                 |                                 | Neg    | (K28.5-D9.2-D31.5-D9.2)                                                                                |

| LRR                 | 0         | 1      | 0   | 0   | 1011        | 7                               | 71                                                                 |                                 | Neg    | (K28.5-D21.1-D31.5-D9.2                                                                                |

| Undefined           | 1         | 0      | 0   | 0   | 0000        | (XY <sub>P</sub> ) <sup>2</sup> | (XY <sub>C</sub> ) <sup>2</sup>                                    | (XY <sub>D</sub> ) <sup>2</sup> |        | (K28.0-DX.Y <sub>B</sub> -DX.Y <sub>C</sub> -DX.Y                                                      |

| Undefined           | 1         | 0      | 0   | 0   | 0001        | (XY <sub>E</sub> ) <sup>2</sup> | (XY <sub>C</sub> ) <sup>2</sup>                                    | (XY <sub>D</sub> ) <sup>2</sup> |        | (K28.1-DX.Y <sub>8</sub> -DX.Y <sub>C</sub> -DX.Y                                                      |

| Undefined           | 1         | 0      | 0   | 0   | 0010        | (XY)2                           | (XY <sub>C</sub> ) <sup>2</sup>                                    | (XY <sub>D</sub> ) <sup>2</sup> |        | (K28.2-DX.Y <sub>B</sub> -DX.Y <sub>C</sub> -DX.Y                                                      |

| Undefined           | 1         | 0      | 0   | 0   | 0011        | (XY <sub>P</sub> ) <sup>2</sup> | (XY <sub>C</sub> ) <sup>2</sup>                                    | (XY <sub>D</sub> ) <sup>2</sup> |        | (K28.3-DX.Y <sub>B</sub> -DX.Y <sub>C</sub> -DX.Y                                                      |

| Undefined           | 1         | 0      | 0   | 0   | 0100        | (XY <sub>B</sub> ) <sup>2</sup> | (XY <sub>C</sub> ) <sup>2</sup>                                    | $(XY_0)^2$                      |        | (K28.4-DX.Y <sub>B</sub> -DX.Y <sub>C</sub> -DX.Y                                                      |

| Undefined           | 1         | Ō      | 0   | 0   | 0101        | (XY <sub>B</sub> ) <sup>2</sup> | (XY <sub>C</sub> ) <sup>2</sup>                                    | (XY <sub>D</sub> ) <sup>2</sup> |        | (K28.5-DX.Y <sub>B</sub> -DX.Y <sub>C</sub> -DX.Y                                                      |

| Undefined           | 1         | 0      | 0   | 0   | 0110        | (XY <sub>B</sub> ) <sup>2</sup> | (XXC) <sub>5</sub>                                                 | (XY <sub>D</sub> ) <sup>2</sup> |        | (K28.6-DX.Y <sub>B</sub> -DX.Y <sub>C</sub> -DX.Y                                                      |

| Undefined           | 1         | 0      | 0   | 0   | 0111        | (XY <sub>R</sub> ) <sup>2</sup> | (XYC)2                                                             | (XY <sub>D</sub> ) <sup>2</sup> |        | (K28.7-DX.Y <sub>B</sub> -DX.Y <sub>C</sub> -DX.Y                                                      |

| Undefined           | 1         | 0      | 0   | 0   | 1000        | (XY <sub>B</sub> ) <sup>2</sup> | (XY <sub>C</sub> ) <sup>2</sup>                                    | (XY <sub>O</sub> ) <sup>2</sup> |        | 932/304/32/32/32/304/30/30/30/30/30/30/30/30/30/30/30/30/30/                                           |

| Undefined           | 1         | 0      | 0   | 0   | 1001        | (XY <sub>B</sub> ) <sup>2</sup> | (XY <sub>c</sub> ) <sup>2</sup>                                    | (XY <sub>D</sub> ) <sup>2</sup> |        | (K23.7-DX.Y <sub>B</sub> -DX.Y <sub>C</sub> -DX.Y                                                      |

| Undefined           | 1         | 0      | 0   | 0   | 1010        | (XY <sub>B</sub> ) <sup>2</sup> | 200000000000000000000000000000000000000                            | v                               |        | (K27.7-DX.Y <sub>B</sub> -DX.Y <sub>C</sub> -DX.Y                                                      |

| Undefined           | 1         | 0      | 0   | 0   | 1011        | (XY <sub>B</sub> ) <sup>2</sup> | (XY <sub>C</sub> ) <sup>2</sup><br>(XY <sub>C</sub> ) <sup>2</sup> | (XY <sub>D</sub> ) <sub>S</sub> |        | (K29.7-DX.Y <sub>B</sub> -DX.Y <sub>C</sub> -DX.Y<br>(K30.7-DX.Y <sub>B</sub> -DX.Y <sub>C</sub> -DX.Y |

NOTES:

2-56

<sup>1.</sup> Don't care (any value).

<sup>2.</sup> Outputs for the data characters in the ordered set must be encoded to the correct data values.

<sup>3.</sup> SOF - Start-of-frame delimiter

<sup>4.</sup> EOF - End-of-frame delimiter

<sup>5.</sup> Encoded as EOFni if TERR or PERR = 1

#### Decode

The Decode block of the GA9103 is in the return path of a serial link from a remote transmitter to the host. It takes the encoded 10-bit data from the GA9102 (Rx) and decodes it into 8-bit data for the host. The 10-bit-wide input, BRXD0..9, is first clocked into the REGISTER, using the Receiver byte clock. RXCLK.

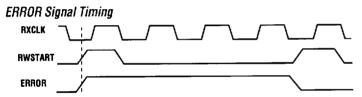

The 10b/8b DECODER decodes data and special characters according to Tables 1 and 2. Initially, the current Running Disparity is negative and each of the characters are decoded based on the received character. The DECODER also checks for the validity of received characters based on Tables 1 and 2. The FRROR flag is set if there are code violations in any one of the four bytes of the word, or if the running disparity is in error. The ERROR signal is active for the entire duration of the word transmission. regardless of which byte was in error. The ERROR pin is also used to flag three other invalid conditions which may occur: 1) when a special character is detected in the second, third, or fourth character of a transmission

word, 2) if SYNC = 1 when BRXD0..9 is not a K28.5, and 3) when an ordered set is received with improper beginning running disparity. Examples of improper running disparity are:

1) SOF with positive running disparity, and 2) EOF content specified for positive running disparity, but received with BRD-. (See Table 4)

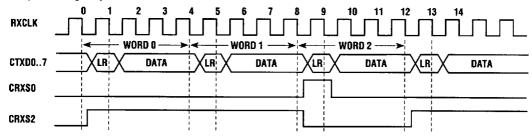

Four bytes of the received signal must be analyzed in order to perform the ORDERED SFT DECODE. For the purpose of ordered set decoding, the SYNC signal is used to align the four bytes of information to generate a word. The ordered sets are decoded according to Table 4 (Ordered Set Decoding). The ORDERED SET DECODE block generates the Data/Ordered Set signal, CRXSO, along with the 8-bit decoded ordered set. The RWSTART signal is also generated from this block. The SYNC signal is used to generate a periodic signal, RWSTART, which is HIGH on the first byte output, CRXD0..7, of every word. RWSTART is initialized by RESETN, RAWRX. or if K28.5 is followed by three valid data bytes (DX.YA, DX.YB, and DX.YC). The relationship between ERROR, RXCLK, and RWSTART is shown in the figure above.

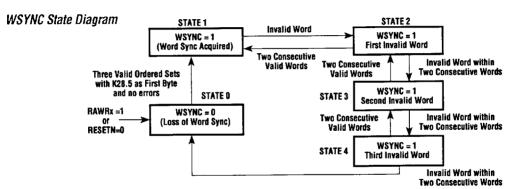

The WSYNC signal from the ORDERED SET DECODE block is used to denote whether or not the link is word-synchronized. As shown in the WSYNC State Diagram below, WSYNC = 0 under the following conditions: if the link loses word synchronization, is in a reset condition, or in the "RAW" mode. The link achieves word synchronization, (WSYNC = 1), only after three valid ordered sets are received without error and the first byte is a K28.5 character. Once synchronized, the link could lose synchronization if it receives a minimum of four invalid words within a

Figure 5. Data Fields for Fiber Channel Ordered Set Decoding

consecutive set of seven words as per the sequence shown in the State Diagram. During this sequence, the link can reacquire word synchronization (State 1) if it receives two consecutive valid words in each of the States as shown in the State Diagram. If RAWRx = 1. WSYNC = 0.

If the ordered sets received correspond to a primitive sequence, the LINE STATE DECODER increments a counter using the SYNC signal. The primitive sequences, as defined by the Fiber Channel standard, are

#### MUX Selection Table

| RAW Rx | GRXS2 CR | XSO MUX Output          |

|--------|----------|-------------------------|

| Ω      | ο ι      | Decoded Data            |

| n      | ο,       | Ordered set/line state  |

| A      | 1 (      | Decoded line state word |

| 1      | n ,      | C Undecoded data*       |

\*CRXSO is part of this data

Offline State (OLS), Not-Operational State (NOS), Link Reset (LR), and Link Reset Response (LRR). These are transmitted to indicate a specific condition within a port. Transmission of NOS indicates the port has detected a link failure condition. OLS indicates the port is preparing to either initialize, to go into the diagnostic mode, or to power down. LR is sent after a link timeout error has occurred or OLS is received. LRR is transmitted to recognize Link Reset. If three consecutive ordered sets are received, the corresponding information is sent through CRXD0..7. according to the Ordered Set Decoding table. CRXS2 is active as long as one of the four possible line state signals, (OLS, NOS, LR, and LRR), is being received. Once active, CRXS2 remains active for the count of two line state ordered sets. On the third count, CRXS2 goes inactive and CRXS0 goes active. The proper line state output signals are flagged on CRXD0..7, as per Table 4. The figure below shows an

example timing sequence for line states when RAWRx = 0.

The fields within the first byte, CRXD0..7. of the word for Ordered Set Decoding are shown in Figure 5. CRXD7 corresponds to the Cntl signal which, when logic LOW, indicates the Fiber Channel-defined ordered set has been received. When the Cntl signal is HIGH, it indicates a non-Fiber Channel (undefined) ordered set has been received. The **Sig** signal (CRXD6). when HIGH, indicates the Line State ordered set, IDLE or R\_RDY, has been received, and when LOW, the Sig signal indicates an ordered set other than Line State has been received. **SOF** (CRXD5). when HIGH, indicates the Start-of-Frame ordered set has been received and EOF (CRXD4), when HIGH, indicates the Endof-Frame ordered set. Type (CRXD3..0) indicates the different types of ordered sets within the SOF, EOF, Line State and Undefined categories.

The CRC CHECK block performs a 32-bit Cyclic Redundancy Check on the received data. The CRC check begins after the Start-of-Frame Detect and finishes prior to End-of-Frame. CRC errors are flagged at the CRXS1 pin if RAWRx = 1 and CRXS1 = 0.

The RAW Rx mode is used whenever the 10-bit-wide input data to the receiver is to be passed through, undecoded, to the receive outputs, CRXD0..7, CRXP, and CRXS0. The MUX is used to choose between the decoded data/ordered set and the register output. When the RAWRx input signal is active, the undecoded data/ordered set/line state is chosen.

If CRXS2 and CRXS0 are LOW, decoded data output is selected through the MUX. If CRXS0 is HIGH and CRXS2 is LOW, the ordered set/line state is selected. If CRXS2 goes HIGH, the MUX output is disabled (that is, the output data is ignored). The selection table for the MUX is shown above.

The PARITY GENERATE block is used to generate the odd parity signal CRXP for every byte of data, CRXD0..7 and CRXS0. If the number of ones in the output, CRXD0..7 and CRXS0, is an even number, CRXP will be HIGH. If the number of ones in the output, CRXD0..7 and CRXS0, is odd. CRXP will be LOW.

#### **Example Timing Sequence for Line States**

Table 4. Ordered Set Decoding - Fiber Channel

|                                                                               |      |     |            | C-Inti | ertace Signa | ls ( Mode: R        | aw)                 |                     |                     |

|-------------------------------------------------------------------------------|------|-----|------------|--------|--------------|---------------------|---------------------|---------------------|---------------------|

| Ax                                                                            |      |     |            | Outp   | uts ( CAXD7  | 0)                  |                     |                     |                     |

| In <del>pu</del> t                                                            |      | Byt | <b>8</b> 1 |        |              | Byte                | 12                  | Byte 3              | Byte 4              |

|                                                                               | Gntl | Sig | SOF        | EOF    | Type         | BR <sub>D</sub> -2  | BRo+ <sup>3</sup>   |                     |                     |

| SOFn1                                                                         | 0    | 0   | 1          | 0      | 0001         |                     | (B5 <sub>16</sub> ) | (37 <sub>16</sub> ) | (37 <sub>16</sub> ) |

| SOFn2                                                                         | 0    | 0   | 1          | 0      | 0010         |                     | (85 <sub>16</sub> ) | (35 <sub>16</sub> ) | (35 <sub>16</sub> ) |

| SOFn3                                                                         | 0    | 0   | • •        | 0      | 0011         |                     | (B5 <sub>16</sub> ) | (36 <sub>16</sub> ) | (36 <sub>16</sub> ) |

| SOFi1                                                                         | 0    | 0   | 1          | 0      | 0101         |                     | (85 <sub>16</sub> ) | (57 <sub>16</sub> ) | (57 <sub>16</sub> ) |

| SOFi2                                                                         | 0    | 0   | 1          | 0      | 0110         |                     | (B5 <sub>16</sub> ) | (55 <sub>16</sub> ) | (55 <sub>16</sub> ) |

| SOF(3                                                                         | 0    | 0   | 1          | -0     | 0111         |                     | (B5 <sub>16</sub> ) | (56 <sub>16</sub> ) | (56 <sub>16</sub> ) |

| SOFc1                                                                         | 0    | 0   | 1          | O      | 1101         |                     | (B5 <sub>16</sub> ) | (17 <sub>16</sub> ) | (17 <sub>16</sub> ) |

| SOFI                                                                          | 0    | 0   | 1          | 0      | 1000         |                     | (85 <sub>16</sub> ) | (58 <sub>16</sub> ) | (58 <sub>16</sub> ) |

| EOFn                                                                          | 0    | 0   | 0          | 1      | 0000         | (95 <sub>16</sub> ) | (B5 <sub>16</sub> ) | (D5 <sub>16</sub> ) | (D5 <sub>16</sub>   |

| EOFI                                                                          | 0    | 0   | 0          | 1      | 0100         | (95 <sub>16</sub> ) | (B5 <sub>16</sub> ) | (75 <sub>16</sub> ) | (75 <sub>16</sub> ) |

| EOFdt                                                                         | 0    | O   | 0          | 1      | 1100         | (95 <sub>16</sub> ) | (B5 <sub>16</sub> ) | (95 <sub>16</sub> ) | (95 <sub>16</sub> ) |

| EOFa                                                                          | 0    | 0   | 0          | 1      | 1001         | (95 <sub>16</sub> ) | (B5 <sub>16</sub> ) | (F5 <sub>16</sub> ) | (F5 <sub>16</sub>   |

| EOFni                                                                         | 0    | 0   | 0          | 1      | 0001         | (8A <sub>16</sub> ) | (AA <sub>16</sub> ) | (D5 <sub>16</sub> ) | (D5 <sub>16</sub>   |

| EOFdti                                                                        | Q    | 0   | 0          | 1      | 1101         | (8A <sub>16</sub> ) | (AA <sub>16</sub> ) | (95 <sub>16</sub> ) | (95 <sub>16</sub>   |

| ldie                                                                          | 0    | 1   | 0          | 0      | 000G         |                     | (95 <sub>16</sub> ) | (85 <sub>16</sub> ) | (B5 <sub>16</sub>   |

| R_Rdy                                                                         | 0    | 1   | 0          | 0      | 0110         |                     | (95 <sub>16</sub> ) | (4A <sub>16</sub> ) | (4A <sub>16</sub>   |

| NO\$                                                                          | 0    | 1   | 0          | 0      | 1000         |                     | (55 <sub>16</sub> ) | (BF <sub>16</sub> ) | (45 <sub>18</sub>   |

| OLS                                                                           | 0    | 1   | 0          | 0      | 1001         |                     | (35 <sub>16</sub> ) | (8A <sub>16</sub> ) | (55 <sub>16</sub>   |

| LR                                                                            | 0    | 1   | 0          | a      | 1010         |                     | (49 <sub>16</sub> ) | (BF <sub>16</sub> ) | (49 <sub>16</sub>   |

| LRR                                                                           | O    | 1   | 0          | 0      | 1011         |                     | (95 <sub>16</sub> ) | (BF <sub>16</sub> ) | (49 <sub>16</sub>   |

| (K28.0-DX.Y <sub>B</sub> -DX.Y <sub>C</sub> -DX.Y <sub>D</sub> )              | 1    | 0   | 0          | 0      | 0000         |                     | (XY <sub>B</sub> )  | (XY <sub>0</sub> )  | (XY <sub>D</sub>    |

| (K28.1-DX.Y <sub>B</sub> -DX.Y <sub>C</sub> -DX.Y <sub>D</sub> )              | 1    | 0   | 0          | 0      | 0001         |                     | (XY <sub>B</sub> )  | (XY <sub>C</sub> )  | (200                |

| (K28.2-DX.Y <sub>B</sub> -DX.Y <sub>C</sub> -DX.Y <sub>D</sub> )              | 1    | 0   | 0          | 0      | 0010         |                     | (XY <sub>B</sub> )  | (XY <sub>C</sub> )  | (XY <sub>D</sub>    |

| (K28.3-DX.Y <sub>B</sub> -DX.Y <sub>C</sub> -DX.Y <sub>D</sub> )              | 1    | 0   | 0          | 0      | 0011         |                     | (XY <sub>B</sub> )  | (XY <sub>C</sub> )  | (XY <sub>D</sub>    |

| (K28.4-DX.Y <sub>B</sub> -DX.Y <sub>C</sub> -DX.Y <sub>D</sub> )              | 1    | 0   | 0          | 0      | 0100         |                     | (XY <sub>B</sub> )  | (XY <sub>C</sub> )  | (XY <sub>D</sub>    |

| (K28.5-DX.Y <sub>B</sub> -DX.Y <sub>C</sub> -DX.Y <sub>D</sub> ) <sup>1</sup> | 1    | 0   | 0          | 0      | 0101         |                     | (XY <sub>B</sub> )  | (XY <sub>C</sub> )  | (XY <sub>C</sub>    |

| (K28.6-DX.Y <sub>B</sub> -DX.Y <sub>C</sub> -DX.Y <sub>D</sub> )              | 1    | Ø   | 0          | 0      | 0110         |                     | (XY <sub>B</sub> )  | (XY <sub>C</sub> )  | (XY <sub>E</sub>    |

| (K28.7-DX.Y <sub>B</sub> -DX.Y <sub>C</sub> -DX.Y <sub>D</sub> )              | 1    | 0   | 0          | 0      | 0111         |                     | (XY <sub>B</sub> )  | (XY <sub>C</sub> )  | (XY <sub>D</sub>    |

| (K23.7-DX.Y <sub>B</sub> -DX.Y <sub>C</sub> -DX.Y <sub>D</sub> )              | 1    | 0   | 0          | 0      | 1000         |                     | (XY <sub>B</sub> )  | (XY <sub>C</sub> )  | (XY <sub>C</sub>    |

| (K27.7-DX.Y <sub>B</sub> -DX.Y <sub>C</sub> -DX.Y <sub>D</sub> )              | 1    | 0   | 0          | 0      | 1001         |                     | (XY <sub>B</sub> )  | (XY <sub>C</sub> )  | (XY <sub>D</sub>    |

| (K29.7-DX.Y <sub>B</sub> -DX.Y <sub>C</sub> -DX.Y <sub>D</sub> )              | 1    | 0   | Ö          | 0      | 1010         |                     | (XY <sub>B</sub> )  | (XY <sub>c</sub> )  | (XY <sub>E</sub>    |

| (K30.7-DX.Y <sub>B</sub> -DX.Y <sub>C</sub> -DX.Y <sub>D</sub> )              | 1    | 0   | 0          | 0      | 1011         |                     | (XY <sub>B</sub> )  | (XY <sub>c</sub> )  | (XY <sub>C</sub>    |

NOTES: 1. Valid for any unrecognized control sequence starting with 'K28.5'. Not valid for acquiring Word Sync.

<sup>2.</sup> BRD - Beginning Running Disparity Negative.

<sup>3.</sup> BR<sub>D</sub> + Beginning Running Disparity Positive

#### System Block Diagram

#### Absolute Maximum Ratings

Exceeding the absolute maximum ratings may damage the device.

|   |   |    |    | 9  | ** |   | 3  |    |   | 2  | 2  |     |   |   |   |   |    |   | 3 | ÷ |  |  |   |  | 8 |    |   |   |    | 2  |    |   |    |     |    |    | 23  |   | *  |

|---|---|----|----|----|----|---|----|----|---|----|----|-----|---|---|---|---|----|---|---|---|--|--|---|--|---|----|---|---|----|----|----|---|----|-----|----|----|-----|---|----|

| į | S | Ų  | ď. | 4  | į, | ı | Ġ  | П  | p | e  | r. | 'n. | Ц | ı |   |   |    |   |   |   |  |  |   |  |   | Š. | ä |   | -  | טנ | ျ  |   | to | •   | ł  | K  | ۳(  | î |    |

|   | A | Ø. | b  | ie | 11 | ŧ | te | M  | Ŋ | 16 | ¥  | 2   | t | W | 0 |   |    |   |   |   |  |  | * |  |   |    |   |   | -{ | 15 | ٥( | 2 | to | 4   | 1  | 25 | ۰(  | 3 |    |

|   | S | ų  | ų  | H  |    | n | d  | ta | 9 | e  | ı  | Ø   | 9 | m | O | ш | 24 | ĺ |   |   |  |  |   |  |   |    |   |   | •  | 0. | 5  | ۷ | tc | ) . | +7 | £  | ٧   |   |    |

|   | D | C  | Ü  | 4  | Ш  | t | N  | ol | t | ų  | μ  |     |   |   |   |   |    |   |   |   |  |  |   |  |   |    |   | 0 | 5  | ١  | 1  | 0 | (V | c   | С  | +( | ),5 | ١ | 1) |

|   | D | C  | İ  | 4  | W  | İ | C  | u  | 7 | 81 | d  | ľ   |   |   |   |   |    |   |   |   |  |  |   |  |   |    |   |   | :  | Ю  | Ŋ  | V | 1  | 0   | +  | ì  | n/  | ١ |    |

#### **Operating Conditions**

Proper functionality is guaranteed under these conditions:

|  | S | ı | P | p | h |   | ĸ | ı | t | ų | K | •  |    |   |   |   |   |  |  |  |  |  |   |  |  |  |  | • | j   | V | ŧ | 5 | %  | Ď. |  |  |

|--|---|---|---|---|---|---|---|---|---|---|---|----|----|---|---|---|---|--|--|--|--|--|---|--|--|--|--|---|-----|---|---|---|----|----|--|--|

|  | ı | ı | n | H | e | Ħ | ľ | t | * | ų | þ | 81 | ra | t | U | ı | į |  |  |  |  |  | 8 |  |  |  |  | l | ) ( | 0 | 7 | 0 | ٥( | ,  |  |  |

#### DC Characteristics (Over operating range unless otherwise specified.)

|                  |                       | Lim                                                | its <sup>1</sup> |

|------------------|-----------------------|----------------------------------------------------|------------------|

| Symbol           | Description           | Test Conditions Min. Ty                            | p. Max. Unit     |

| Von              | Output HIGH voltage   | V <sub>CC</sub> = Min l <sub>OH</sub> = -4 mA 3.6  | ٧                |

|                  |                       | V <sub>IN</sub> = V <sub>H</sub> or V <sub>L</sub> |                  |

| V <sub>OL</sub>  | Output LOW voltage    | V <sub>CC</sub> = Min I <sub>OL</sub> = 4 mA       | 0.37 V           |

| 42000            |                       | $V_{IN}^3 = V_{IH} \text{ or } V_{IL}$             |                  |

| V <sub>H</sub> 2 | Input HIGH level      | Guaranteed input logical HIGH 2.0                  | ٧                |

|                  |                       | voltage for all inputs                             |                  |

| V <sub>L</sub> 2 | Input LOW level       | Guaranteed input logical LOW                       | 0.8 V            |

|                  |                       | voltage for all inputs                             |                  |

| l <u>l</u>       | Input Leakage current | $V_{CC} = Max$ $V_{IN} = 0.40 V$ -15               | 50 -400 µA       |

Notes: 1. Typical limits are:  $V_{CC} = 5.0 \text{ V}$  and  $T_A = 25^{\circ}C$ .

3. VIN, the TTL input, can be HIGH or LOW.

<sup>2.</sup> These are absolute values with respect to device ground, and all overshoots due to system or tester noise are included.

#### TTL Test Load, TLL Outputs

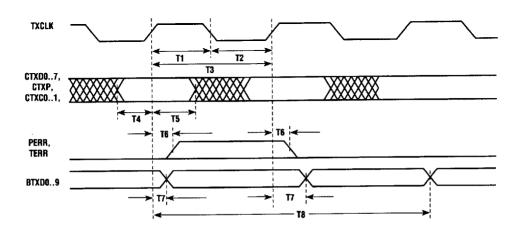

#### AC Characteristics - ENCODE

| Parameter | Description Min. Typ. Max. Unit           |

|-----------|-------------------------------------------|

| T1        | TXCLK Pulse Width HIGH 15.00 ns           |

| <b>T2</b> | TXCLK Pulse Width LOW 15:00 T3-T1 ns      |

| T3        | TXCLK Period 37.51 37.70 37.89 ns         |

| T4        | CTXD0.7; CTXP; CTXC0,1 Setup Time 2.00 ns |

| <b>T5</b> | CTXD0.7; CTXP; CTXC0,1 Hold Time 7.00 ns  |

| T6        | TXCLK ↑ to PERR, TERR 3.50 17.00 ns       |

| 17        | TXCLK † to BTXD09 5.00 19.00 ns           |

| T8        | ENCODE Latency 2*T3 +7 3*T3 +12 ns        |

#### **ENCODE Timing Diagram**

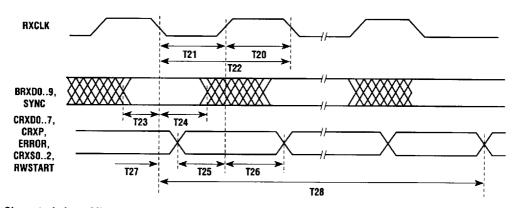

#### AC Characteristics - DECODE

| Parameter | Descriptian                                               | Min.        | Тур.  | Max.      | Unit |

|-----------|-----------------------------------------------------------|-------------|-------|-----------|------|

| T20       | RXCLK Pulse Width HIGH                                    | (T22/2) - 3 |       |           | ns   |

| T21       | RXCLK Pulse Width LOW                                     | (T22/2) - 3 |       |           | กร   |

| T22       | RXCLK Period                                              | 37.51       | 37.70 | 37.89     | пs   |

| T23       | BRXD09, SYNC Valid to RXCLK ¥                             | 1.00        |       |           | ns   |

| T24       | BRXD09, SYNC Valid from RXCLK ¥                           | 8.00        |       |           | ns   |

| T25       | CRXDO.7, CRXP, ERROR, CRXSO2, RWSTART Valid to RXCLK †    | 4.70        |       |           | ns   |

| T26       | CRXDO.7, CRXP, ERROR, CRXSO.2, RWSTART Valid from RXCLK † | 18.25       |       |           | ns   |

| T27       | CRXDO.7, CRXP, ERROR, CRXSO.2, RWSTAHT from RXCLK ₩       | 2.50        |       | 11.00     | ns   |

| T28       | DECODE Latency                                            | 6*T22       |       | 7*T22 +10 | ns   |

Note: The DECODE functional block clocks off the negative edge of RXCLK.

#### **DECODE Timing Diagram**

AC Characteristics - Miscellaneous

| Parameter | Description | Min. Typ. Max. L | Unit |

|-----------|-------------|------------------|------|

| T29 RES   |             | 10               | ns   |

#### **RESETN Timing Diagram**

Table 5. Pin Definitions

| Symbol   | <i>V</i> 0 | Quantity | Logic Level | Active | Description                                | Pin#                             |

|----------|------------|----------|-------------|--------|--------------------------------------------|----------------------------------|

| CRXD07   | Output     | 8        | ΠL          | HIGH   | Receive Data Output                        | 59-57, 55-51                     |

| CRXSO    | Output     | 1        | TTL         | HIGH   | Receive Control                            | 60                               |

| CRXS1    | Output     | 1        | TTL         | HIGH   | Receive CRC Error                          | 61                               |

| CRXS2    | Output     | 1        | ΠL          | HIGH   | Line State                                 | 62                               |

| BRXDO9   | Input      | 10       | ΠL          | HIGH   | Receive Data Input                         | 37-39, 41-43, 45-48              |

| RXCLK    | input      | 1        | ΠL          | HIGH   | Receive Byte Clock                         | 36                               |

| SYNC     | Imput      | 1        | ΠL          | HIGH   | Receive Byte Sync                          | 49                               |

| TXCLK    | Input      | 1        | ΠL          | HIGH   | Transmit Byte Clock                        | 33                               |