# TESDS5V0ALC Steering Diode Structure ESD Protection Array

# **Small Signal Diode**

#### Features

- ♦Meet IEC61000-4-2 (ESD) ±15kV (air), ±8kV (contact)

♦ Meet IEC61000-4-4 (EET) ratios: 404 (E(E04a))

- ♦Meet IEC61000-4-4 (EFT) rating. 40A (5/50ήs)

- ♦Working Voltage : 5V

- $\diamond \mathsf{Pb}$  free version, RoHS compliant, and Halogen free

# **Mechanical Data**

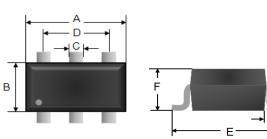

- $\diamond$ Case : SOT-26 standard package, molded plastic

- ♦High temperature soldering guaranteed: 260°C/10s

- ♦Molding Compound Flammability Rating : UL 94V-O

- ♦Weight :16 mg (approximately)

- ♦Marking Code : Y B05

# Applications

♦USB Power & Data Line Protection

- $\diamond Notebooks,$  Desktops, Servers and Video Graphics Cards

- ♦Monitors and Flat Panel Displays

- ♦Portable Instrumentation

- ♦Set Top Box

# **Ordering Information**

| Part No.    | Package | Packing      | Packing Code | Marking |

|-------------|---------|--------------|--------------|---------|

| TESDS5V0ALC | SOT-26  | 3K / 7" Reel | RFG          | Y B05   |

# **Maximum Ratings and Electrical Characteristics**

Rating at 25°C ambient temperature unless otherwise specified.

#### **Maximum Ratings**

| Type Number                                                    | Symbol   | Value        | Units |

|----------------------------------------------------------------|----------|--------------|-------|

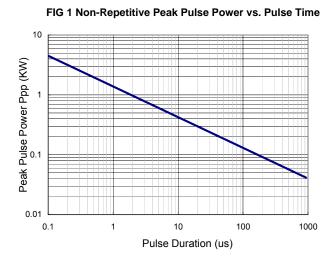

| Peak Pulse Power (tp=8/20µs waveform)                          | Ppp      | 200          | W     |

| Peak Pulse Current (tp = 8/20µs)                               | PP       | 5            | A     |

| ESD per IEC 61000-4-2 (Air)<br>ESD per IEC 61000-4-2 (Contact) | Vesd     | ±27<br>±16   | KV    |

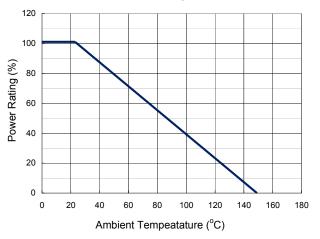

| Junction and Storage Temperature Range                         | TJ, Tstg | -55 to + 150 | °C    |

#### **Electrical Characteristics**

| Type Number               |                              | Symbol            | Min   | Max   | Units |

|---------------------------|------------------------------|-------------------|-------|-------|-------|

| Reverse Stand-Off Voltage |                              | VRWM              | -     | 5     | V     |

| Reverse Breakdown Voltac  | l <b>⊧= 1mA</b>              | V <sub>(BR)</sub> | 6.5   | -     | V     |

| Reverse Leakage Current   | Vr= 5V                       | IR                | -     | 0.1   | uA    |

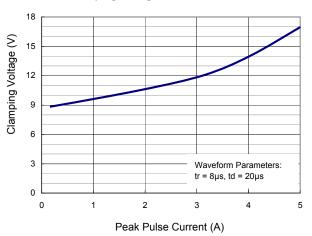

| Clamping Voltage          | I <sub>PP</sub> = 1A         | Vc                | -     | 9.8   | · V   |

|                           | I <sub>PP</sub> = 3A         |                   | -     | 17    |       |

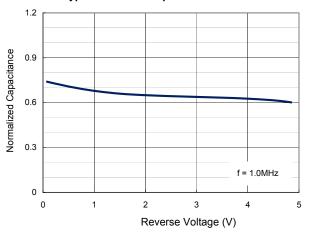

| Junction Capacitance      | V <sub>R</sub> =0V, f=1.0MHz | CJ                | 0.7 ( | Тур.) | pF    |

G

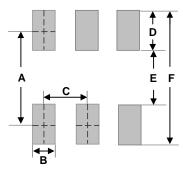

| Dimensions | Unit      | (mm) | Unit (inch) |       |  |

|------------|-----------|------|-------------|-------|--|

| Dimensions | Min       | Max  | Min         | Max   |  |

| А          | 2.80      | 3.00 | 0.110       | 0.118 |  |

| В          | 1.50      | 1.70 | 0.059       | 0.067 |  |

| С          | 0.30      | 0.50 | 0.012       | 0.020 |  |

| D          | 1.80      | 2.00 | 0.071       | 0.079 |  |

| E          | 2.65      | 2.95 | 0.104       | 0.112 |  |

| F          | 1.05      | 1.15 | 0.041       | 0.045 |  |

| G          | 0.575 REF |      | 0.022 REF   |       |  |

# Pin Configutation

### **Small Signal Diode**

### **Rating and Characteristic Curves**

FIG 2 Pulse Waveform 110 100 Waveform Parameters: tr = 8 $\mu$ s, td = 20 $\mu$ s 90 Percent of Ipp 00 00 08 00 00 08 e 40 30 td=lpp/2 20 10 0 0 5 10 15 20 25 30 Time (us)

FIG 3 Admissible Power Dissipation Curve

FIG 5 Clamping Voltage vs. Peak Pulse Current

FIG 4 Typical Junction Capacitance

# Small Signal Diode

## **Applications Information**

- Designed to protect protect high speed data interfaces

- Designed to protect four data lines from transient over-voltages by clamping them to a fixed reference

- Designed to protect protect sensitive components which are connected to data and transmission lines from overvoltage caused by electrostatic discharge (ESD), electrical fast transients (EFT), and lightning.

- TESDS5V0ALC incorporates eight surge rated, low capacitance steering diodes and a TVS diode in a single package

♦During transient conditions, the steering diodes direct the transient to either the positive side of the power supply line or to ground

♦The internal TVS diode prevents over-voltage on the power line, protecting any downstream components

## **Circuit Board Layout Recommendations**

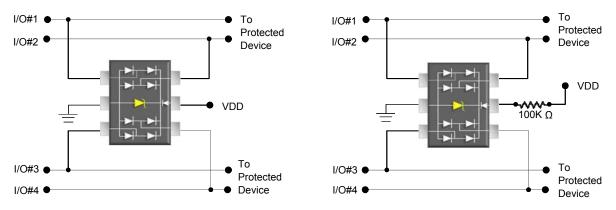

♦To protect data lines and the power line, connect pin 5 directly to the VDD. In this configuration the data lines are referenced to the supply voltage. The internal TVS diode prevents over-voltage on the supply rail.

- The TESDS5V0ALC can be isolated from the power supply by adding a series resistor between pin 5 and VDD. A value of 100kΩ is recommended. The internal TVS and steering diodes remain biased, providing the advantage of lower capacitance.

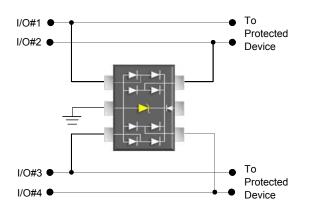

- <sup>2</sup>In applications where no positive supply reference is available, or complete supply isolation is desired, the internal TVS may be used as the reference. In this case, pin 5 is not connected. The steering diodes will begin to conduct when the voltage

♦Data Line and Power Supply Protection Using Vcc as reference

♦Data Line Protection with Bias and Power Supply Isolation

♦Data Line Protection Using Internal TVS Diode as Reference

# TESDS5V0ALC Steering Diode Structure ESD Protection Array

## Small Signal Diode

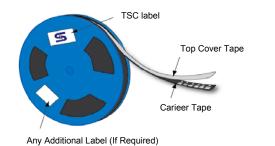

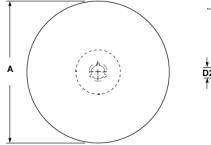

## **Tape & Reel specification**

10 Pitches Cumulative P0 Tolerance on Tape ±2.0mm ( ±0.008") \$ Ε € K B₁ B, D Тор For Components 2.0mm X 1.2mm Cover Tape See Not and Large Center Lines of Cavity κ A<sub>0</sub>

| Item                   | Symbol | Dimension<br>(mm) |

|------------------------|--------|-------------------|

| Carrier depth          | К      | 1.22 Max.         |

| Sprocket hole          | D      | 1.50 +0.10        |

| Reel outside diameter  | A      | 180 ± 1           |

| Reel inner diameter    | D1     | 50 Min.           |

| Feed hole width        | D2     | 13.0 ± 0.5        |

| Sprocke hole position  | E      | 1.75 ±0.10        |

| Sprocke hole pitch     | P0     | 4.00 ±0.10        |

| Embossment center      | P1     | 2.00 ±0.10        |

| Overall tape thickness | Т      | 0.6 Max.          |

| Tape width             | W      | 8.30 Max.         |

| Reel width             | W1     | 14.4 Max.         |

Direction of Feed

#### For Machine Reference Only Including Draft and RADLL Concentric Around B<sub>0</sub>

W1

### Suggested PAD Layout

| Dimensions | Unit (inch) | Unit (mm) |

|------------|-------------|-----------|

| A          | 0.098       | 2.50      |

| В          | 0.024       | 0.60      |

| С          | 0.037       | 0.95      |

| D          | 0.043       | 1.10      |

| E          | 0.055       | 1.40      |

| F          | 0.142       | 3.60      |

Note 1:  $A_0$ ,  $B_0$ , and  $K_0$  are determined by component size. The clearance between the components and the cavity must be within 0.05 mm min. to 0.5 mm max. The component cannot rote more than 10 ° within the determined cavity.

Note 2: If B<sub>1</sub> exceeds 4.2 mm(0.165") for 8 mm embossed tape, the tape may not feed through all tape feeders.

Note 3: The suggested land pattern dimensions have been provided for reference only, as actual pad layouts may vary despending on application.