## FAN5355 1A / 0.8A, 3MHz Digitally Programmable TinyBuck<sup>™</sup> Regulator

#### **Features**

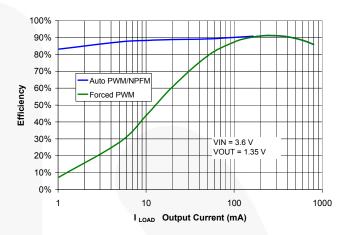

- 91% Efficiency at 3MHz

- 800mA or 1A Output Current<sup>(1)</sup>

- 2.7V to 5.5V Input Voltage Range

- 6 or 7-bit V<sub>OUT</sub> Programmable from 0.75 to 1.975V

- 3MHz Fixed-Frequency Operation

- Excellent Load and Line Transient Response

- Small Size, 1µH Inductor Solution

- ±2% PWM DC Voltage Accuracy

- 35ns Minimum On-Time

- High-Efficiency, Low-Ripple, Light-Load PFM

- Smooth Transition between PWM and PFM

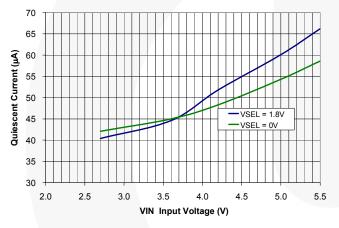

- 37µA Operating PFM Quiescent Current

- Software Selectable 25kHz Minimum PFM Frequency Prevents Audible Noise in PFM Mode

- I<sup>2</sup>C™-Compatible Interface up to 3.4Mbps

- Pin-Selectable or I<sup>2</sup>C<sup>TM</sup> Programmable Output Voltage

- On-the-Fly External Clock Synchronization

- 10-lead MLP (3 x 3mm) or 12-bump CSP Packages

### **Applications**

- SmartReflex<sup>TM</sup>-Compliant Power Supply

- Split Supply DSPs and μP Solutions OMAP™, XSCALE™

- Cell Phones, Smart Phones, PDAs, Digital Cameras, and Portable Media Players

- Micro DC-DC Converter Modules

- Handset Graphic Processors (NVIDIA<sup>®</sup>, ATI)

I<sup>2</sup>C is a trademark of Philips Corporation. SmartReflex and OMAP are trademarks of Texas Instruments. XSCALE is a trademark of Intel Corporation. NVIDIA is a registered trademark of NVIDIA Corporation.

### **Description**

The FAN5355 device is a high-frequency, ultra-fast transient response, synchronous step-down DC-DC converter optimized for low-power applications using small, low-cost inductors and capacitors. The FAN5355 supports up to 800mA or 1A<sup>(1)</sup> load current.

The device is ideal for mobile phones and similar portable applications powered by a single-cell Lithium-Ion battery. With an output voltage range adjustable via  $I^2C^{TM}$  interface from 0.75V to 1.975V, the device supports low-voltage DSPs and processors, core power supplies in smart phones, PDAs, and handheld computers.

The FAN5355 operates at 3MHz (nominal) fixed switching frequency using either its internal oscillator or external SYNC frequency.

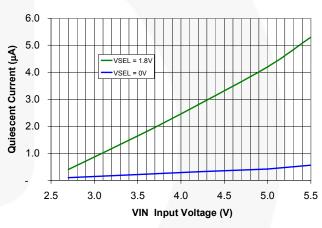

During light-load conditions, the regulator includes a PFM mode to enhance light-load efficiency. The regulator transitions smoothly between PWM and PFM modes with no glitches on  $V_{\text{OUT}}$ . Normal PFM (NPFM) mode offers the lowest quiescent current, at the expense of setpoint accuracy. Enhanced PFM (EPFM) mode features higher accuracy, as well as a 25kHz minimum PFM frequency, designed to prevent the regulator from operating in the audible range. In shutdown, the current consumption is reduced to less than  $2\mu A$ , using software shutdown (EN = 1 with EN\_DCDC = 0), and less than 200nA in hardware shutdown (EN = 0).

The serial interface is compatible with Fast/Standard and High-Speed mode I<sup>2</sup>C specifications, allowing transfers up to 3.4Mbps. This interface is used for dynamic voltage scaling with 12.5mV voltage steps, for reprogramming the mode of operation (PFM or Forced PWM), or to disable/enable the output voltage.

The chip's advanced protection features include short-circuit protection and current and temperature limits. During a sustained over-current event, the IC shuts down and restarts after a delay to reduce average power dissipation into a fault.

During start-up, the IC controls the output slew rate to minimize input current and output overshoot at the end of soft-start. The IC maintains a consistent soft-start ramp, regardless of output load during start-up.

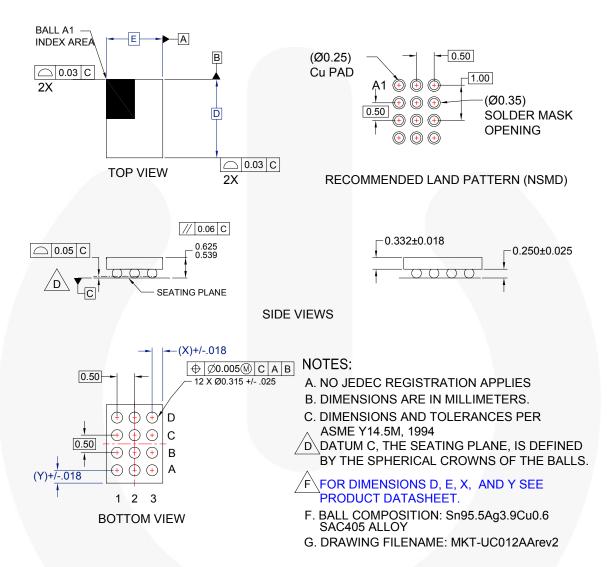

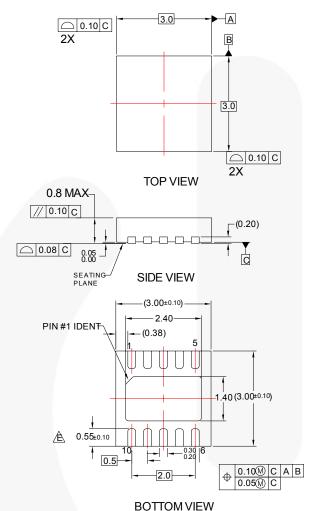

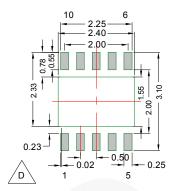

The FAN5355 is available in 10-lead MLP (3x3mm) and 12-bump CSP packages.

### **Ordering Information**

|                  |                   |            | ave<br>ss LSB | v   | V <sub>OUT</sub> Programming |                       | Power-up<br>Defaults |      |                        |

|------------------|-------------------|------------|---------------|-----|------------------------------|-----------------------|----------------------|------|------------------------|

| Order Number (4) | Option            | <b>A</b> 1 | A0            | DAC | MIN.                         | MAX.                  | VSEL0 VSEL1          |      | Package <sup>(4)</sup> |

| FAN5355UC00X     | 00                | 0          | 0             | 6   | 0.7500                       | 1.5375                | 1.05                 | 1.35 | WLCSP-12, 2.23x1.46mm  |

| FAN5355MP00X     | 00                | 0          | 0             | 6   | 0.7500                       | 1.5375                | 1.05                 | 1.35 | MLP-10, 3x3mm          |

| FAN5355UC02X     | 02                | 1          | 0             | 6   | 0.7500                       | 1.4375 <sup>(2)</sup> | 1.05                 | 1.20 | WLCSP-12, 2.23x1.46mm  |

| FAN5355UC03X     | 03                | 0          | 0             | 6   | 0.7500                       | 1.5375                | 1.00                 | 1.20 | WLCSP-12, 2.23x1.46mm  |

| FAN5355UC06X     | 06 <sup>(1)</sup> | 0          | 0             | 6   | 1.1875                       | 1.9750                | 1.80                 | 1.80 | WLCSP-12, 2.23x1.46mm  |

| FAN5355UC07X     | 07 <sup>(1)</sup> | 1          | 1             | 7   | 0.7500 <sup>(3)</sup>        | 1.9750                | 1.05                 | 1.35 | WLCSP-12, 2.23x1.46mm  |

| FAN5355MP07X     | 07 <sup>(1)</sup> | 1          | 1             | 7   | 0.7500 <sup>(3)</sup>        | 1.9750                | 1.05                 | 1.35 | MLP-10, 3x3mm          |

#### Notes:

- 1. Option 06 and 07 is rated for 1A output current. All other options are rated for 800mA output current.

- 2. V<sub>OUT</sub> is limited to the maximum voltage for all VSEL codes greater than the maximum V<sub>OUT</sub> listed.

- 3. V<sub>OUT</sub> may be programmed down 100mV for option 07. Performance below 0.75V is not guaranteed.

- 4. Ø All packages are "green" per JEDEC: J-STD-020B standard. The "X" designator specifies tape and reel packaging.

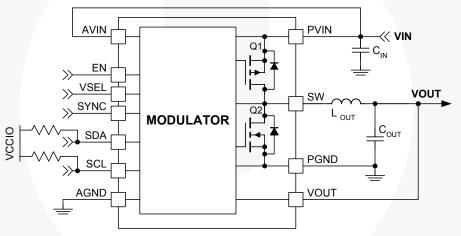

### **Typical Application**

Figure 1. Typical Application

| Component              | Description                               | Vendor                                     | Parameter        | Min. | Тур. | Max. | Units |

|------------------------|-------------------------------------------|--------------------------------------------|------------------|------|------|------|-------|

| L1 (L <sub>OUT</sub> ) | 1μH nominal Murata LC                     |                                            | L <sup>(5)</sup> | 0.7  | 1.0  | 1.2  | μН    |

| LT (LOUT)              | τμιττιοιτιιτίαι                           | or FDK MIPSA2520                           | DCR (series R)   |      | 100  |      | mΩ    |

| Соит                   | 0603 (1.6x0.8x0.8)<br>10μF X5R or better  | Murata or equivalent<br>GRM188R60G106ME47D | C <sup>(6)</sup> | 5.6  | 10.0 | 12.0 | μF    |

| C <sub>IN</sub>        | 0603 (1.6x0.8x0.8)<br>4.7μF X5R or better | Murata or equivalent<br>GRM188R60J475KE19D | C <sup>(6)</sup> | 3.0  | 4.7  | 5.6  | μF    |

**Table 1. Recommended External Components**

#### Notes:

- 5. Minimum L incorporates both tolerance, temperature, and partial saturation effects (L decreases with increasing current).

- 6. Minimum C is a function of initial tolerance, maximum temperature, and the effective capacitance being reduced due to frequency, dielectric, and voltage bias effects.

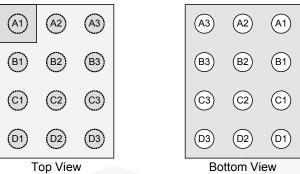

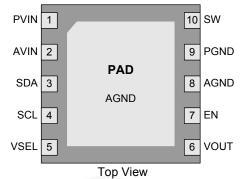

## **Pin Configuration**

Figure 2. WLCSP- 12, 2.23x1.46mm

Figure 3. MLP10, 3x3mm

### **Pin Definitions**

| Pin    | #      | Name | Description                                                                                                                                                                                                                                                                                                         |

|--------|--------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WLCSP  | MLP    | Name | Description                                                                                                                                                                                                                                                                                                         |

| A1, B1 | 9      | PGND | <b>Power GND</b> . Power return for gate drive and power transistors. Connect to AGND on PCB. The connection from this pin to the bottom of $C_{IN}$ should be as short as possible.                                                                                                                                |

| A2     | 10     | SW   | Switching Node. Connect to output inductor.                                                                                                                                                                                                                                                                         |

| А3     | 1      | PVIN | <b>Power Input Voltage</b> . Connect to input power source. The connection from this pin to $C_{\text{IN}}$ should be as short as possible.                                                                                                                                                                         |

| B2     | N/A    | SYNC | <b>Sync</b> . When toggling and SYNC_EN bit is HIGH, the regulator synchronizes to the frequency on this pin. In PWM mode, when this pin is statically LOW or statically HIGH, or when its frequency is outside of the specified capture range, the regulator's frequency is controlled by its internal 3MHz clock. |

| В3     | 2      | AVIN | Analog Input Voltage. Connect to input power source as close as possible to the input bypass capacitor.                                                                                                                                                                                                             |

| C1     | 8, PAD | AGND | <b>Analog GND</b> . This is the signal ground reference for the IC. All voltage levels are measured with respect to this pin.                                                                                                                                                                                       |

| C2     | 7      | EN   | <b>Enable</b> . When this pin is HIGH, the circuit is enabled. When LOW, quiescent current is minimized. This pin should not be left floating.                                                                                                                                                                      |

| C3     | 3      | SDA  | SDA. I <sup>2</sup> C interface serial data.                                                                                                                                                                                                                                                                        |

| D1     | 6      | VOUT | Output Voltage Monitor. Tie this pin to the output voltage. This is a signal input pin to the control circuit and does not carry DC current.                                                                                                                                                                        |

| D2     | 5      | VSEL | <b>Voltage Select</b> . When HIGH, V <sub>OUT</sub> is set by VSEL1. When LOW, V <sub>OUT</sub> is set by VSEL0. This behavior can be overridden through I <sup>2</sup> C register settings. This pin should not be left floating.                                                                                  |

| D3     | 4      | SCL  | SCL. I <sup>2</sup> C interface serial clock.                                                                                                                                                                                                                                                                       |

#### Note:

7. All logic inputs (SDA, SCL, SYNC, EN, and VSEL) are high impedance and should not be left floating. For minimum quiescent power consumption, tie unused logic inputs to AVIN or AGND. If I2C control is unused, tie SDA and SCL to AVIN.

### **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol           | Parameter                                |                                      | Min.        | Max.                      | Units |

|------------------|------------------------------------------|--------------------------------------|-------------|---------------------------|-------|

| \/               | AVIN, SW, PVIN Pins                      |                                      | -0.3        | 6.5                       | V     |

| $V_{CC}$         | Other Pins                               |                                      | -0.3        | AVIN + 0.3 <sup>(8)</sup> | V     |

| ESD              | Electrostatic Discharge Protection Level | Human Body Model per JESD22-A114     | 3.5         |                           | KV    |

| LOD              | Liectiostatic discharge Protection Level | Charged Device Model per JESD22-C101 |             | 1.5                       |       |

| $T_J$            | Junction Temperature                     |                                      | -40         | +150                      | °C    |

| T <sub>STG</sub> | Storage Temperature                      |                                      | <b>–</b> 65 | +150                      | °C    |

| TL               | Lead Soldering Temperature, 10 Seconds   | 6                                    |             | +260                      | °C    |

#### Note:

Lesser of 6.5V or V<sub>CC</sub>+0.3V.

### **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to absolute maximum ratings.

| Symbol          | Parameter                                | Min. | Max. | Units |

|-----------------|------------------------------------------|------|------|-------|

| V <sub>IN</sub> | Supply Voltage                           | 2.7  | 5.5  | V     |

| f               | Frequency Range                          | 2.7  | 3.3  | MHz   |

| V <sub>SW</sub> | SDA and SCL Voltage Swing <sup>(9)</sup> |      | 2.5  | V     |

| T <sub>A</sub>  | Ambient Temperature                      | -40  | +85  | °C    |

| TJ              | Junction Temperature                     | -40  | +125 | °C    |

#### Note:

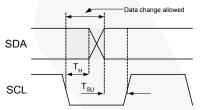

9. The I<sup>2</sup>C interface operates with t<sub>HD;DAT</sub> = 0 as long as the pull-up voltage for SDA and SCL is less than 2.5V. If voltage swings greater than 2.5V are required (for example if the I<sup>2</sup>C bus is pulled up to V<sub>IN</sub>), the minimum t<sub>HD;DAT</sub> must be increased to 80ns. Most I<sup>2</sup>C masters change SDA near the midpoint between the falling and rising edges of SCL, which provides ample t<sub>HD;DAT</sub>.

## **Dissipation Ratings**<sup>(10)</sup>

| Package                                | $R\theta_{JA}^{(11)}$ | Power Rating at T <sub>A</sub> ≤ 25°C | Derating Factor > T <sub>A</sub> = 25°C |

|----------------------------------------|-----------------------|---------------------------------------|-----------------------------------------|

| Molded Leadless Package (MLP)          | 49°C/W                | 2050mW                                | 21mW/°C                                 |

| Wafer-Level Chip-Scale Package (WLCSP) | 110°C/W               | 900mW                                 | 9mW/°C                                  |

#### Notes:

- 10. Maximum power dissipation is a function of  $T_{J(max)}$ ,  $\theta_{JA}$ , and  $T_A$ . The maximum allowable power dissipation at any allowable ambient temperature is  $P_D = [T_{J(max)} T_A] / \theta_{JA}$ .

- 11. This thermal data is measured with high-K board (four-layer board according to JESD51-7 JEDEC standard).

**Electrical Specifications**  $V_{IN} = 3.6V$ ,  $EN = V_{IN}$ ,  $VSEL = V_{IN}$ ,  $EN = V_{IN}$ , EN

| Symbol                | Parameter                                  | Conditions                                                             | Min. | Тур. | Max. | Units |

|-----------------------|--------------------------------------------|------------------------------------------------------------------------|------|------|------|-------|

| Power Sup             | pplies                                     |                                                                        |      | •    |      |       |

| V <sub>IN</sub>       | Input Voltage Range                        |                                                                        | 2.7  |      | 5.5  | V     |

|                       |                                            | I <sub>O</sub> = 0mA, EPFM Mode, F <sub>PFM</sub> = 25kHz              |      | 110  | 150  | μА    |

| $I_{Q}$               | Quiescent Current                          | I <sub>o</sub> = 0mA, NPFM Mode                                        |      | 37   | 50   | μΑ    |

|                       |                                            | I <sub>o</sub> = 0mA, 3MHz PWM Mode                                    |      | 4.8  |      | mA    |

|                       |                                            | EN = GND                                                               |      | 0.1  | 2.0  |       |

| I <sub>SD</sub>       | Shutdown Supply Current                    | EN = V <sub>IN</sub> , EN_DCDC bit = 0,<br>SDA = SCL = V <sub>IN</sub> |      | 0.1  | 2.0  | μА    |

| V                     | Linder Voltage Leekeut Threehold           | V <sub>IN</sub> Rising                                                 |      | 2.40 | 2.60 | V     |

| $V_{UVLO}$            | Under-Voltage Lockout Threshold            | V <sub>IN</sub> Falling                                                | 2.00 | 2.15 | 2.30 | V     |

| V <sub>UVHYST</sub>   | Under-Voltage Lockout Hysteresis           |                                                                        | 200  | 250  | 300  | mV    |

| ENABLE, \             | /SEL, SDA, SCL, SYNC                       |                                                                        |      | •    |      |       |

| V <sub>IH</sub>       | HIGH-Level Input Voltage                   |                                                                        | 1.2  |      |      | V     |

| V <sub>IL</sub>       | LOW-Level Input Voltage                    |                                                                        |      |      | 0.4  | V     |

| I <sub>IN</sub>       | Input Bias Current                         | Input tied to GND or V <sub>IN</sub>                                   |      | 0.01 | 1.00 | μА    |

| Power Swi             | tch and Protection                         |                                                                        |      | •    |      |       |

|                       |                                            | V <sub>IN</sub> = 3.6V, CSP Package                                    |      | 145  |      |       |

| R <sub>DS(ON)P</sub>  | P-channel MOSFET On Resistance             | V <sub>IN</sub> = 3.6V, MLP Package                                    |      | 165  |      | mΩ    |

|                       |                                            | V <sub>IN</sub> = 2.7V, MLP Package                                    |      | 200  |      |       |

| I <sub>LKGP</sub>     | P-channel Leakage Current                  | V <sub>DS</sub> = 6V                                                   |      |      | 1    | μА    |

|                       |                                            | V <sub>IN</sub> = 3.6V, CSP Package                                    |      | 75   |      |       |

| R <sub>DS(ON)N</sub>  | N-channel MOSFET On Resistance             | V <sub>IN</sub> = 3.6V, MLP Package                                    |      | 95   |      | mΩ    |

|                       |                                            | V <sub>IN</sub> = 2.7V, MLP Package                                    |      | 101  |      |       |

| I <sub>LKGN</sub>     | N-channel Leakage Current                  | V <sub>DS</sub> = 6V                                                   | /    |      | 1    | μΑ    |

| R <sub>DIS</sub>      | Discharge Resistor for Power-down Sequence | Options 03, 06, 07                                                     |      | 15   | 50   | Ω     |

|                       |                                            | $2.7V \le V_{IN} \le 4.2V$ , All Options Except 06 and 07              | 1150 | 1350 | 1600 |       |

| I <sub>LIMPK</sub>    | P-MOS Current Limit                        | $2.7V \le V_{IN} \le 5.5V$ , All Options Except 06 and 07              | 1050 | 1350 | 1600 | mA    |

|                       |                                            | 2.7V ≤ V <sub>IN</sub> ≤ 4.2V, 06 and 07 Option                        | 1300 | 1550 | 1800 |       |

| $T_{LIMIT}$           | Thermal Shutdown                           |                                                                        |      | 150  |      | °C    |

| T <sub>HYST</sub>     | Thermal Shutdown Hysteresis                |                                                                        |      | 20   |      | °C    |

| Frequency             | Control                                    |                                                                        |      |      |      |       |

| f <sub>SW</sub>       | Oscillator Frequency                       |                                                                        | 2.65 | 3.00 | 3.35 | MHz   |

| f <sub>SYNC</sub>     | Synchronization Range                      |                                                                        | 2.7  | 3.0  | 3.3  | MHz   |

| D <sub>SYNC</sub>     | Synchronization Duty Cycle                 |                                                                        | 20   |      | 80   | %     |

| f <sub>SYNCVAL</sub>  | SYNC Frequency Rejection                   |                                                                        | 1.6  |      | 4.3  | MHz   |

| f <sub>PFM(MIN)</sub> | Minimum PFM Frequency                      | EPFM Mode, I <sub>LOAD</sub> = 0                                       |      | 25   |      | kHz   |

Continued on the following page...

### **Electrical Specifications** (Continued)

$V_{IN}$  = 3.6V, EN =  $V_{IN}$ , VSEL =  $V_{IN}$ , SYNC = GND, VSEL0(6) bit = 1, CONTROL2[4:3] = 00.  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $T_A$  = 25°C. Circuit and components according to Figure 1

| Symbol                                   | Parameter                 |           | Conditions                                                                                         | Min. | Тур. | Max. | Units |

|------------------------------------------|---------------------------|-----------|----------------------------------------------------------------------------------------------------|------|------|------|-------|

| Output Rec                               | gulation                  |           |                                                                                                    |      |      |      | •     |

|                                          |                           |           | I <sub>OUT(DC)</sub> = 0, Forced PWM, V <sub>OUT</sub> = 1.35V                                     | -1.5 |      | 1.5  | %     |

|                                          |                           | Option 00 | $2.7V \le V_{IN} \le 5.5V$ , $V_{OUT}$ from 0.75 to 1.5375, $I_{OUT(DC)} = 0$ to 800mA, Forced PWM | -2   |      | 2    | %     |

|                                          |                           |           | $2.7V \le V_{IN} \le 5.5V$ , $V_{OUT}$ from 0.75 to 1.5375, $I_{OUT(DC)} = 0$ to 800mA, NPFM Mode  | -1.5 |      | 3.5  | %     |

|                                          |                           |           | I <sub>OUT(DC)</sub> = 0, Forced PWM, V <sub>OUT</sub> = 1.20V                                     | -1.5 |      | 1.5  | %     |

|                                          |                           | Option 02 | $2.7V \le V_{IN} \le 5.5V$ , $V_{OUT}$ from 0.75 to 1.4375, $I_{OUT(DC)} = 0$ to 800mA, Forced PWM | -2   |      | 2    | %     |

|                                          |                           |           | $2.7V \le V_{IN} \le 5.5V$ , $V_{OUT}$ from 0.75 to 1.4375, $I_{OUT(DC)} = 0$ to 800mA, NPFM Mode  | -1.5 |      | 3.5  | %     |

|                                          | 6                         |           | I <sub>OUT(DC)</sub> = 0, Forced PWM, V <sub>OUT</sub> = 1.20V                                     | -1.5 |      | 1.5  | %     |

|                                          | V <sub>OUT</sub> Accuracy |           | $2.7V \le V_{IN} \le 5.5V$ , $V_{OUT}$ from 0.75 to 1.5375, $I_{OUT(DC)} = 0$ to 800mA, Forced PWM | -2   |      | 2    | %     |

|                                          |                           | Option 03 | $2.7V \le V_{IN} \le 5.5V$ , $V_{OUT}$ from 0.75 to 1.5375, $I_{OUT(DC)} = 0$ to 800mA, NPFM Mode  | -1.5 |      | 3.5  | %     |

| $V_{OUT}$                                |                           |           | $2.7V \le V_{IN} \le 5.5V$ , $V_{OUT}$ from 0.75 to 1.5375, $I_{OUT(DC)} = 0$ to 800mA, EPFM Mode  | -0.5 |      | 2    | %     |

|                                          |                           |           | I <sub>OUT(DC)</sub> = 0, Forced PWM, V <sub>OUT</sub> = 1.800V                                    | -1.5 |      | 1.5  | %     |

|                                          |                           |           | $2.7V \le V_{IN} \le 5.5V$ , $V_{OUT}$ from 1.185 to 1.975, $I_{OUT(DC)} = 0$ to 1A, Forced PWM    | -2   |      | 2    | %     |

|                                          |                           | Option 06 | $2.7V \le V_{IN} \le 5.5V$ , $V_{OUT}$ from 1.185 to 1.975, $I_{OUT(DC)} = 0$ to 1A, NPFM Mode     | -1.5 |      | 3.5  | %     |

|                                          | \                         |           | $2.7V \le V_{IN} \le 5.5V$ , $V_{OUT}$ from 1.185 to 1.975, $I_{OUT(DC)} = 0$ to 1A, EPFM Mode     | -0.5 |      | 2    | %     |

|                                          |                           |           | I <sub>OUT(DC)</sub> = 0, Forced PWM, V <sub>OUT</sub> = 1.35V                                     | -1.5 |      | 1.5  | %     |

|                                          |                           |           | $2.7V \le V_{IN} \le 5.5V$ , $V_{OUT}$ from 0.75 to 1.6875, $I_{OUT(DC)} = 0$ to 1A, Forced PWM    | -2   |      | 2    | %     |

|                                          |                           | Option 07 | $2.7V \le V_{IN} \le 5.5V$ , $V_{OUT}$ from 0.75 to 1.6875, $I_{OUT(DC)} = 0$ to 1A, NPFM Mode     | -1.5 |      | 3.5  | %     |

|                                          |                           |           | $2.7V \le V_{IN} \le 5.5V$ , $V_{OUT}$ from 0.75 to 1.6875, $I_{OUT(DC)} = 0$ to 1A, EPFM Mode     | -0.5 |      | 2    | %     |

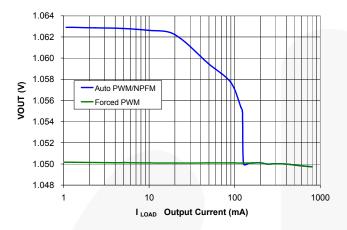

| $\frac{\Delta V_{OUT}}{\Delta I_{LOAD}}$ | Load Regulation           |           | I <sub>OUT(DC)</sub> = 0 to 800mA, Forced PWM                                                      |      | -0.5 |      | %/A   |

| $\frac{\Delta V_{OUT}}{\Delta V_{IN}}$   | Line Regulation           |           | 2.7V ≤ V <sub>IN</sub> ≤ 5.5V, I <sub>OUT(DC)</sub> = 300mA                                        |      | 0    | (+   | %/V   |

| \/                                       | Output Bingle Va          | ultago    | PWM Mode, V <sub>OUT</sub> = 1.35V                                                                 |      | 2.2  |      | mVP-l |

| $V_{RIPPLE}$                             | Output Ripple Vo          | oitage    | PFM Mode, I <sub>OUT(DC)</sub> = 10mA                                                              |      | 20   |      | mVP-f |

Continued on the following page...

### **Electrical Specifications** (Continued)

$V_{IN}$  = 3.6V, EN =  $V_{IN}$ , VSEL =  $V_{IN}$ , SYNC = GND, VSEL0(6) bit = 1, CONTROL2[4:3] = 00.  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $T_A$  = 25°C. Circuit and components according to Figure 1.

| Symbol            | Parameter                        |                        | Conditions                                                                                           | Min. | Тур.  | Max. | Units |

|-------------------|----------------------------------|------------------------|------------------------------------------------------------------------------------------------------|------|-------|------|-------|

| DAC               |                                  |                        |                                                                                                      | •    | •     | •    |       |

|                   | Resolution                       |                        | Option 07                                                                                            | 7    |       |      | Bits  |

|                   | Resolution                       |                        | All Other Options                                                                                    | 6    |       |      | Bits  |

|                   | Differential Nonlinea            | arity                  | Monotonicity Assured by Design                                                                       |      |       | 0.8  | LSB   |

| Timing            |                                  |                        |                                                                                                      |      |       |      |       |

| I2C <sub>EN</sub> | EN HIGH to I <sup>2</sup> C Sta  | art                    |                                                                                                      | 250  |       |      | μS    |

| $t_{V(L-H)}$      | V <sub>OUT</sub> LOW to HIGH     | Settling               | $R_{LOAD}$ = 75 $\Omega$ , Transition from 1.0 to 1.5375V $V_{OUT}$ Settled to within 2% of Setpoint | 4    | 7     |      | μS    |

| Soft-Start        |                                  |                        |                                                                                                      |      |       |      |       |

|                   | Regulator Enable                 | Option 06              | $R_{LOAD} \ge 5\Omega$ , to $V_{OUT} = 1.8000V$                                                      |      | 170   | 210  | μS    |

| t <sub>ss</sub>   | to Regulated V <sub>OUT</sub>    | All Other<br>Options   | $R_{LOAD} \ge 5\Omega$ , to $V_{OUT}$ = Power-up Default                                             |      | 140   | 180  | μS    |

| V <sub>SLEW</sub> | Soft-start V <sub>OUT</sub> Slev | v Rate <sup>(12)</sup> |                                                                                                      |      | 18.75 |      | V/ms  |

#### Note:

12. Option 06 slew rate is 35.5V/ms during the first 16µs of soft-start.

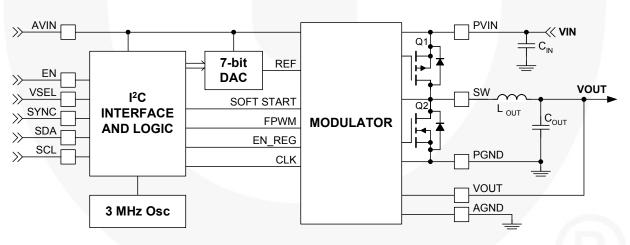

Figure 4. Block Diagram

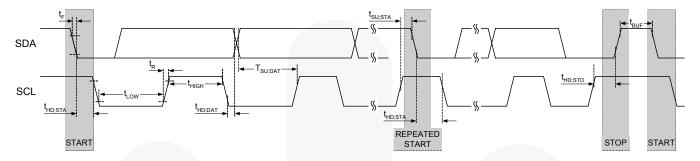

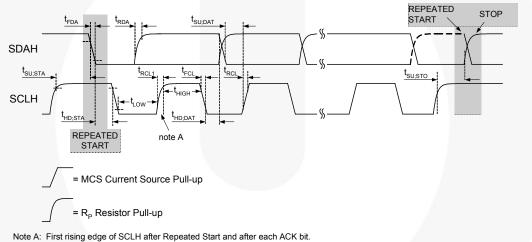

# I<sup>2</sup>C Timing Specifications

Guaranteed by design.

| Symbol              | Parameter                         | Conditions                                                           | Min.         | Тур.                                          | Max.                                                                                 | Unit     |

|---------------------|-----------------------------------|----------------------------------------------------------------------|--------------|-----------------------------------------------|--------------------------------------------------------------------------------------|----------|

|                     |                                   | Standard mode                                                        |              |                                               | 100                                                                                  | kHz      |

| $f_{SCL}$           | SCL Clock Frequency               | Fast mode                                                            |              |                                               | 400                                                                                  | kHz      |

| ISCL                | SOL Clock I requericy             | High-Speed mode, C <sub>B</sub> ≤ 100pF                              |              |                                               | 3400                                                                                 | kHz      |

|                     |                                   | High-Speed mode, C <sub>B</sub> ≤ 400pF                              |              |                                               | 100<br>400                                                                           | kHz      |

| tour                | Bus-free Time between STOP and    | Standard mode                                                        |              | 4.7                                           |                                                                                      | μS       |

| t <sub>BUF</sub>    | START Conditions                  | Fast mode                                                            |              | 1.3                                           |                                                                                      | μS       |

|                     | START or Reported START Hold      | Standard mode                                                        |              | 4                                             |                                                                                      | μS       |

| $t_{\text{HD;STA}}$ | START or Repeated START Hold Time | Fast mode                                                            |              | 600                                           |                                                                                      | ns       |

|                     |                                   | High-Speed mode                                                      |              | 160                                           |                                                                                      | ns       |

|                     |                                   | Standard mode                                                        |              | 4.7                                           |                                                                                      | μS       |

| tı ow               | t <sub>LOW</sub> SCL LOW Period   | Fast mode                                                            | A            | 1.3                                           |                                                                                      | ns       |

| LOW                 |                                   | High-Speed mode, C <sub>B</sub> ≤ 100pF                              |              | 160                                           |                                                                                      | ns       |

|                     |                                   | High-Speed mode, C <sub>B</sub> ≤ 400pF                              |              | 320                                           |                                                                                      | ns       |

|                     |                                   | Standard mode                                                        |              | 4                                             |                                                                                      | μS       |

| t <sub>HIGH</sub>   | SCL HIGH Period                   | Fast mode                                                            |              | 600                                           |                                                                                      | ns       |

| TIION               |                                   | High-Speed mode, C <sub>B</sub> ≤ 100pF                              |              | 60                                            |                                                                                      | ns       |

|                     |                                   | High-Speed mode, C <sub>B</sub> ≤ 400pF                              |              | 120                                           | 3.45<br>900<br>70<br>150<br>300<br>80<br>160<br>300<br>80<br>160<br>300<br>80<br>160 | ns       |

|                     |                                   | Standard mode                                                        |              | 4.7                                           |                                                                                      | μS       |

| t <sub>SU;STA</sub> | Repeated START Setup Time         | Fast mode                                                            |              | _                                             |                                                                                      | ns       |

|                     |                                   | High-Speed mode                                                      |              |                                               |                                                                                      | ns       |

|                     |                                   | Standard mode                                                        |              | 600<br>160<br>250<br>100<br>10<br>3.45<br>900 | ns                                                                                   |          |

| t <sub>SU;DAT</sub> | Data Setup Time                   | Fast mode                                                            |              |                                               |                                                                                      | ns       |

|                     |                                   | High-Speed mode                                                      | _            | 10                                            |                                                                                      | ns       |

|                     |                                   | Standard mode                                                        | 0            |                                               |                                                                                      | μS       |

| t <sub>HD;DAT</sub> | Data Hold Time <sup>(9)</sup>     | Fast mode                                                            | 0            |                                               |                                                                                      | ns       |

| ,                   |                                   | High-Speed mode, C <sub>B</sub> ≤ 100pF                              | 0            |                                               |                                                                                      | ns       |

|                     |                                   | High-Speed mode, C <sub>B</sub> ≤ 400pF                              | 0            | 10                                            |                                                                                      | ns       |

|                     |                                   | Standard mode                                                        | 20+0         |                                               |                                                                                      | ns       |

| t <sub>RCL</sub>    | SCL Rise Time                     | Fast mode                                                            | 20+0         |                                               |                                                                                      | ns       |

|                     |                                   | High-Speed mode, C <sub>B</sub> ≤ 100pF                              |              | 10                                            |                                                                                      | ns       |

| -                   |                                   | High-Speed mode, C <sub>B</sub> ≤ 400pF                              | 20.10        | 20                                            |                                                                                      | ns       |

|                     |                                   | Standard mode                                                        | 20+0<br>20+0 |                                               |                                                                                      | ns       |

| $t_{FCL}$           | SCL Fall Time                     | Fast mode                                                            | 20+0         |                                               |                                                                                      | ns       |

|                     |                                   | High-Speed mode, $C_B \le 100pF$<br>High-Speed mode, $C_B \le 400pF$ |              | 10<br>20                                      |                                                                                      | ns<br>ns |

|                     |                                   | Standard mode                                                        | 20+0         |                                               |                                                                                      | ns       |

| t <sub>RDA</sub>    | SDA Rise Time                     | Fast mode                                                            | 20+0         |                                               |                                                                                      |          |

|                     | Rise Time of SCL After a Repeated | High-Speed mode, C <sub>B</sub> ≤ 100pF                              | 20+0         | 10                                            |                                                                                      | ns<br>ns |

| t <sub>RCL1</sub>   | START Condition and After ACK Bit | High-Speed mode, $C_B \le 100pr$                                     |              | 20                                            |                                                                                      | ns       |

|                     |                                   | Standard mode                                                        | 20+0         |                                               |                                                                                      | ns       |

|                     |                                   | Fast mode                                                            | 20+0         |                                               |                                                                                      | ns       |

| $t_{\sf FDA}$       | SDA Fall Time                     | High-Speed mode, C <sub>B</sub> ≤ 100pF                              | 2010         | 10                                            |                                                                                      | ns       |

|                     |                                   | High-Speed mode, C <sub>B</sub> ≤ 400pF                              |              | 20                                            |                                                                                      | ns       |

|                     |                                   | Standard mode                                                        |              | 4                                             | . 50                                                                                 | μS       |

| t <sub>su:sto</sub> | Stop Condition Setup Time         | Fast mode                                                            |              | 600                                           |                                                                                      | ns       |

| -50,510             |                                   | High-Speed mode                                                      |              | 160                                           |                                                                                      | ns       |

| Св                  | Capacitive Load for SDA and SCL   | g epeca mode                                                         |              | 1.00                                          | 400                                                                                  | pF       |

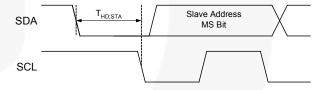

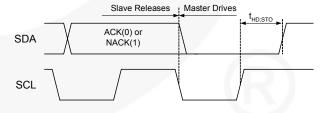

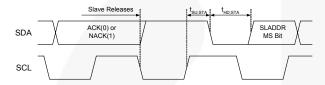

## **Timing Diagrams**

Figure 5. I<sup>2</sup>C Interface Timing for Fast and Slow Modes

Figure 6. I<sup>2</sup>C Interface Timing for High-Speed Mode

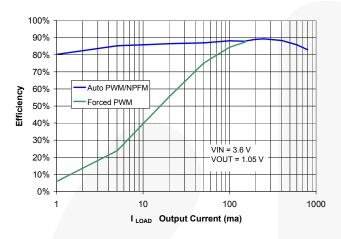

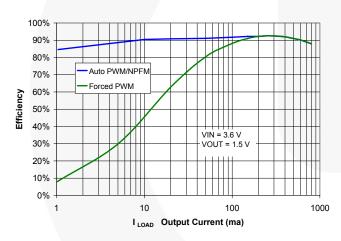

### **Typical Performance Characteristics**

Unless otherwise specified, Auto-PWM/NPFM,  $V_{IN}$  = 3.6V,  $T_A$  = 25°C, and recommended components as specified in Table 1.

### **Efficiency**

Figure 7. Efficiency vs. Load at V<sub>OUT</sub> = 1.05V

Figure 9. Efficiency vs. Load at  $V_{OUT} = 1.50V$

Figure 8. Efficiency vs. Load at V<sub>OUT</sub> = 1.35V

### **Typical Performance Characteristics**

Unless otherwise specified, Auto-PWM/NPFM, V<sub>IN</sub> = 3.6V, T<sub>A</sub> = 25°C, and recommended components as specified in Table 1.

1.364

1.362

1.360

1.358

— Auto PWMNPFM

— Forced PWM

1.352

1.350

1.348

1 10 100 1000

I Load Output Current (mA)

Figure 10. Load Regulation at V<sub>OUT</sub> = 1.05V

Figure 11. Load Regulation at V<sub>OUT</sub> = 1.35V

Figure 12. Quiescent Current, I<sub>LOAD</sub> = 0, EN = 1.8V

Figure 13. Shutdown Current,  $I_{LOAD} = 0$ , EN = 0

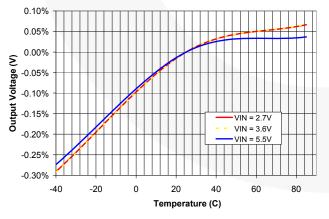

Figure 14. % V<sub>OUT</sub> Shift vs. Temperature (Normalized)

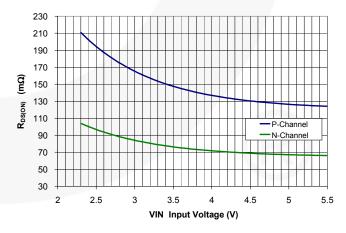

Figure 15. Output Stage R<sub>DS(ON)</sub> vs. V<sub>IN</sub>

Unless otherwise specified,  $V_{IN}$  = 3.6V,  $V_{OUT}$  = 1.35V, and load step  $t_R$  =  $t_F$  < 100ns.

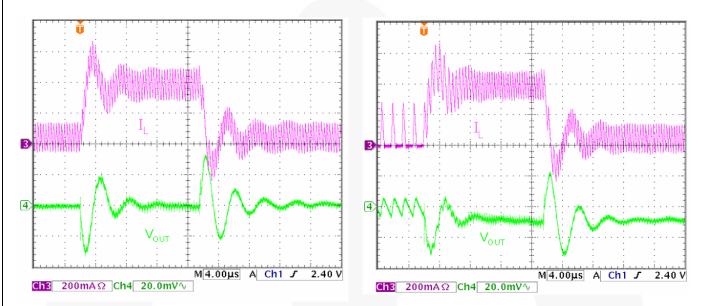

### **Load Transient Response**

Figure 16. 50mA to 400mA to 50mA, Forced PWM

Figure 17. 50mA to 400mA to 50mA, Auto PWM/NPFM

Figure 18. 400mA to 750mA to 400mA, Auto PWM/NPFM

Figure 19. 0mA to 125mA to 0mA, Auto PWM/NPFM

Unless otherwise specified,  $V_{IN} = 3.6V$ .

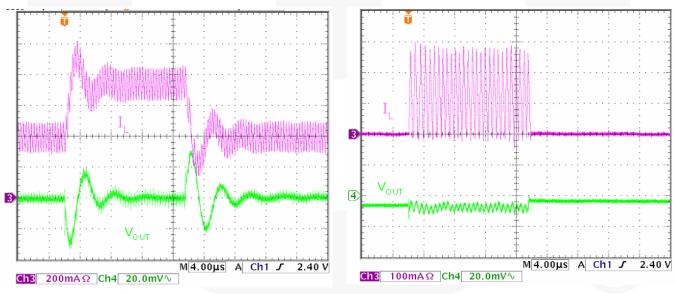

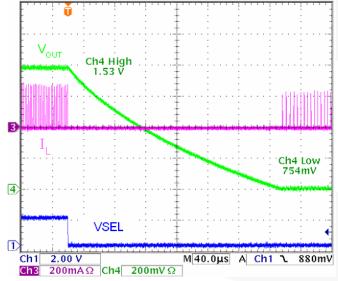

#### **VSEL Transitions**

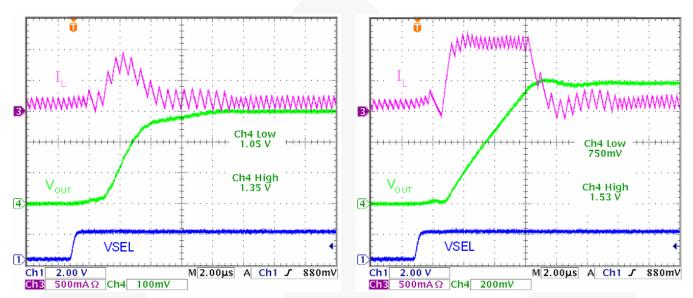

Figure 20. Single-Step,  $R_{LOAD} = 6.2\Omega$

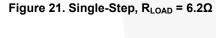

Figure 22. Single-Step,  $R_{LOAD} = 50\Omega$

Figure 23. Single-Step,  $R_{LOAD} = 50\Omega$

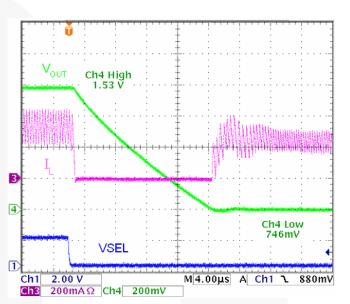

Unless otherwise specified,  $V_{IN} = 3.6V$ .

#### **VSEL Transitions**

Figure 24. Single-Step from Forced PWM (MODE1=0),  $R_{LOAD}$  =  $50\Omega$

Figure 26. Single–Step from Auto PWM/PFM (MODE1=1),  $R_{LOAD}$  =  $50\Omega$

Figure 25. Single Step,  $R_{LOAD} = 6.2\Omega$

$R_{LOAD}$  is switched with N-channel MOSFET from VOUT to GND.  $V_{IN}$  = 3.6V, initial  $V_{OUT}$  = 1.35V, initial  $I_{LOAD}$  = 0mA.

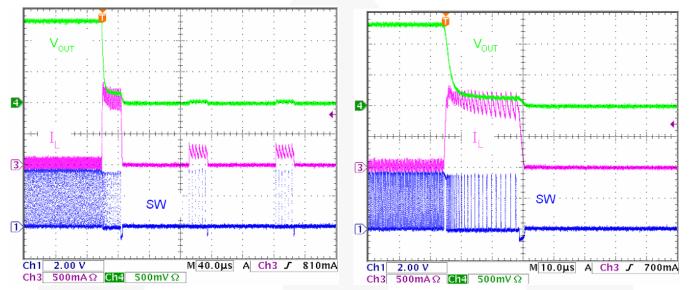

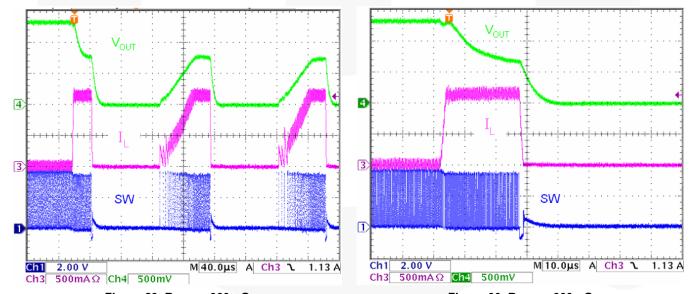

### **Short Circuit and Over-Current Fault Response**

Figure 27. Metallic Short Applied at VOUT

Figure 28. Metallic Short Applied at VOUT

Figure 29.  $R_{LOAD} = 660 m\Omega$

Figure 30.  $R_{LOAD} = 660 m\Omega$

Unless otherwise specified,  $V_{IN} = 3.6V$ .

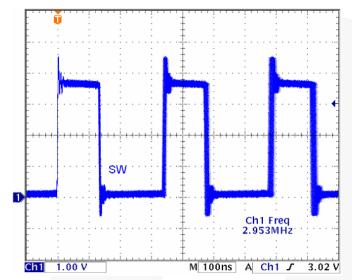

Ch1 Freq 3.215MHz

Figure 31. SW-Node Jitter (Infinite Persistence),  $I_{LOAD} = 200 mA$

Figure 32. SW-Node Jitter, External Synchronization (Infinite Persistence), I<sub>LOAD</sub> = 200mA

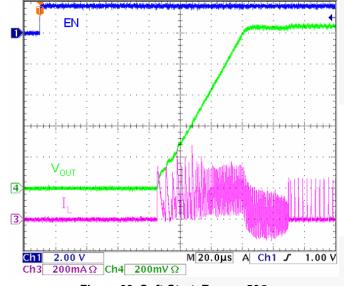

Figure 33. Soft-Start,  $R_{LOAD} = 50\Omega$

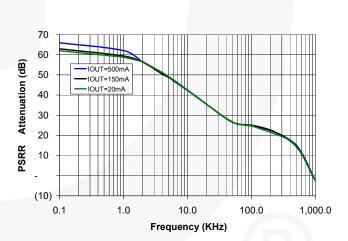

Figure 34. V<sub>IN</sub> Ripple Rejection (PSRR)

### **Circuit Description**

#### Overview

The FAN5355 is a synchronous buck regulator that typically operates at 3MHz with moderate to heavy load currents. At light load currents, the converter operates in power-saving PFM mode. The regulator automatically transitions between fixed-frequency PWM and variable-frequency PFM mode to maintain the highest possible efficiency over the full range of load current.

The FAN5355 uses a very fast non-linear control architecture to achieve excellent transient response with minimum-sized external components.

The FAN5355 integrates an  $I^2$ C-compatible interface, allowing transfers up to 3.4Mbps. This communication interface can be used to:

- Dynamically re-program the output voltage in 12.5mV increments.

- Reprogram the mode of operation to enable or disable PFM mode.

- Control voltage transition slew rate.

- Control the frequency of operation by synchronizing to an external clock.

- Enable / disable the regulator.

For more details, refer to the  $\hat{l}^2C$  Interface and Register Description sections.

### **Output Voltage Programming**

| Option        | V <sub>OUT</sub> Equation                                                                                                                                                                                                                         |     |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 00, 02,<br>03 | $V_{OUT} = 0.75 + N_{VSEL} \bullet 12.5 mV$                                                                                                                                                                                                       | (1) |

| 07            | $\begin{aligned} &V_{OUT} = 0.100 + N_{VSEL} \bullet 25 mV \\ &\text{for } N_{VSEL} = 0 \text{ to } 23 \end{aligned}$ $\begin{aligned} &V_{OUT} = 0.675 + \left(N_{VSEL} - 23\right) \bullet 12.5 mV \\ &\text{for } N_{VSEL} > 23 \end{aligned}$ | (2) |

| 06            | $V_{OUT} = 1.1875 + N_{VSEL} \bullet 12.5 mV$                                                                                                                                                                                                     | (3) |

where  $N_{VSEL}$  is the decimal value of the setting of the VSEL register that controls  $V_{OUT}$ .

#### Note:

13. Option 02 maximum voltage is 1.4375V (see Table 3).

#### Power-up, EN, and Soft-start

All internal circuits remain de-biased and the IC is in a very low quiescent current state until the following are true:

- 1. V<sub>IN</sub> is above its rising UVLO threshold, and

- 2. EN is HIGH.

At that point, the IC begins a soft-start cycle, its I<sup>2</sup>C interface is enabled, and its registers loaded with their default values.

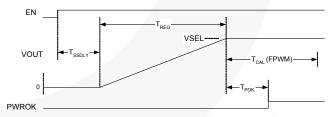

During the initial soft-start,  $V_{OUT}$  ramps linearly to the setpoint programmed in the VSEL register selected by the VSEL pin. The soft start features a fixed output voltage slew rate of 18.75V/ms, and achieves regulation approximately  $90\mu s$  after EN rises. PFM mode is enabled during soft-start until the output is in regulation, regardless of the MODE bit settings. This allows the regulator to start into a partially charged output without discharging it; in other words, the regulator does not allow current to flow from the load back to the battery.

As soon as the output has reached its setpoint, the control forces PWM mode for about  $85\mu s$  to allow all internal control circuits to calibrate.

| Symbol             | Description                            | Value (μs) |                |      |

|--------------------|----------------------------------------|------------|----------------|------|

| t <sub>SSDLY</sub> | Time from EN to sta<br>soft-start ramp | art of     | 25             |      |

| +                  | V <sub>OUT</sub> ramp start to Opt 06  |            | 16 +(VSEL-0.7) | X 53 |

| t <sub>REG</sub>   | regulation                             | Others     | (VSEL-0.1) X   | 53   |

| t <sub>POK</sub>   | PWROK (CONTRO                          | )L2[5])    | 11             |      |

| t <sub>CAL</sub>   | Regulator stays in PWM                 |            | 10             |      |

Table 2. Soft-Start Timing (see Figure 35)

Figure 35. Soft-start Timing

| V        | VSEL Value VOUT  |          |                  |                  |                  |  |  |  |  |  |

|----------|------------------|----------|------------------|------------------|------------------|--|--|--|--|--|

| Dec      | Binary           | Hex      | 00, 03           | 02               | 06               |  |  |  |  |  |

| 0        | 000000           | 00       | 0.7500           | 0.7500           | 1.1875           |  |  |  |  |  |

| 1        | 000001           | 01       | 0.7625           | 0.7625           | 1.2000           |  |  |  |  |  |

| 2        | 000010           | 02       | 0.7750           | 0.7750           | 1.2125           |  |  |  |  |  |

| 3        | 000011           | 03       | 0.7875           | 0.7875           | 1.2250           |  |  |  |  |  |

| 4        | 000100           | 04       | 0.8000           | 0.8000           | 1.2375           |  |  |  |  |  |

| 5        | 000101           | 05       | 0.8125           | 0.8125           | 1.2500           |  |  |  |  |  |

| 6        | 000110           | 06       | 0.8250           | 0.8250           | 1.2625           |  |  |  |  |  |

| 7        | 000111           | 07       | 0.8375           | 0.8375           | 1.2750           |  |  |  |  |  |

| 8        | 001000           | 80       | 0.8500           | 0.8500           | 1.2875           |  |  |  |  |  |

| 9        | 001001           | 09       | 0.8625           | 0.8625           | 1.3000           |  |  |  |  |  |

| 10       | 001010           | 0A<br>0B | 0.8750<br>0.8875 | 0.8750<br>0.8875 | 1.3125<br>1.3250 |  |  |  |  |  |

| 12       | 001011           | 0C       | 0.8675           | 0.8875           | 1.3375           |  |  |  |  |  |

| 13       | 001101           | 0D       | 0.9000           | 0.9000           | 1.3500           |  |  |  |  |  |

| 14       | 001101           | 0E       | 0.9250           | 0.9250           | 1.3625           |  |  |  |  |  |

| 15       | 001111           | 0F       | 0.9375           | 0.9375           | 1.3750           |  |  |  |  |  |

| 16       | 010000           | 10       | 0.9500           | 0.9500           | 1.3875           |  |  |  |  |  |

| 17       | 010001           | 11       | 0.9625           | 0.9625           | 1.4000           |  |  |  |  |  |

| 18       | 010001           | 12       | 0.9750           | 0.9750           | 1.4125           |  |  |  |  |  |

| 19       | 010011           | 13       | 0.9875           | 0.9875           | 1.4250           |  |  |  |  |  |

| 20       | 010100           | 14       | 1.0000           | 1.0000           | 1.4375           |  |  |  |  |  |

| 21       | 010101           | 15       | 1.0125           | 1.0125           | 1.4500           |  |  |  |  |  |

| 22       | 010110           | 16       | 1.0250           | 1.0250           | 1.4625           |  |  |  |  |  |

| 23       | 010111           | 17       | 1.0375           | 1.0375           | 1.4750           |  |  |  |  |  |

| 24       | 011000           | 18       | 1.0500           | 1.0500           | 1.4875           |  |  |  |  |  |

| 25       | 011001           | 19       | 1.0625           | 1.0625           | 1.5000           |  |  |  |  |  |

| 26       | 011010           | 1A       | 1.0750           | 1.0750           | 1.5125           |  |  |  |  |  |

| 27       | 011011           | 1B       | 1.0875           | 1.0875           | 1.5250           |  |  |  |  |  |

| 28       | 011100           | 1C       | 1.1000           | 1.1000           | 1.5375           |  |  |  |  |  |

| 29       | 011101           | 1D       | 1.1125           | 1.1125           | 1.5500           |  |  |  |  |  |

| 30       | 011110           | 1E       | 1.1250           | 1.1250           | 1.5625           |  |  |  |  |  |

| 31       | 011111           | 1F       | 1.1375           | 1.1375           | 1.5750           |  |  |  |  |  |

| 32       | 100000           | 20       | 1.1500           | 1.1500           | 1.5875           |  |  |  |  |  |

| 33       | 100001           | 21       | 1.1625           | 1.1625           | 1.6000           |  |  |  |  |  |

| 34       | 100010           | 22       | 1.1750           | 1.1750           | 1.6125           |  |  |  |  |  |

| 35<br>36 | 100011           | 23       | 1.1875<br>1.2000 | 1.1875<br>1.2000 | 1.6250<br>1.6375 |  |  |  |  |  |

| 37       | 100100           | 25       | 1.2125           | 1.2125           | 1.6500           |  |  |  |  |  |

| 38       | 100101           | 26       | 1.2250           | 1.2250           | 1.6625           |  |  |  |  |  |

| 39       | 100111           | 27       | 1.2375           | 1.2375           | 1.6750           |  |  |  |  |  |

| 40       | 101000           | 28       | 1.2500           | 1.2500           | 1.6875           |  |  |  |  |  |

| 41       | 101001           | 29       | 1.2625           | 1.2625           | 1.7000           |  |  |  |  |  |

| 42       | 101010           | 2A       | 1.2750           | 1.2750           | 1.7125           |  |  |  |  |  |

| 43       | 101011           | 2B       | 1.2875           | 1.2875           | 1.7250           |  |  |  |  |  |

| 44       | 101100           | 2C       | 1.3000           | 1.3000           | 1.7375           |  |  |  |  |  |

| 45       | 101101           | 2D       | 1.3125           | 1.3125           | 1.7500           |  |  |  |  |  |

| 46       | 101110           | 2E       | 1.3250           | 1.3250           | 1.7625           |  |  |  |  |  |

| 47       | 101111           | 2F       | 1.3375           | 1.3375           | 1.7750           |  |  |  |  |  |

| 48       | 110000           | 30       | 1.3500           | 1.3500           | 1.7875           |  |  |  |  |  |

| 49       | 110001           | 31       | 1.3625           | 1.3625           | 1.8000           |  |  |  |  |  |

| 50       | 110010           | 32       | 1.3750           | 1.3750           | 1.8125           |  |  |  |  |  |

| 51       | 110011           | 33       | 1.3875           | 1.3875           | 1.8250           |  |  |  |  |  |

| 52       | 110100           | 34       | 1.4000           | 1.4000           | 1.8375           |  |  |  |  |  |

| 53       | 110101           | 35       | 1.4125           | 1.4125           | 1.8500           |  |  |  |  |  |

| 54       | 110110           | 36       | 1.4250           | 1.4250           | 1.8625           |  |  |  |  |  |

| 55       | 110111           | 37       | 1.4375           | 1.4375           | 1.8750           |  |  |  |  |  |

| 56       | 111000           | 38       | 1.4500           | 1.4375           | 1.8875           |  |  |  |  |  |

| 57       | 111001           | 39       | 1.4625           | 1.4375<br>1.4375 | 1.9000           |  |  |  |  |  |

| 58<br>59 | 111010<br>111011 | 3A<br>3B | 1.4750<br>1.4875 | 1.4375           | 1.9125<br>1.9250 |  |  |  |  |  |

| 60       | 1111011          | 3C       | 1.5000           | 1.4375           | 1.9375           |  |  |  |  |  |

| 61       | 111101           | 3D       | 1.5125           | 1.4375           | 1.9500           |  |  |  |  |  |

| 62       | 111110           | 3E       | 1.5250           | 1.4375           | 1.9625           |  |  |  |  |  |

| 63       | 111111           | 3F       | 1.5375           | 1.4375           | 1.9750           |  |  |  |  |  |

|          |                  |          |                  |                  |                  |  |  |  |  |  |

| VS  | EL  |                  |   | VS         | EL  | 1                |

|-----|-----|------------------|---|------------|-----|------------------|

| Dec | Hex | VOUT             | ı | Dec        | Hex | VOUT             |

| 0   | 00  | 0.1000           |   | 64         | 00  | 1.1875           |

| 1   | 01  | 0.1250           |   | 65         | 01  | 1.2000           |

| 2   | 02  | 0.1500           |   | 66         | 02  | 1.2125           |

| 3   | 03  | 0.1750           |   | 67         | 03  | 1.2250           |

| 4   | 04  | 0.2000           |   | 68         | 04  | 1.2375           |

| 5   | 05  | 0.2250           |   | 69         | 05  | 1.2500           |

| 6   | 06  | 0.2500           |   | 70         | 06  | 1.2625           |

| 7   | 07  | 0.2750           |   | 71         | 07  | 1.2750           |

| 8   | 08  | 0.3000           |   | 72         | 08  | 1.2875           |

| 9   | 09  | 0.3250           |   | 73         | 09  | 1.3000           |

| 10  | 0A  | 0.3500           |   | 74         | 0A  | 1.3125           |

| 11  | 0B  | 0.3750           |   | 75         | 0B  | 1.3250           |

| 12  | 0C  | 0.4000           |   | 76         | 0C  | 1.3375           |

| 13  | 0D  | 0.4250           |   | 77         | 0D  | 1.3500           |

| 14  | 0E  | 0.4500           |   | 78         | 0E  | 1.3625           |

| 15  | 0F  | 0.4750           |   | 79         | 0F  | 1.3750           |

| 16  | 10  | 0.5000           |   | 80         | 10  | 1.3875           |

| 17  | 11  | 0.5250           |   | 81         | 11  | 1.4000           |

| 18  | 12  | 0.5500           |   | 82         | 12  | 1.4125           |

| 19  | 13  | 0.5750           |   | 83         | 13  | 1.4250           |

| 20  | 14  | 0.6000           |   | 84         | 14  | 1.4375           |

| 21  | 15  | 0.6250           |   | 85         | 15  | 1.4500           |

| 22  | 16  | 0.6500           |   | 86         | 16  | 1.4625           |

| 23  | 17  | 0.6750           |   | 87         | 17  | 1.4750           |

| 24  | 18  | 0.6875           |   | 88         | 18  | 1.4875           |

| 25  | 19  | 0.7000           |   | 89         | 19  | 1.5000           |

| 26  | 1A  | 0.7000           |   | 90         | 1A  | 1.5125           |

| 27  | 1B  | 0.7123           |   | 91         | 1B  | 1.5250           |

| 28  | 1C  | 0.7250           |   | 92         | 1C  | 1.5375           |

| 29  | 1D  |                  |   | 93         | 1D  | 1.5500           |

| 30  | 1E  | 0.7500<br>0.7625 |   | 93         | 1E  | 1.5625           |

| 31  | 1F  | 0.7623           |   | 95         | 1F  | 1.5750           |

| 32  | 20  | 0.7750           |   | 96         | 20  | 1.5875           |

| 33  | 21  | 0.8000           |   | 97         | 21  | 1.6000           |

| 34  | 22  | 0.8125           |   | 98         | 22  | 1.6125           |

| 35  | 23  | 0.8123           |   | 99         | 23  | 1.6250           |

| 36  | 24  | 0.8375           |   | 100        | 24  | 1.6375           |

| 37  | 25  | 0.8500           |   | 101        | 25  | 1.6500           |

| 38  | 26  | 0.8625           |   | 101        | 26  | 1.6625           |

| 39  | 27  | 0.8750           |   | 103        | 27  | 1.6750           |

| 40  | 28  | 0.8875           |   | 103        | 28  | 1.6875           |

| 41  | 29  | 0.9000           |   | 105        | 29  | 1.7000           |

| 42  | 2A  | 0.9000           |   | 103        | 2A  | 1.7125           |

| 42  | 2B  | 0.9125           |   | 106        | 2B  | 1.7125           |

| 43  | 2B  | 0.9250           |   | 107        | 2B  | 1.7375           |

| 45  | 2D  | 0.9500           |   | 108        | 2D  | 1.7500           |

| 46  | 2E  | 0.9500           |   | 110        | 2E  | 1.7500           |

| 46  | 2F  | 0.0020           |   |            | 2F  | 1.7750           |

|     | _   | 0.9750           |   | 111        |     |                  |

| 48  | 30  | 0.9875           |   | 112<br>113 | 30  | 1.7875           |

| 50  | 32  | 1.0000<br>1.0125 |   | 114        | 32  | 1.8000<br>1.8125 |

|     | 33  |                  |   |            |     |                  |

| 51  |     | 1.0250<br>1.0375 |   | 115        | 33  | 1.8250<br>1.8375 |

| 52  | 34  |                  |   | 116        | 35  |                  |

| 53  | 35  | 1.0500           |   | 117        |     | 1.8500<br>1.8625 |

| 54  | 36  | 1.0625           |   | 118        | 36  |                  |

| 55  | 37  | 1.0750           |   | 119        | 37  | 1.8750           |

| 56  | 38  | 1.0875           |   | 120        | 38  | 1.8875           |

| 57  | 39  | 1.1000           |   | 121        | 39  | 1.9000           |

| 58  | 3A  | 1.1125           |   | 122        | 3A  | 1.9125           |

| 59  | 3B  | 1.1250           |   | 123        | 3B  | 1.9250           |

| 60  | 3C  | 1.1375           |   | 124        | 3C  | 1.9375           |

| 61  | 3D  | 1.1500           |   | 125        | 3D  | 1.9500           |

| 62  | 3E  | 1.1625           |   | 126        | 3E  | 1.9625           |

| 63  | 3F  | 1.1750           |   | 127        | 3F  | 1.9750           |

Table 3. VSEL vs. VOUT for Options 00, 02, 03, 06

#### **Software Enable**

The EN\_DCDC bit, VSELx[7] can be used to enable the regulator in conjunction with the EN pin. Setting EN\_DCDC with EN HIGH begins the soft-start sequence described above.

| EN_DCDC Bit | EN Pin | I <sup>2</sup> C | REGULATOR |

|-------------|--------|------------------|-----------|

| 0           | 0      | OFF              | OFF       |

| 1           | 1      | ON               | ON        |

| 1           | 0      | OFF              | OFF       |

| 0           | 1      | ON               | OFF       |

Table 5. EN\_DCDC Behavior

#### **Light-Load (PFM) Operation**

The FAN5355 offers both a Normal PFM (NPFM) and Enhanced PFM (EPFM) mode. NPFM is normally used when the load current is very low and when quiescent current must be minimized. EPFM provides more accurate DC regulation and limits the minimum frequency to 25kHz typical to prevent operation in the audio band.

V<sub>OUT</sub> ripple is identical in both modes (less than 20mV), and both modes feature very fast response to load transients.

The FAN5355 incorporates a single-pulse, light-load modulation that ensures:

- Smooth transitions between PFM and PWM modes

- Minimum frequency, of 25kHz typical, to avoid audible noise (EPFM only)

- Single-pulse operation for low ripple

- Predictable PFM entry and exit currents.

PFM begins after the inductor current has become discontinuous, crossing zero during the PWM cycle in 32 consecutive cycles. PFM exit occurs when discontinuous current mode (DCM) operation cannot supply sufficient current to maintain regulation. During PFM mode, the inductor current ripple is about 40% higher than in PWM mode. The load current required to exit PFM mode is thereby about 20% higher than the load current required to enter PFM mode, providing sufficient hysteresis to prevent "mode chatter."

While PWM ripple voltage is typically less than 4mVP-P, PFM ripple voltage can be up to 30mVP-P during very light load. To prevent significant undershoot when a load transient occurs, the initial DC setpoint for the regulator in PFM mode is set 10mV higher than in PWM mode. This offset decays to about 5mV after the regulator has been in PFM mode for  $\sim 100 \, \mu s$ . The maximum instantaneous voltage in PFM is 30mV above the setpoint.

In Enhanced PFM (EPFM) mode, the regulator maintains a minimum frequency of 25kHz (typical) to prevent audible noise being generated by the external components. To achieve this, the regulator turns on the low-side MOSFET to

"create demand" for a pulse if no pulse had been required for  $40\mu s$ . The minimum frequency limit circuit takes effect with load currents below about 3.5mA. Above that load point, the natural PFM period is less than  $40\mu s$ . This circuit only activates when  $I_{LOAD}$  is greater than ~3.5mA. If the load remains above 3.5mA, there is no quiescent current penalty for EPFM mode and there is some accuracy advantage.

NPFM allows the switching frequency ( $f_{SW}$ ) to go as low as required to support the load current. This achieves a lower quiescent current than EPFM, but sacrifices up to  $\pm 15 \text{mV}$  of DC accuracy when compared to EPFM or PWM modes. As shown in Table 6, EPFM and NPFM modes have the same frequency when the load is above 4mA. If the load is above 4mA, EPFM is the preferred mode, since it has tighter DC regulation with the same efficiency.

EPFM can only be enabled by setting the MODE\_CTRL bits to 11. In versions with MODE\_CTRL disabled (see *Table 12*), the PFM mode is NPFM.

| Mode                                                    | EPFM     | NPFM     |  |  |

|---------------------------------------------------------|----------|----------|--|--|

| I <sub>QUIESCENT</sub> typical at I <sub>LOAD</sub> = 0 | 110μΑ    | 38μΑ     |  |  |

| DC Accuracy                                             | Better   | Good     |  |  |

| f <sub>SW</sub> at I <sub>LOAD</sub> = 0                | 25 kHz   | to 0 Hz  |  |  |

| f <sub>SW</sub> at I <sub>LOAD</sub> > 3.5mA            | > 33 kHz | > 33 kHz |  |  |

**Table 6. PFM Modes Comparison**

PFM mode can be disabled by writing to the mode control bits: CONTROL1[3:0] (see Table 12 for details).

# Switching Frequency Control and Synchronization

The nominal internal oscillator frequency is 3MHz. The regulator runs at its internal clock frequency until these conditions are met:

- 1. EN\_SYNC bit, CONTROL1[5], is set; and

- 2. A valid frequency appears on the SYNC pin.

| CON      | CONTROL2                  |      |      | d    |  |

|----------|---------------------------|------|------|------|--|

| PLL_MULT | f <sub>SYNC</sub> Divider | Min. | Тур. | Max. |  |

| 00       | 1                         | 2.25 | 3.00 | 4.00 |  |

| 01       | 2                         | 1.13 | 1.50 | 2.00 |  |

| 10       | 3                         | 0.75 | 1.00 | 1.33 |  |

| 11       | 4                         | 0.56 | 0.75 | 1.00 |  |

Table 7. SYNC Frequency Validation for fosc(INTERNAL)=3.0MHz

If the EN\_SYNC is set and SYNC fails validation, the regulator continues to run at its internal oscillator frequency. The regulator is functional if  $f_{\text{SYNC}}$  is valid, as defined in Table 7, but its performance is compromised if  $f_{\text{SYNC}}$  is outside the  $f_{\text{SYNC}}$  window in the Electrical Specifications.

When CONTROL1[3:2] = 00 and the VSEL line is LOW, the converter operates according to the MODE0 bit, CONTROL1[0], with synchronization disabled regardless of the state of the EN\_SYNC and HW\_nSW bits.

### **Output Voltage Transitions**

The IC regulates  $V_{OUT}$  to one of two setpoint voltages, as determined by the VSEL pin and the HW\_nSW bit.

| VSEL Pin | HW_nSW Bit | V <sub>OUT</sub> Setpoint <sup>(14)</sup> | PFM       |

|----------|------------|-------------------------------------------|-----------|

| 0        | 1          | VSEL0                                     | Allowed   |

| 1        | 1          | VSEL1                                     | Per MODE1 |

| х        | 0          | VSEL1                                     | Per MODE1 |

Table 8.  $V_{OUT}$  Setpoint and Mode Control MODE\_CTRL, CONTROL1[3:2] = 00

#### Note:

Option 07 uses VSELx[6:0] to set V<sub>OUT</sub>, while all other options use VSELx[5:0].

If HW\_nSW =0,  $V_{OUT}$  transitions are initiated through the following sequence:

- Write the new setpoint in VSEL1.

- Write desired transition rate in DEFSLEW, CONTROL2[2:0], and set the GO bit in CONTROL2[7].

If HW\_nSW =1, V<sub>OUT</sub> transitions are initiated either by changing the state of the VSEL pin or by writing to the VSEL register selected by the VSEL pin.

#### **Positive Transitions**

When transitioning to a higher  $V_{OUT}$ , the regulator can perform the transition using multi-step or single-step mode.

#### Multi-step Mode:

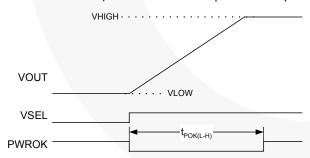

The internal DAC is stepped at a rate defined by DEFSLEW, CONTROL2[2:0], ranging from 000 to 110. This mode minimizes the current required to charge  $C_{\text{OUT}}$  and thereby minimizes the current drain from the battery when transitioning. The PWROK bit, CONTROL2[5], remains LOW until about 1.5 $\mu$ s after the DAC completes its ramp.

Figure 36. Multi-step V<sub>OUT</sub> Transition

#### Single-step Mode:

Used if DEFSLEW, CONTROL2[2:0] = 111. The internal DAC is immediately set to the higher voltage and the regulator performs the transition as quickly as its current limit circuit allows, while avoiding excessive overshoot.

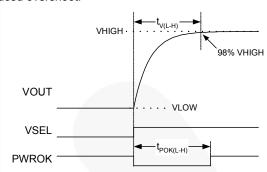

Figure 37 shows single-step transition timing.  $t_{\text{V(L-H)}}$  is the time it takes the regulator to settle to within 2% of the new

setpoint and is typically  $7\mu s$  for a full-range transition (from 00000 to 11111 for 6-bit DAC options). The PWROK bit, CONTROL2[5], goes LOW until the transition is complete and  $V_{OUT}$  settled. This typically occurs ~ $2\mu s$  after  $t_{V(L-H)}$ .

It is good practice to reduce the load current before making positive VSEL transitions. This reduces the time required to make positive load transitions and avoids current–limit-induced overshoot.

Figure 37. Single-Step V<sub>OUT</sub> Transition

All positive  $V_{\text{OUT}}$  transitions inhibit PFM until the transition is complete, which occurs at the end of  $t_{\text{POK}(L-H)}$ .

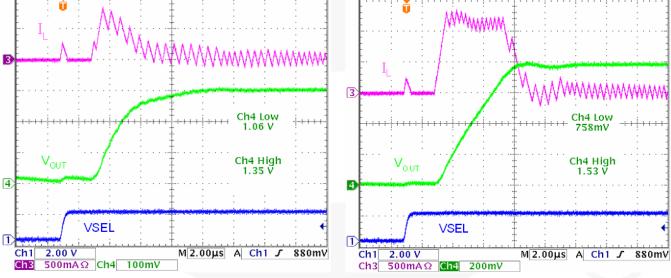

#### **Negative Transitions**

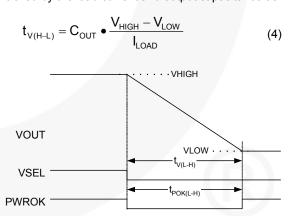

When moving from VSEL=1 to VSEL=0, the regulator enters PFM mode, regardless of the condition of the SYNC pin or MODE bits, and remains in PFM until the transition is completed. Reverse current through the inductor is blocked, and the PFM minimum frequency control inhibited, until the new setpoint is reached, at which time the regulator resumes control using the mode established by MODE\_CTRL. The transition time from  $V_{\text{HIGH}}$  to  $V_{\text{LOW}}$  is controlled by the load current and output capacitance as:

Figure 38. Negative V<sub>OUT</sub> Transition

#### **Protection Features**

#### **Current Limit / Auto-Restart**

The regulator includes cycle-by-cycle current limiting, which prevents the instantaneous inductor current from exceeding ~1350mA.

The IC enters "fault" mode after sustained over-current. If current limit is asserted for more than 32 consecutive cycles (about  $20\mu s$ ), the IC returns to shutdown state and remains in that condition for  $\sim\!80\mu s$ . After that time, the regulator attempts to restart with a normal soft-start cycle. If the fault has not cleared, it shuts down  $\sim\!10\mu s$  later.

If the fault is a short circuit, the initial current limit is  $\sim 30\%$  of the normal current limit, which produces a very small drain on the system power source.

#### **Thermal Protection**

When the junction temperature of the IC exceeds 150°C, the device turns off all output MOSFETs and remains in a low quiescent current state until the die cools to 130°C before commencing a normal soft-start cycle.

#### **Under-Voltage Lockout (UVLO)**

The IC turns off all MOSFETs and remains in a very low quiescent current state until  $V_{\text{IN}}$  rises above the UVLO threshold.

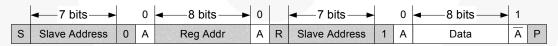

### I<sup>2</sup>C Interface

The FAN5355's serial interface is compatible with standard, fast, and HS mode  $\rm I^2C$  bus specifications. The FAN5355's SCL line is an input and its SDA line is a bi-directional opendrain output; it can only pull down the bus when active. The SDA line only pulls LOW during data reads and when signaling ACK. All data is shifted in MSB (bit 7) first.

SDA and SCL are normally pulled up to a system I/O power supply (VCCIO), as shown in Figure 1. If the I<sup>2</sup>C interface is not used, SDA and SCL should be tied to AVIN to minimize quiescent current consumption.

#### Addressing

FAN5355 has four user-accessible registers:

|          | Address |   |   |   |   |   |   |   |  |  |

|----------|---------|---|---|---|---|---|---|---|--|--|