(COG-VL248160)

DOCUMENT TITLE:

PRELIMINARY SPECIFICATION

OF

**LCD MODULE TYPE** MODEL NUMBER: COG-VL248160-02

| DEPARTMENT  | NAME         | SIGNATURE | DATE       |

|-------------|--------------|-----------|------------|

| PREPARED BY | PHILIP CHENG | A         | 2008-11-19 |

| CHECKED BY  | TIM WONG     | hh        | 2008/11/19 |

| APPROVED BY | CYRUS CHEUNG |           | 2008/11/19 |

|             |              |           |            |

DISTRIBUTION LIST: MARKETING

## VL-PS-COG-VL248160-02 REV.A (COG-VL248160) NOV/2008

PAGE 2 OF 12

| DOCUMENT<br>REVISION<br>FROM TO | DATE       | DESCRIPTION                                                         | CHANGED<br>BY   | CHECKEI<br>BY |

|---------------------------------|------------|---------------------------------------------------------------------|-----------------|---------------|

| A                               | 2008.11.19 | First Release. (Based on LCD counter drawing: COG-DEMO1003 (Rev.0)) | PHILIP<br>CHENG | TIM WON       |

|                                 |            |                                                                     |                 |               |

|                                 |            |                                                                     |                 |               |

|                                 |            |                                                                     |                 |               |

|                                 |            |                                                                     |                 |               |

|                                 |            |                                                                     |                 |               |

|                                 |            |                                                                     |                 |               |

VL-PS-COG-VL248160-02 REV.A (COG-VL248160) NOV/2008 PAGE 3 OF 12

## **CONTENTS**

Page No.

| 1.                             | GENERAL DESCRIPTION                                                                                                                  | 4                        |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| 2.                             | MECHANICAL SPECIFICATIONS                                                                                                            | 4                        |

| 3.                             | INTERFACE SIGNALS                                                                                                                    | 7                        |

| 4.<br>4.1<br>4.2               | ABSOLUTE MAXIMUM RATINGS<br>ELECTRICAL MAXIMUM RATINGS - FOR IC ONLY<br>ENVIRONMENTAL CONDITION                                      | 8<br>8<br>8              |

| 5.<br>5.1<br>5.2<br>5.3<br>5.4 | ELECTRICAL SPECIFICATIONS<br>TYPICAL ELECTRICAL CHARACTERISTICS<br>TIMING SPECIFICATIONS<br>POWER-UP SEQUENCE<br>POWER-DOWN SEQUENCE | 9<br>9<br>10<br>11<br>11 |

| 6.                             | LCD COSMETIC CONDITIONS                                                                                                              | 12                       |

| 7.                             | REMARK                                                                                                                               | 12                       |

VL-PS-COG-VL248160-02 REV.A (COG-VL248160) NOV/2008 PAGE 4 OF 12

## VARITRONIX LIMITED

## Preliminary Specification of LCD Module Type Model No.: COG-VL248160-02

## 1. General Description

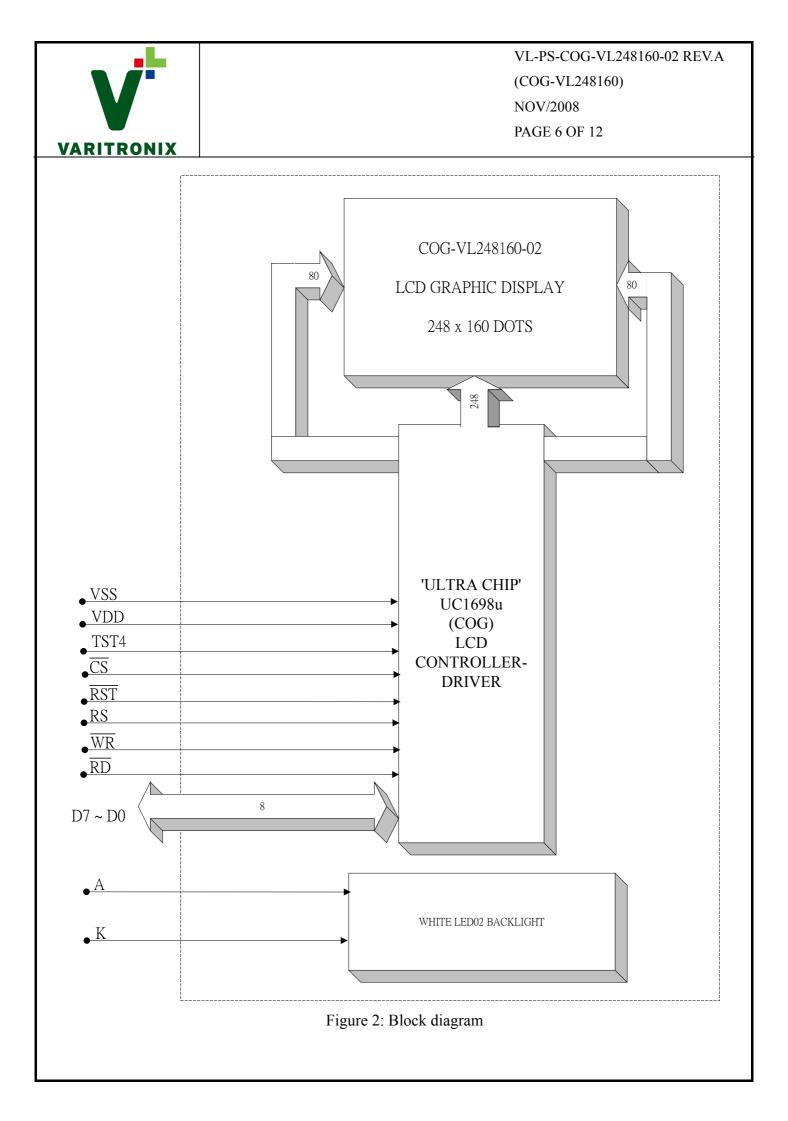

- 248x160 dots, FSTN, black & white, positive, transflective, LCD graphic module.

- Viewing angle: 12 o'clock.

- Driving scheme: 1/160 duty, 1/12 bias.

- 'ULTRA CHIP' UC1698u (COG) LCD controller-driver.

- 8-bit parallel bus (8080).

- Logic voltage: +3V.

- White LED02 backlight.

## 2. Mechanical Specifications

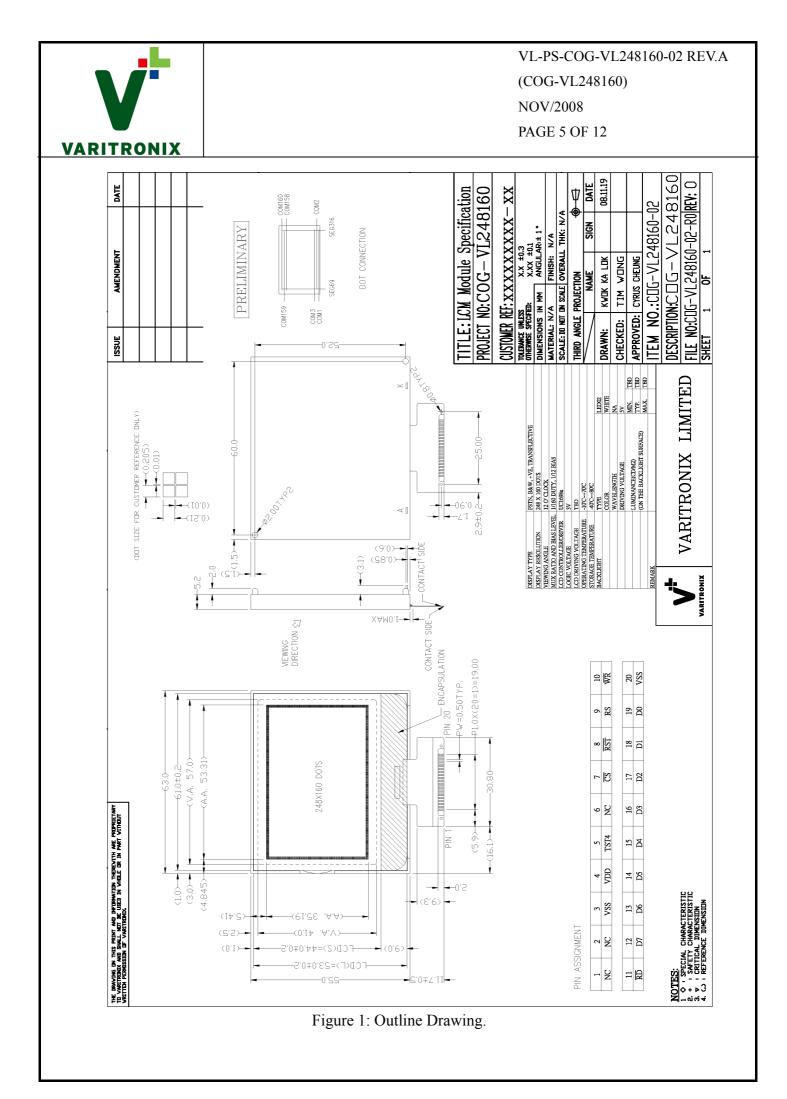

The mechanical detail is shown in Fig. 1 and summarized in Table 1 below.

|                    | Table 1                         |       |

|--------------------|---------------------------------|-------|

| Parameter          | Specifications                  | Unit  |

| Outline dimensions | 63.0(W) x 66.7(H) x 8.3(D)      | mm    |

| Viewing area       | 57.0(W) x 41.0(H)               | mm    |

| Active area        | 53.31(W) x 35.19(H)             | mm    |

| Display format     | 248(Horizontal) x 160(Vertical) | dots  |

| Dot size           | 0.205(W) x 0.21(H)              | mm    |

| Dot spacing        | 0.01(W) x 0.01(H)               | mm    |

| Dot pitch          | 0.215(W) x 0.22(H)              | mm    |

| Weight             | Approx. TBD                     | grams |

VL-PS-COG-VL248160-02 REV.A (COG-VL248160) NOV/2008 PAGE 7 OF 12

## 3. Interface signals

|         |        | Table 2                                                                                                                                                                                                                                                                                                                                                                               |

|---------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No. | Symbol | Description                                                                                                                                                                                                                                                                                                                                                                           |

| 1       | NC     | - No connection.                                                                                                                                                                                                                                                                                                                                                                      |

| 2       | NC     |                                                                                                                                                                                                                                                                                                                                                                                       |

| 3       | VSS    | Ground.                                                                                                                                                                                                                                                                                                                                                                               |

| 4       | VDD    | Power supply.                                                                                                                                                                                                                                                                                                                                                                         |

| 5       | TST4   | <ul> <li>Test control. This pin has on-chip pull-up resistor. Leave it open during normal operation.</li> <li>TST4 is also used as one of the high voltage power supply for MTP programming operation. For COG designs, please wire out TST4 with trace resistance between 30~50 Ω.</li> </ul>                                                                                        |

| 6       | NC     | No connection.                                                                                                                                                                                                                                                                                                                                                                        |

| 7       | CS     | $\overline{\text{CS}}$ (CS0). Chip Select. Chip is selected when $\overline{\text{CS}}$ = "L". When the chip is not selected, D[7:0] will be high impedance.                                                                                                                                                                                                                          |

| 8       | RST    | <ul> <li>RST(RST). When RST="L", all control registers are re-initialized by their default states. Since UC1698u has built-in Power-ON reset and software reset commands, RST pin is not required for proper chip operation.</li> <li>An RC Filter has been included on-chip. There is no need for external RC noise filter. When RST is not used, connect the pin to VDD.</li> </ul> |

| 9       | RS     | RS(CD). Select Control data or Display data for read/write operation.<br>"L": Control data "H": Display data                                                                                                                                                                                                                                                                          |

| 10      | WR     | $\overline{\text{RD}}$ , $\overline{\text{WR}}$ (WR[1:0]) controls the read/write operation of the host interface.                                                                                                                                                                                                                                                                    |

| 11      | RD     | WR(WR0):write.<br>RD (WR1):read.                                                                                                                                                                                                                                                                                                                                                      |

| 12      | D7     |                                                                                                                                                                                                                                                                                                                                                                                       |

| 13      | D6     |                                                                                                                                                                                                                                                                                                                                                                                       |

| 14      | D5     |                                                                                                                                                                                                                                                                                                                                                                                       |

| 15      | D4     | Di directional hus for norallel hest interface                                                                                                                                                                                                                                                                                                                                        |

| 16      | D3     | Bi-directional bus for parallel host interface.                                                                                                                                                                                                                                                                                                                                       |

| 17      | D2     | 7                                                                                                                                                                                                                                                                                                                                                                                     |

| 18      | D1     |                                                                                                                                                                                                                                                                                                                                                                                       |

| 19      | D0     | 7                                                                                                                                                                                                                                                                                                                                                                                     |

| 20      | VSS    | Ground.                                                                                                                                                                                                                                                                                                                                                                               |

| -       | А      | Anode of LED backlight.                                                                                                                                                                                                                                                                                                                                                               |

|         | K      | Cathode of LED backlight.                                                                                                                                                                                                                                                                                                                                                             |

VL-PS-COG-VL248160-02 REV.A (COG-VL248160) NOV/2008 PAGE 8 OF 12

## 4. Absolute Maximum Ratings

## 4.1 Electrical Maximum Ratings - for IC Only

|                                     | <u>Table 3</u> |      |         |      |

|-------------------------------------|----------------|------|---------|------|

| Parameter                           | Symbol         | Min. | Max.    | Unit |

| Supply voltage                      | VDD - VSS      | -0.3 | +4.0    | V    |

| LCD driving voltage(-25°C to +75°C) | VLCD           | -0.3 | +19.8   | V    |

| Digital input voltage               | Vin            | -0.4 | VDD+0.5 | V    |

Note:

1.) The modules may be destroyed if they are used beyond the absolute maximum ratings.

2.) VDD is based on VSS = 0V.

## 4.2 Environmental Condition

|                                                                                       |                                    | Table 4                                |                                              |       |        |  |

|---------------------------------------------------------------------------------------|------------------------------------|----------------------------------------|----------------------------------------------|-------|--------|--|

| Item                                                                                  | Operating<br>temperature<br>(Topr) |                                        | Storage<br>temperature<br>(Tstg)<br>(Note 1) |       | Remark |  |

|                                                                                       | Min.                               | Max.                                   | Min.                                         | Max.  |        |  |

| Ambient temperature                                                                   | -10°C                              | +70°C                                  | -40°C                                        | +80°C | Dry    |  |

| Humidity (Note 1)                                                                     |                                    | No                                     |                                              |       |        |  |

| framency (Note 1)                                                                     | < 50% RH for 4                     | condensation                           |                                              |       |        |  |

| Vibration (IEC 68-2-6)                                                                |                                    | Frequency: 10                          |                                              |       |        |  |

| cells must be mounted                                                                 |                                    | Amplitude: 0.75 mm                     |                                              |       |        |  |

| on a suitable connector                                                               | Dui                                | Duration: 20 cycles in each direction. |                                              |       |        |  |

| Shock (IEC 68-2-27)                                                                   | Pulse duration: 11 ms              |                                        |                                              |       |        |  |

| · · · · · · · · · · · · · · · · · · ·                                                 | Pe                                 |                                        | 3 directions                                 |       |        |  |

| Half-sine pulse shape<br>Number of shocks: 3 shocks in 3 mutually perpendicular axes. |                                    |                                        |                                              |       |        |  |

Note 1: Product cannot sustain at extreme storage conditions for long time.

VL-PS-COG-VL248160-02 REV.A (COG-VL248160) NOV/2008 PAGE 9 OF 12

## 5. Electrical Specifications

## 5.1 Typical Electrical Characteristics

At Ta = 25 °C, VDD=3V±5%, VSS=0V.

|                                         |                 | Table 5                                |         |      |        |                   |

|-----------------------------------------|-----------------|----------------------------------------|---------|------|--------|-------------------|

| Parameter                               | Symbol          | Conditions                             | Min.    | Тур. | Max.   | Unit              |

| Supply voltage<br>(Logic)               | VDD-VSS         |                                        | 2.85    | 3    | 3.15   | V                 |

|                                         |                 | Ta = -10 °C,<br>VDD=3V, Note 1         | -       | TBD  | -      | V                 |

| LCD driving voltage<br>(built-in)       | VLCD            | $Ta = +25^{\circ}C,$<br>VDD=3V, Note 1 | -       | TBD  | -      | V                 |

|                                         |                 | $Ta = +70^{\circ}C,$<br>VDD=3V, Note 1 | -       | TBD  | -      | V                 |

| Input logic HIGH                        | V <sub>IH</sub> |                                        | 0.8 VDD | -    | -      | V                 |

| Input logic LOW                         | $V_{IL}$        |                                        | -       | -    | 0.2VDD | V                 |

| Supply Current                          | IDD             | Character mode                         | -       | TBD  | -      | mA                |

| (Logic & LCD)                           | IDD             | Checker board mode                     | -       | TBD  | -      | mA                |

| Supply voltage of white LED02 backlight | VLED            | Forward current<br>=TBDmA              | -       | 5    | -      | V                 |

| Luminance(on the backlight surface)     |                 | Number of LED chips<br>=TBD            | -       | TBD  | -      | cd/m <sup>2</sup> |

Note 1: There is tolerance in optimum LCD driving voltage during production and it will be within the specified range.

## 5.2 Timing Specifications

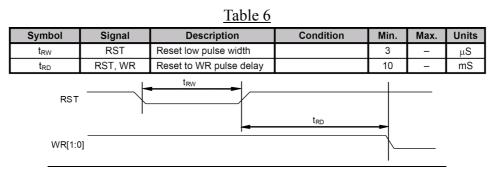

## 5.2.1 Reset Characteristics

At Ta =  $-10^{\circ}$ C to  $+70^{\circ}$ C, VDD= $3V\pm5\%$ , VSS = 0V

Refer to Fig. 3, the reset characteristics.

Figure 3: Reset characteristics.

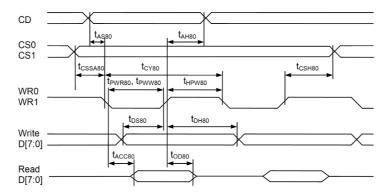

## 5.2.2 Parallel Bus Timing Characteristics (for 8080 MCU)

At Ta = -10°C to +70°C , VDD= $3V\pm5\%$ , VSS = 0V

Refer to Fig. 4, Parallel Bus Timing Characteristics (for 8080 MCU)

## Table 7

| Symbol                                    | Signal   | Description                                                                      | Condition              | Min.                    | Max.     | Units |

|-------------------------------------------|----------|----------------------------------------------------------------------------------|------------------------|-------------------------|----------|-------|

| t <sub>as80</sub><br>t <sub>ah80</sub>    | CD       | Address setup time<br>Address hold time                                          |                        | 0<br>0                  | -        | nS    |

| t <sub>CY80</sub>                         |          | System cycle time<br>16-bit bus (read)<br>(write)<br>8-bit bus (read)<br>(write) |                        | 170<br>130<br>100<br>80 | -        | nS    |

| t <sub>PWR80</sub>                        | WR1      | Pulse width 16-bit (read)<br>8-bit                                               |                        | 85<br>50                | -        | nS    |

| t <sub>PWW80</sub>                        | WR0      | Pulse width 16-bit (write)<br>8-bit                                              |                        | 65<br>40                | -        | nS    |

| t <sub>HPW80</sub>                        | WR0, WR1 | High pulse width<br>16-bit bus (read)<br>(write)<br>8-bit bus (read)<br>(write)  |                        | 85<br>65<br>50<br>40    | -        | nS    |

| t <sub>DS80</sub><br>t <sub>DH80</sub>    | D0~D15   | Data setup time<br>Data hold time                                                |                        | 30<br>0                 | -        | nS    |

| t <sub>ACC80</sub><br>t <sub>OD80</sub>   |          | Read access time<br>Output disable time                                          | C <sub>L</sub> = 100pF | -<br>15                 | 60<br>30 | nS    |

| T <sub>CSSA80</sub><br>t <sub>CSH80</sub> | CS1/CS0  | Chip select setup time                                                           |                        | 5<br>5                  |          | nS    |

Figure 4: Parallel Bus Timing Characteristics (for 8080 MCU)

VL-PS-COG-VL248160-02 REV.A (COG-VL248160) NOV/2008 PAGE 11 OF 12

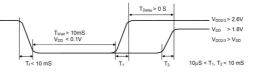

## 5.3 Power-Up Sequence

UC1698u power-up sequence is simplified by builtin "Power Ready" flags and the automatic invocation of *System-Reset* command after *Power-ON-Reset*.

System programmers are only required to wait 150 ms before the CPU starting to issue commands to UC1698u. No additional time sequences are required between enabling the charge pump, turning on the display drivers, writing to RAM or any other commands. However, while turning on VDD, VDD2/3 should be started not later than VDD.

Delay allowance between VDD and VDD2/3 is illustrated as Figure 7.

Figure 5: Reference Power-Up Sequence

## 5.4 Power-Down Sequence

To prevent the charge stored in capacitors CBX+, CBX–, and CL from damaging the LCD, when VDD is switched off, use Reset mode to enable the built-in draining circuit and discharge these capacitors.

The draining resistor is  $10K\Omega$  for both VLCD and VB+. It is recommended to wait 3 x RC for VLCD and 1.5 x RC for VB+. For example, if CL is 0.1uF, then the draining time required for VLCD is ~3mS.

When internal VLCD is not used, UC1698u will *NOT* drain VLCD during RESET. System designers need to make sure external VLCD source is properly drained off before turning off VDD.

Figure 6:Reference Power-Down Sequence

Figure 7: Delay allowance between VDD and VDD2/3

LCD is made up of glass, organic sealant, organic fluid and

When soldering DIL pins, avoid excessive heat and keep soldering temperature between 260°C to 300°C for no more than 5 seconds. Never use wave or

MDL's are assembled and adjusted with a high degree of orccision. Avoid excessive shocks and do not make any alterations or modifications. The following should be noted.

Do not tamper in any way with the tabs on the metal

Do not modify the PCB by drilling extra holes, changing its outline, moving its components or

polymer based polarizers. The following precautio be taken when handling:

Note: LCD size of the product is TBD.

### Remark

scrub hard.

reflow soldering

2.1 Mechanical Consideration

2. Liquid Crystal Display Modules (MDL)

(1)

(2)

(3)

(4)

(5)

(6)

(7) (8)

(1)

(2)

(3)

frame

1. Liquid Crystal Display (LCD)

### HANDLING LCD AND LCD MODULES

When mounting a MDL make sure that the PCB is not under any stress such as bending or twisting. Elastomer contacts are very delicate and missing pixels could result from slight dislocation of any of (4)the elements

- (5)

- the elements. Avoid pressing on the metal bezel, otherwise the elastomer connector could be deformed and lose contact, resulting in missing pixels. If FPCA need to be bent, please refer the suggested bending area on the specification. The stiffener and component area on FPC/FFC/COF must not be bent during or after assembly (Note: for those models with FPC/FFC/COF+stiffener). Sharp bending should be avoided on FPC to prevent

- Sharp bending should be avoided on FPC to prevent track cracking.

such devices should apply, namely:

- The operator should be grounded whenever he comes into contact with the module. Never touch any of the conductive parts such as the LSI pads, the copper leads on the PCB and the interface terminals with any part of the human body. The modules should be kept in antistatic bags or other containers resistant to static for storage. Only properly grounded soldering irons should be used.

- (3)

- (4)

- (5)

- (6)

### 2.3 Soldering

- Solder only to the I/O terminals. Use only soldering irons with proper grounding and (2)

- Soldering temperature is  $280^{\circ}C \pm 10^{\circ}C$  . (3)

- (6)

- Use entectic solder with resin flux fill. If flux is used, the LCD surface should be covered to avoid flux spatters. Flux residue should be removed afterwards. Use proper de-soldering methods (e.g. suction type desoldering irons) to remove lead wires from the I/O terminals when necessary. Do not repeat the soldering/desoldering process more than three times as the pads and plated through holes may be damaged. (7)

### 2.4 Label

obstructing the viewing area of display.

(COG-VL248160)

PAGE 12 OF 12

NOV/2008

### 3. Operation

The viewing angle can be adjusted by varying the LCD driving voltage Vo. Driving voltage should be kept within specified range excess voltage shoutens display life. Response time increases with decrease in temperatures. Display may turn black or dark Blue at temperatures above its operational ranse: this is however not (1)

VL-PS-COG-VL248160-02 REV.A

- (2) (3)

- (4)above its operational range; this is however not destructive and the display will return to normal once the temperature falls back to range.

- (5)

- the temperature tails back to range. Mechanical disturbance during operation (such as pressing on the viewing area) may cause the segments to appear "fractured". They will recover once the display is turned off. Condensation at terminals will cause malfunction and possible electrochemical reaction. Relative humidity of the environment should therefore be kept below 60%. (6) (7)

- Display performance may vary out of viewing area If there is any special requirement on performance out of viewing area, please consult Varitronix.

### 4. Storage and Reliability

- LCD's should be kept in sealed polyethylene bags while MDL's should use antistatic ones. If properly sealed, there is no need for desiccant. Store in dark places and do not expose to sunlight or (1)

- (2) fluorescent light. Keep the temperature between 0°C and 35°C and the relative humidity low. Please consult VARITRONIX for other storage

- requirements. Water con (3)

- (4)

- (5)

- requirements.

Water condensation will affect reliability performance of the display and is not allowed.

Semi-conductor device on the display is sensitive to light and should be protected properly.

Power up/down sequence.

a) Power Up: in general, LCD supply voltage, Vom must be supplied after logic voltage, VDD becomes steady. Please refer to related IC data sheet for details. sheet for details

- Power Down: in general, LCD supply voltage, Vo must be removed before logic voltage, VDD turns off. Please refer to related IC data b) eet for details

### 5. Safety

documents.

2.

3.

If any fluid leaks out of a damaged glass cell, wash off any human part that comes into contact with soap and water. Never swallow the fluid. The toxicity is extremely low but caution should be exercised at all times.

accordance with VARITRONIX LCD Acceptance Standards (copies available on request), for a period of one year from the date of shipment. Confirmation of such date shall be based on freight

No warranty can be granted if any of the precautions stated in HANDLING LCD and LCD Modules above have been disregarded. Broken glass, scratches on polarizers, mechanical damages as well as defects that are caused by accelerated environmental tests are excluded from warranty. In returning the LCD and Modules, they must be properly packaged and there should be detailed description of the failures or defects.

VARITRONIX LCDs and modules are not consumer products, but may be incorporated by VARITRONIX's customers into consumer products or components thereof. VARITRONIX does not warrant that its LCDs and components are fit for any such particular purpose.

The liability of VARITRONIX is limited to repair or replacement on the terms set forth below. VARITRONIX will not be responsible for any subsequent or consequential events or injury or damage to any personnel or user including third party personnel and/or user.

Unless otherwise agreed in writing between VARITRONIX and the customer, VARITRONIX will only replace or repair any of its LCD which is found defective electrically or visually when inspected in

### IMPORTANT NOTICE

LIMITED WARRANTY

The information presented in this document has been carefully checked and is believed to be accurate, however, no responsibility is assumed for inaccuracies. VARITRONIX reserves the right to make changes to any specifications without further notice for performance, reliability, production technique and other considerations, VARITRONIX does not assume any liability arising out of the application or use of products herein. Please see Limited Warranty in the previous continue to the previous section.

"Varitronix Limited reserves the right to change this specification."

Tel:(852) 2197-6000.

## Fax:(852) 2343-9555.

## URL:http://www.varitronix.com

- END -

6. LCD Cosmetic Conditions Refer to the document: TBD.

7.

# Keep the temperature within range for use and storage. Excessive temperature and humidity could cause polarization degredation, polarizer peel-off or bubble generation. When storage for a long period over 40° C is required, the relative humidity should be kept below 60%. Do not contact the exposed polarizers with anything harder than an HB pencil lead. To clean dust off the display surface, wipe gently with cotton, chamois or other soft material soaked in petroleum benzin. Never scrub hard. (7)other soft material soaked in petroleum benzin. Never scrub hard. Varitonix does not responsible for any polarizer defect after the protective film has been removed from the display Wipe off saliva or water drops immediately. Contact with water over a long period of time may cause polarizer deformation or color fading, while an active LCD with water condensation on its surface will cause corrosion of ITO electrodes. PETROLEUM BENZIN is recommended to remove adhesives used to attach front/rear polarizers and reflectors, while chemicals like acetone, toluene, ethanol and isopropyl alcohol will cause damage to the polarizer. Avoid oil and fats. Avoid lacquer and epoxies which might contain solvents and hardeners to cause electrode errosion. Some solvents will also soften the epoxy covering the DLL pins and thereby weakening the adhesion of the epoxy on glass. This will cause the exposed electrodes to erode electrochemically when operating in high humidity and condensing environment. Glass can be easily chipped or cracked from rough handling, especially at corners and edges. Do not drive LCD with DC voltage. When soldering DLL pins, avoid excessive heat and keen soldering DLL pins, avoid excessive heat and keen soldering the adhesion of excessive heat and 2.2 Static Electricity

MDL contains CMOS LSI's and the same precaution for

## (2)

- used. If an electric screwdriver is used it should be well grounded and shielded from commutator sparks. The normal static prevention measures should be observed for work clothes and working benches; for the latter conductive (nubber) mat is recommended. Since dry air is inductive to statics, a relative humidity of 50 60% is recommended.

- no leakage.

- Soldering time: 3 to 4 seconds. Use eutectic solder with resin flux fill.

Identification labels will be stuck on the module without