## Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application for written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics atta abooks, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU ROHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

The revision list can be viewed directly by clicking the title page.

The revision list summarizes the locations of revisions and additions. Details should always be checked by referring to the relevant text.

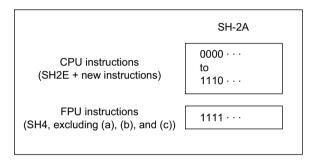

# SH-2A, SH2A-FPU

Software Manual Renesas 32-Bit RISC Microcomputer SuperH<sup>™</sup> RISC engine Family

Renesas Electronics

Rev.3.00 2005.07

#### Keep safety first in your circuit designs!

Renesas Technology Corp. puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage. Remember to give due consideration to safety when making your circuit designs, with appropriate

measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

#### Notes regarding these materials

- These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corp. product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corp. or a third party.

- 2. Renesas Technology Corp. assumes no responsibility for any damage, or infringement of any thirdparty's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- 3. All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corp. without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor for the latest product information before purchasing a product listed herein.

The information described here may contain technical inaccuracies or typographical errors. Renesas Technology Corp. assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

Please also pay attention to information published by Renesas Technology Corp. by various means, including the Renesas Technology Corp. Semiconductor home page (http://www.renesas.com).

- 4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corp. assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- 5. Renesas Technology Corp. semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- 6. The prior written approval of Renesas Technology Corp. is necessary to reprint or reproduce in whole or in part these materials.

- 7. If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

Any diversion or receiver technologies are subject to the ownert control lows and regulations of longe and/or the

Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

8. Please contact Renesas Technology Corp. for further details on these materials or the products contained therein.

## Main Revisions for this Edition

| Item                                                                                                        | Page | Revision (See Manual for Details)                                                                                                                                        |  |  |

|-------------------------------------------------------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1.1 Features                                                                                                | 1    | Description amended                                                                                                                                                      |  |  |

|                                                                                                             |      | The SH-2A/SH2A-FPU is a 32-bit RISC (reduced instruction set computer) microprocessor that is upward-compatible with the SH-1, SH-2, and SH-2E at the object code level. |  |  |

| 2.2.2 Control                                                                                               | 5    | Description amended                                                                                                                                                      |  |  |

| Registers<br>(1) Status Register,<br>SR                                                                     |      | (32-bit,initial value =0000 0000 0000 0000 00X0 00XX 1111 00XX)                                                                                                          |  |  |

|                                                                                                             | 10   | Note amended                                                                                                                                                             |  |  |

| 3.1.1 Exception<br>Handling Types and                                                                       | 16   |                                                                                                                                                                          |  |  |

| Priority                                                                                                    |      | Notes:1.Delayed branch instructions:JMP, JSR, BRA, BSR,RTS, RTE,BF/S, BT/S, BSRF, BRAF                                                                                   |  |  |

| Table 3.1 Exception<br>Types and Priority                                                                   |      |                                                                                                                                                                          |  |  |

| 3.1.2 Exception                                                                                             | 18   | Description amended                                                                                                                                                      |  |  |

| Handling Operation                                                                                          |      | ··· and the vector table address offset of the interrupt exception                                                                                                       |  |  |

| (2) Address Error,<br>RAM Error, Register<br>Bank Error, Interrupt,<br>or Instruction<br>Exception Handling |      | handling to be executed,                                                                                                                                                 |  |  |

| 3.3.1 Address Error                                                                                         | 22   | Table amended                                                                                                                                                            |  |  |

| Sources                                                                                                     |      | Bus Cycle Address Error                                                                                                                                                  |  |  |

| Table 3.5 Bus                                                                                               |      | Type Bus Master Bus Cycle Operation Occurrence                                                                                                                           |  |  |

| Cycles and Address                                                                                          |      | Data         CPU or         Double longword data accessed from double         No error (normal)           read/write         DMAC         longword boundary              |  |  |

| Errors                                                                                                      |      | Double longword data accessed from other Address error than double longword boundary                                                                                     |  |  |

| 3.6.3 Interrupt                                                                                             | 26   | Description amended                                                                                                                                                      |  |  |

| Exception Handling                                                                                          |      | ··· and the vector table address offset of the interrupt exception handling to be executed,···                                                                           |  |  |

| Item                                                          | Page | Revision (See Manual for Details)                                                                                                                                        |

|---------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.3 Instruction                                               | 45   | Table amended                                                                                                                                                            |

| Format                                                        |      | Instruction Formats                                                                                                                                                      |

| Table 4.8<br>Instruction Formats                              |      | nid format                                                                                                                                                               |

|                                                               |      | 32 16<br>xxxx nnnn xiii xxxx<br>15 0<br>xxxx dddd dddd dddd                                                                                                              |

| 5.1 Instruction Set                                           | 53   | Table amended                                                                                                                                                            |

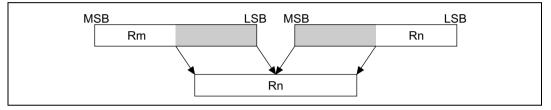

| by Classification                                             |      | Item Format Explanation                                                                                                                                                  |

| Table 5.2<br>Instruction Code<br>Format                       |      | Instruction<br>Rm: Source register<br>Rn: Destination register<br>imm: Immediate data<br>disp: Displacement*1                                                            |

| 5.1.1 Data Transfer                                           | 56   | Table amended                                                                                                                                                            |

| Instructions                                                  |      | MOVML.L @R15+,Rn                                                                                                                                                         |

| Table 5.3 Data                                                |      | MOVMU.L @R15+,Rn                                                                                                                                                         |

| Transfer Instructions                                         |      | Note: When Rn = R15, read Rn as PR                                                                                                                                       |

| 6.2 Format of                                                 | 76   | Description amended                                                                                                                                                      |

| Instruction                                                   |      | Register bank structure definition                                                                                                                                       |

| Descriptions                                                  |      | (VTO: Interrupt vector table address offset)                                                                                                                             |

| 6.3.30 RESBANK                                                | 145  | Note amended                                                                                                                                                             |

| REStore from<br>registerBANK<br>System Control<br>Instruction |      | <ul> <li>* 19 when a bank overflow has occurred and the register is<br/>restored from the stack</li> </ul>                                                               |

| 6.4.21 DT                                                     | 196  | Program listing amended                                                                                                                                                  |

| Decrement and Test<br>Arithmetic Instruction                  |      | DT R5                                                                                                                                                                    |

| 6.4.31 MOV                                                    | 219  | Description amended                                                                                                                                                      |

| MOVe immediate<br>data<br>Data Transfer<br>Instruction        |      | The PC points to the starting address of the fourth byte after this MOV instruction The PC points to the starting address of the fourth byte after this MOV instruction, |

| Item                                                                     | Page | Revision (See Manual for Details)                                                                                                    |

|--------------------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------|

| 6.4.48 RTE<br>ReTurn from<br>Exception<br>System Control<br>Instruction  | 244  | Description amended<br>Return from<br>Exception Handling Delayed Branch Instruction                                                  |

| 6.4.50 SETT                                                              | 248  | Description amended                                                                                                                  |

| SET T bit                                                                |      | T Bit Setting                                                                                                                        |

| System Control<br>Instruction                                            |      |                                                                                                                                      |

| 6.4.57 SLEEP                                                             | 257  | Description amended                                                                                                                  |

| SLEEP<br>System Control<br>Instruction                                   |      | Transition to Power-Down Mode                                                                                                        |

| 6.5.10 FLOAT                                                             | 296  | Description amended                                                                                                                  |

| Floating-point<br>convert from integer<br>Floating-Point<br>Instruction  |      | When FPSCR.enable.I = 1, and FPSCR.PR = 0, an FPU exception trap is generated regardless of whether or not an exception has occurred |

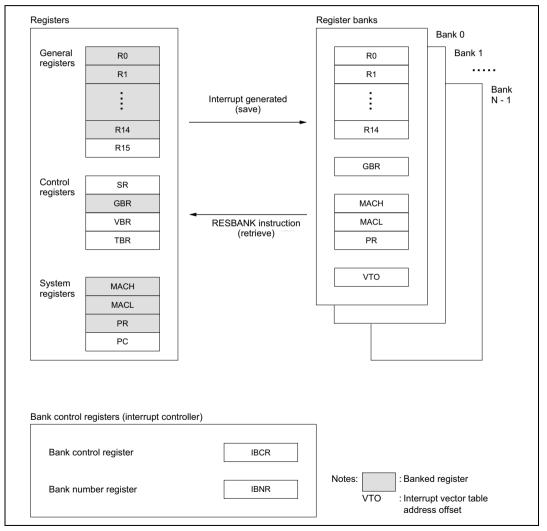

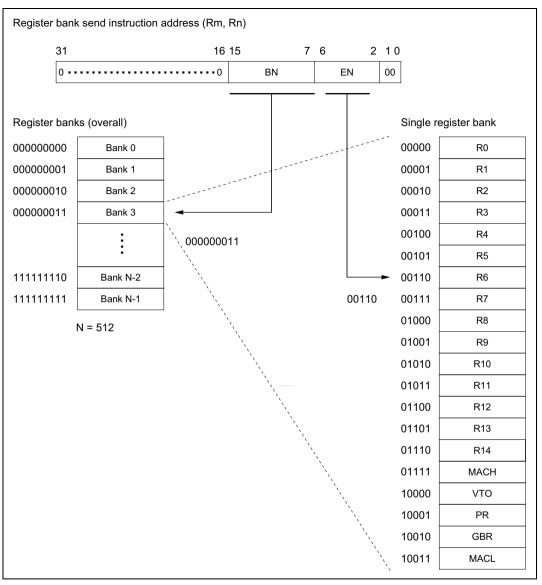

| 7.1 Overview                                                             | 325  | Figure amended                                                                                                                       |

| Figure 7.1 Overview                                                      | W    | (Before) $IVO \rightarrow (After) VTO$                                                                                               |

| of Register Bank<br>Configuration                                        |      | Figure notes amended                                                                                                                 |

| Configuration                                                            |      | VTO: Interrupt vector table address offset                                                                                           |

| 7.2.1 Banked Data                                                        | 326  | Description amended                                                                                                                  |

|                                                                          |      | $\cdots$ and the interrupt vector table address offsets (VTO) are banked.                                                            |

| 7.2.2 Register                                                           | 326  | Description amended                                                                                                                  |

| Banks                                                                    |      | ··· Register banks are stacked in first in last out (FILO) sequence.···                                                              |

| 7.2.3 Bank Control                                                       | 327  | Description amended                                                                                                                  |

| Registers                                                                |      | Bits 3 to 0: BN3 to BN0                                                                                                              |

| (2) Bank Number<br>Register (IBNR) (16<br>bit, Initial value:<br>H'0000) |      | after which the data is retrieved from the register bank. These bits are read-only and cannot be modified.                           |

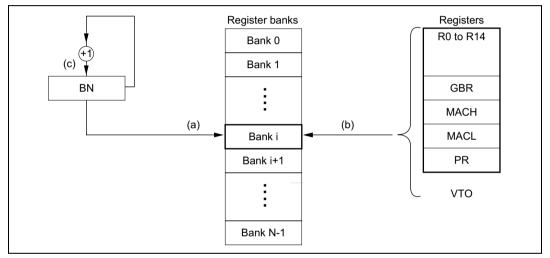

| 7.3.1 Save to Bank                                                       | 328  | Description amended                                                                                                                  |

|                                                                          |      | (b), and the interrupt vector table address offset (VTO) are saved to the bank indicated by the BN, bank i.                          |

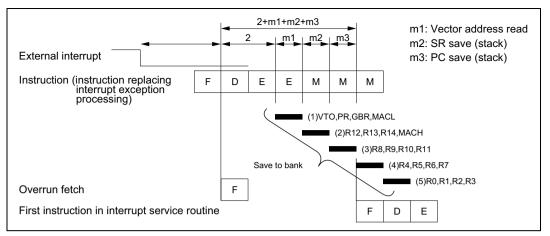

| Figure 7.2 Bank                                                          | 328, | Figure amended                                                                                                                       |

| Save Operations                                                          | 329  | (Before) $IVN \rightarrow (After) VTO$                                                                                               |

| Figure 7.3 Bank<br>Save Timing                                           |      |                                                                                                                                      |

Rev. 3.00 Jul 08, 2005 page v of xiv

| Item                                                                                    | Page | Revision (See Manual for Details)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------------------------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7.4.2 Register Bank                                                                     | 330  | Description amended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

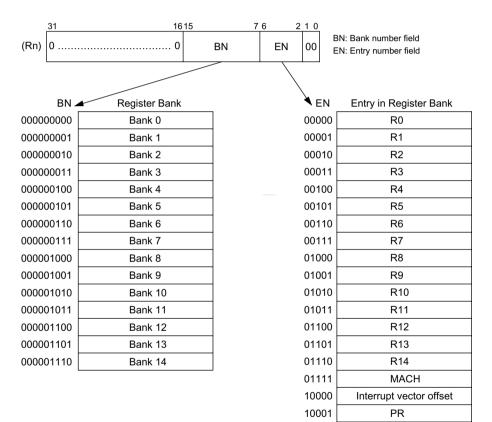

| Addressing                                                                              |      | ··· and the entry within the bank (R0 to R14, GBR, MACH, MACL, PR, VTO) is specified by address bits 6 to 2 (EN).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Figure 7.4 Register                                                                     | 331  | Figure amended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Bank Addressing                                                                         |      | (Before) $IVO \rightarrow (After) VTO$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

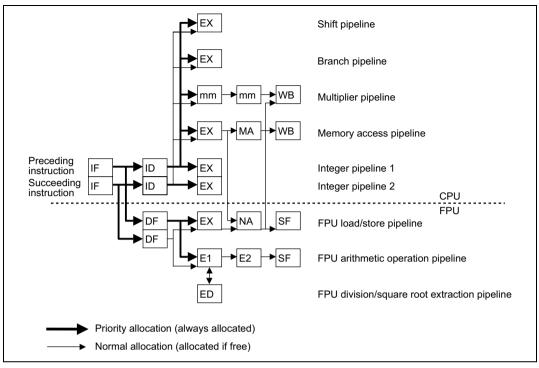

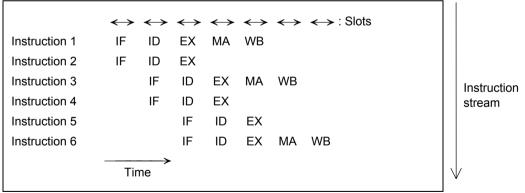

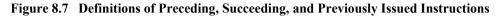

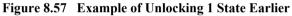

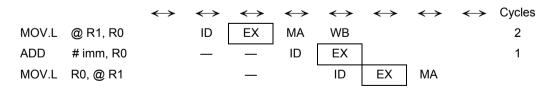

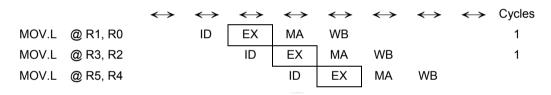

| 8.2 Slots and                                                                           | 339  | Figure amended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Pipeline Flow                                                                           |      | Instruction 1 IF ID EX MA WB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure 8.3<br>Impossible Pipeline<br>Flow (1)                                           |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

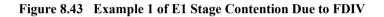

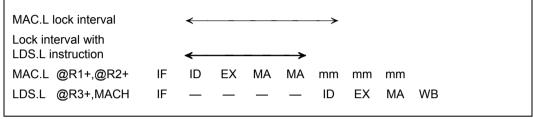

| 8.6 Contention Due                                                                      | 353  | Figure amended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| to FPU                                                                                  |      | (Before) $GX \rightarrow (After) EX$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Figure 8.36<br>Example of Use of<br>Result of Zero-<br>Latency Instruction<br>as Source |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

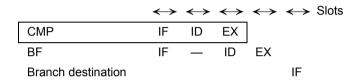

| 8.9 Pipeline                                                                            | 372  | Table amended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Operations for Each<br>Instruction                                                      |      | Type         Category         Number<br>of Stages         Execution<br>States         Latency         Contention         Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Table 8.1 Number                                                                        |      | System         MAC →         4         1         2         • These instructions use the         STS         MACH,Rn           control         register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| of Instruction Stages                                                                   |      | instructions instructions and instructio |

| and Execution States                                                                    |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Appendix A SH-                                                                          | 480, | Table amended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2A/SH2A-FPU<br>Parallel Execution                                                       | 481  | Classifi-<br>cation of<br>First Second     Instruction       Instruction     Instruction       MW     MW     STC.L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                         |      | EX EX SUBC Rm,Rn SUBV Rm,Rn TST ∰mm,R0<br>BR MR JSR/N @@(disp8,TBR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

## Contents

| Secti | on 1 (   | Overview                               | 1  |

|-------|----------|----------------------------------------|----|

| 1.1   | Feature  | S                                      | 1  |

|       |          |                                        |    |

| Secti | on 2 I   | Programming Model                      | 3  |

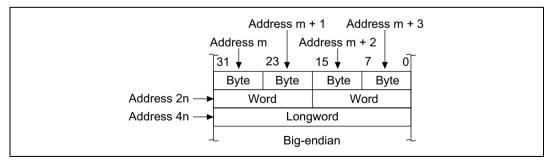

| 2.1   | Data Fo  | ormats                                 | 3  |

| 2.2   | Registe  | r Configuration                        | 3  |

|       | 2.2.1    | General Registers                      | 3  |

|       | 2.2.2    | Control Registers                      | 5  |

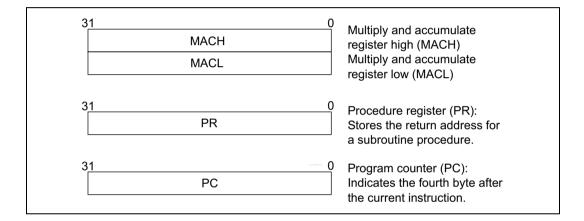

|       | 2.2.3    | System Registers                       | 6  |

|       | 2.2.4    | Floating-Point Registers               | 7  |

|       | 2.2.5    | Floating-Point System Registers        | 8  |

|       | 2.2.6    | Register Banks                         | 10 |

|       | 2.2.7    | Register Initial Values                | 10 |

| 2.3   | Data Fo  | ormats                                 | 11 |

|       | 2.3.1    | Data Format in Registers               | 11 |

|       | 2.3.2    | Data Formats in Memory                 | 11 |

|       | 2.3.3    | Immediate Data Format                  | 12 |

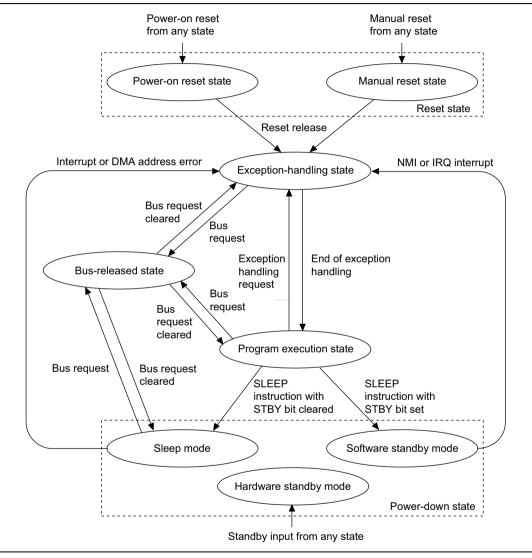

| 2.4   | Process  | ing States                             | 13 |

|       |          |                                        |    |

| Secti | on 3 I   | Exception Handling                     | 15 |

| 3.1   |          | 2W                                     | 15 |

|       | 3.1.1    | Exception Handling Types and Priority  | 15 |

|       | 3.1.2    | Exception Handling Operation           | 17 |

|       | 3.1.3    | Exception Vector Table                 | 18 |

| 3.2   | Resets.  | -                                      | 20 |

|       | 3.2.1    | Types of Reset                         | 20 |

|       | 3.2.2    | Power-On Reset                         | 20 |

|       | 3.2.3    | Manual Reset                           | 21 |

| 3.3   | Addres   | s Errors                               | 22 |

|       | 3.3.1    | Address Error Sources                  | 22 |

|       | 3.3.2    | Address Error Exception Handling       | 23 |

| 3.4   | RAM E    | Crrors                                 | 23 |

|       | 3.4.1    | RAM Error Sources                      | 23 |

|       | 3.4.2    | RAM Error Exception Handling           | 23 |

| 3.5   | Registe  | r Bank Errors                          | 24 |

|       | 3.5.1    | Register Bank Error Sources            | 24 |

|       | 3.5.2    | Register Bank Error Exception Handling | 24 |

| 3.6   | Interrur | ots                                    | 25 |

|       | 1        |                                        |    |

Rev. 3.00 Jul 08, 2005 page vii of xiv

|       | 3.6.1   | Interrupt Sources                             |                                | 25 |

|-------|---------|-----------------------------------------------|--------------------------------|----|

|       | 3.6.2   | Interrupt Priority                            |                                | 25 |

|       | 3.6.3   | Interrupt Exception Handling                  |                                | 26 |

| 3.7   | Instruc | tion Exceptions                               |                                | 27 |

|       | 3.7.1   | Types of Instruction Exception                |                                | 27 |

|       | 3.7.2   | Trap Instruction                              |                                | 28 |

|       | 3.7.3   | Slot Illegal Instructions                     |                                | 28 |

|       | 3.7.4   | General Illegal Instructions                  |                                | 29 |

|       | 3.7.5   | Integer Division Instructions                 |                                | 29 |

|       | 3.7.6   | Floating-Point Operation Instructions         |                                | 29 |

| 3.8   | Cases i | n Which Exceptions Are Not Accepted           |                                | 30 |

| 3.9   | Stack S | tatus after Exception Handling                |                                | 31 |

| 3.10  | Usage   | Notes                                         |                                | 32 |

|       | 3.10.1  | Stack Pointer (SP) Value                      |                                | 32 |

|       | 3.10.2  | Vector Base Register (VBR) Value              |                                | 32 |

|       | 3.10.3  | Address Errors Occurring in Address Error Exc | ception Handling Stacking      | 32 |

|       |         |                                               |                                |    |

| Secti | ion $4$ | Instruction Features                          |                                | 33 |

| 4.1   | RISC-7  | Sype Instruction Set                          |                                | 33 |

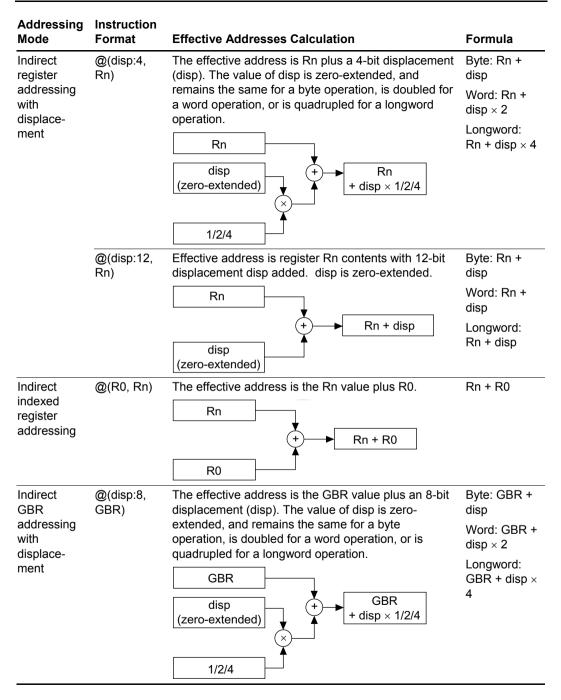

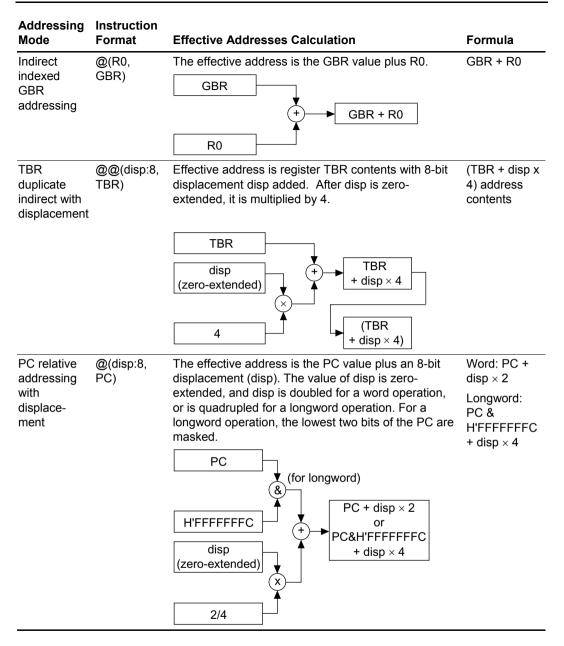

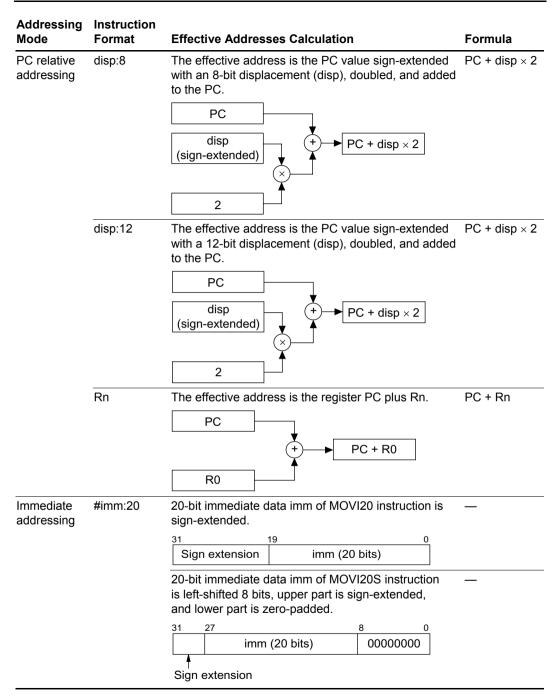

| 4.2   | Addres  | sing Modes                                    |                                | 37 |

| 4.3   | Instruc | tion Format                                   |                                | 41 |

|       |         |                                               |                                |    |

| Secti |         | Instruction Set                               |                                | 47 |

| 5.1   | Instruc | tion Set by Classification                    |                                | 47 |

|       | 5.1.1   | Data Transfer Instructions                    |                                | 54 |

|       | 5.1.2   | Arithmetic Operation Instructions             |                                | 58 |

|       | 5.1.3   | Logic Operation Instructions                  |                                | 61 |

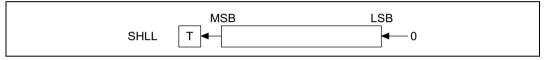

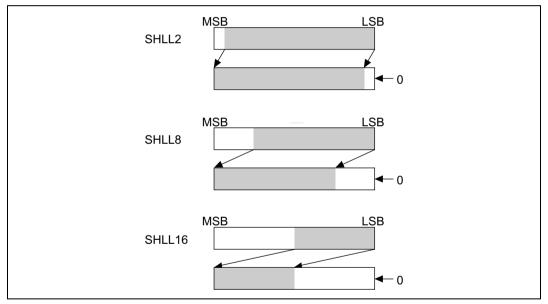

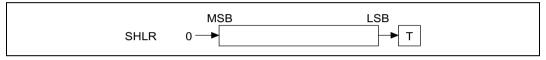

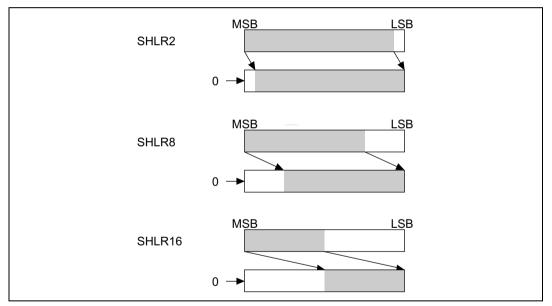

|       | 5.1.4   | Shift Instructions                            |                                | 62 |

|       | 5.1.5   | Branch Instructions                           |                                | 63 |

|       | 5.1.6   | System Control Instructions                   |                                | 64 |

|       | 5.1.7   | Floating-Point Instructions                   |                                | 66 |

|       | 5.1.8   | FPU-Related CPU Instructions                  |                                | 68 |

|       | 5.1.9   | Bit Manipulation Instructions                 |                                | 69 |

|       |         |                                               |                                |    |

| Secti |         | Instruction Descriptions                      |                                | 71 |

| 6.1   |         | ew of New Instructions                        |                                | 71 |

| 6.2   |         | of Instruction Descriptions                   |                                | 75 |

| 6.3   |         | structions                                    |                                | 88 |

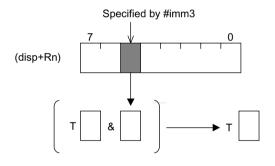

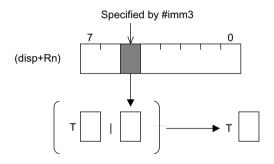

|       | 6.3.1   | BAND Bit AND                                  |                                | 88 |

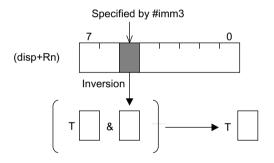

|       | 6.3.2   | BANDNOT Bit ANDNOT                            | -                              | 90 |

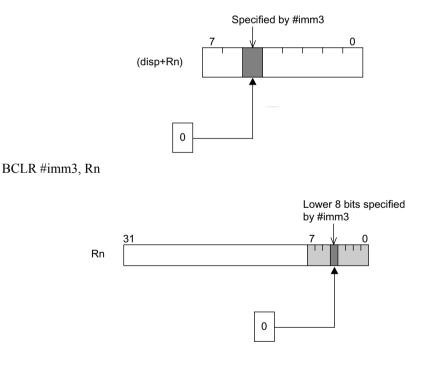

|       | 6.3.3   | BCLR Bit CLeaR                                | . Bit Manipulation Instruction | 92 |

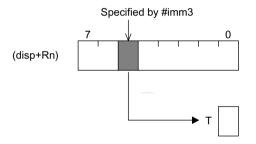

| 6.3.4  | BLD     | Bit LoaD                        | . Bit Manipulation Instruction | 94  |

|--------|---------|---------------------------------|--------------------------------|-----|

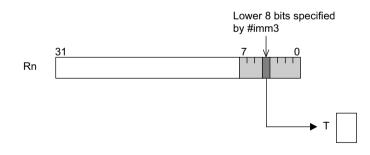

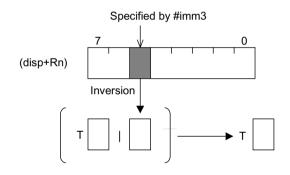

| 6.3.5  | BLDNOT  | Bit LoaDNOT                     | . Bit Manipulation Instruction | 96  |

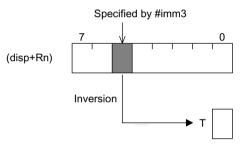

| 6.3.6  | BOR     | Bit OR                          | . Bit Manipulation Instruction | 98  |

| 6.3.7  | BORNOT  | Bit ORNOT                       | . Bit Manipulation Instruction | 100 |

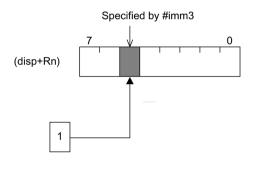

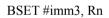

| 6.3.8  | BSET    | Bit SET                         | . Bit Manipulation Instruction | 102 |

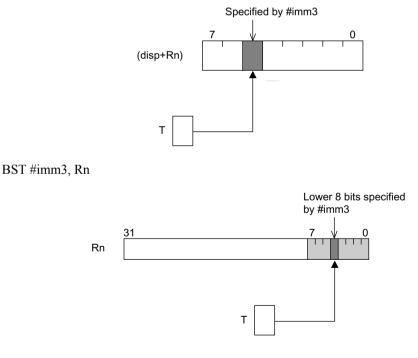

| 6.3.9  |         | Bit STore                       | -                              |     |

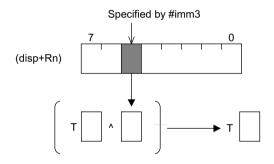

| 6.3.10 | BXOR    | Bit exclusive OR                | . Bit Manipulation Instruction | 106 |

| 6.3.11 |         | CLIP as Signed                  |                                |     |

| 6.3.12 |         | CLIP as Unsigned                |                                |     |

|        |         | DIVide as Signed                |                                |     |

|        |         | DIVide as Unsigned              |                                |     |

| 6.3.15 | FMOV    | Floating-point MOVe             | . Floating-Point Instruction   | 115 |

| 6.3.16 | JSR/N   | Jump to SubRoutine with No dela | -                              |     |

|        |         |                                 |                                |     |

|        |         | LoaD register BANK              | •                              |     |

|        |         | LoaD to Control register        | 5                              |     |

|        |         | MOVe structure data             |                                |     |

|        |         | MOVe reverse stack              |                                |     |

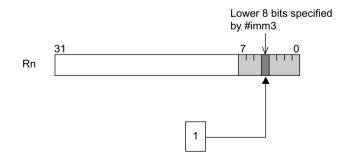

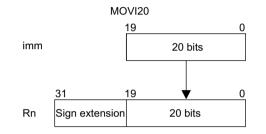

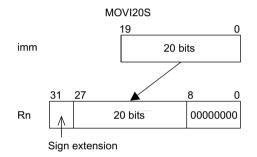

|        |         | MOVe Immediate 20bits data      |                                | 130 |

| 6.3.22 | MOVI20S | MOVe Immediate 20bits data and  |                                |     |

|        |         |                                 |                                |     |

|        |         | MOVe Multi-register Lower part  |                                |     |

| 6.3.24 |         | MOVe Multi-register Upper part  |                                |     |

|        |         | MOVe Reverse Tbit               |                                | 139 |

| 6.3.26 | MOVU    | MOVe structure data as Unsigned |                                |     |

|        |         |                                 |                                |     |

|        |         | MULtiply to Register            |                                |     |

|        |         | NOT Tbit                        |                                |     |

|        |         | PREFetch data to cache          |                                |     |