|       |        |      |             |        |          |          |           | T            |                  |           |                   |    |              |    |     |     | RE  | ۷I  | SION           | 18   |     |     |            |      |     |     |          |

|-------|--------|------|-------------|--------|----------|----------|-----------|--------------|------------------|-----------|-------------------|----|--------------|----|-----|-----|-----|-----|----------------|------|-----|-----|------------|------|-----|-----|----------|

|       |        |      |             |        |          |          |           | 1            | TR               | T         |                   |    |              | DE | 3CI | RIP | TIO | N   |                |      |     | 0   | ATE        | A    | PP  | RO  | VED      |

|       |        |      |             |        |          |          |           |              |                  | T         |                   |    |              |    |     |     |     |     |                |      |     |     |            |      |     |     |          |

|       |        |      |             |        |          |          |           |              |                  |           |                   |    |              |    |     |     |     |     |                |      |     |     |            |      |     |     |          |

|       |        |      |             |        |          |          |           | '            |                  | •         |                   |    |              |    |     |     |     |     |                |      | '   | •   |            | •    |     |     |          |

|       |        |      |             |        |          |          |           |              |                  |           |                   |    |              |    |     |     |     |     |                |      |     |     |            |      |     |     |          |

|       |        |      |             |        |          |          |           |              |                  |           |                   |    |              |    |     |     |     |     |                |      |     |     |            |      |     |     |          |

|       |        |      |             |        |          |          |           |              |                  |           |                   |    |              |    |     |     |     |     |                |      |     |     |            |      |     |     |          |

|       |        |      |             |        |          |          |           |              |                  |           |                   |    |              |    |     |     |     |     |                |      |     |     |            |      |     |     |          |

|       |        |      |             |        |          |          |           |              |                  |           |                   |    |              |    |     |     |     |     |                |      |     |     |            |      |     |     |          |

|       |        |      |             |        |          |          |           |              |                  |           |                   |    |              |    |     |     |     |     |                |      |     |     |            |      |     |     |          |

|       |        |      |             |        |          |          |           |              |                  |           |                   |    |              |    |     |     |     |     |                |      |     |     |            |      |     |     |          |

|       |        |      |             |        |          |          |           |              |                  |           |                   |    |              |    |     |     |     |     |                |      |     |     |            |      |     |     |          |

|       |        |      |             |        |          |          |           |              |                  |           |                   |    |              |    |     |     |     |     |                |      |     |     |            |      |     |     |          |

|       |        |      |             |        |          |          |           |              |                  |           |                   |    |              |    |     |     |     |     |                |      |     |     |            |      |     |     |          |

|       |        |      |             |        |          |          |           |              |                  |           |                   |    |              |    |     |     |     |     |                |      |     |     |            |      |     |     |          |

|       |        |      |             |        |          |          |           |              |                  |           |                   |    |              |    |     |     |     |     |                |      |     |     |            |      |     |     |          |

|       |        |      |             |        |          |          |           |              |                  |           |                   |    |              |    |     |     |     |     |                |      |     |     |            |      |     |     |          |

|       |        |      |             |        |          |          |           |              |                  |           |                   |    |              |    |     |     |     |     |                |      |     |     |            |      |     |     |          |

|       |        |      |             |        |          |          |           |              |                  |           |                   |    |              |    |     |     |     |     |                |      |     |     |            |      |     |     |          |

|       |        |      |             |        |          |          |           |              |                  |           |                   |    |              |    |     |     |     |     |                |      |     |     |            |      |     |     |          |

|       |        |      |             |        |          |          |           |              |                  |           |                   |    |              |    |     |     |     |     |                |      |     |     |            |      |     |     |          |

|       |        |      |             |        |          |          |           |              |                  |           |                   |    |              |    |     |     |     |     |                |      |     |     |            |      |     |     |          |

| Prep  | ared   | in   | acc         | cordar | nce      | wit      | h D       | <b>0D-</b> S | TD-1             | 00        |                   |    |              |    |     |     |     |     | Se             | elec | ted | it  | em dr      | awi  | ng  |     |          |

| REV   |        |      |             |        | T        | П        |           |              | Τ                | Т         | Τ                 | Ι  | T            | П  |     |     |     |     | П              | T    | Π   |     | П          | T    | Γ   | Γ   |          |

| PAGE  | 28     | 29   | $\sqcap$    | $\Box$ | $\vdash$ |          |           |              |                  |           |                   |    | I            |    |     |     |     |     |                | İ    | L   |     |            | I    |     |     |          |

| REV   |        | JS   | _           |        |          |          |           |              | L                |           |                   | L  | $oxed{\Box}$ |    |     |     |     |     |                |      | L   | _   |            | 1    | ↓_  | L   | $\vdash$ |

| OF PA | BES    |      | PA          | GES    | 1        | 2        | 3         | 4 5          | 6                | 7         | 8                 | 9  | 10           | 11 | 12  | _   |     | _   | 16 1           |      |     |     |            |      |     |     |          |

| 0rig  | ina!   | dat  | :e          |        |          | PR       | EPA<br>Z  | RED          | B'               | Y         | مندر              | _  |              |    | 1   |     | DEF | EN  | SE EL          | ECT  | ROM | IES | SUP        | PLY  | CE  | NTE |          |

|       | lrawin |      | 205         |        | -        | <u>ر</u> | <u> </u>  | 41           | <u>u.</u>        | 7         | 3                 |    |              |    | 4   |     | 71  | _   |                |      |     |     | 110        |      |     |     |          |

|       | 14 May | y 13 | <i>3</i> 86 |        | ı        | CH E     | $\gamma($ |              | BY<br>2<br>2 zv. | عر.       |                   |    |              |    |     | 11  | N-  | CH/ | MICRO<br>ANNEL | , SI | LIC | ON  | GATE,      | , CO | UNT | er/ | TIME     |

|       |        |      |             |        | t        | AF       | <u> </u>  | OVE          | 7                |           | $\overline{\cap}$ |    |              |    | ㅓ   |     | AN  | D F | PARALI         | .EL  | 1/0 | U۱  | IIT        |      |     |     |          |

|       |        |      |             |        |          | l'       | Π         | $\ell k$     | la               | سا        | لم                | _  |              |    |     |     |     |     |                |      |     |     |            |      |     |     |          |

|       |        |      |             |        | Γ        | 8IZ      | E         | C            | ODE              |           | DEN               | I. | NO           | ). | Ī   | DY  | NB  | N   | <b>o</b> . 8   | 5    | 51  | 7   |            |      |     |     |          |

|       |        |      |             |        | 1        |          |           |              | •                | 80        | 9                 |    |              |    |     |     |     |     | _              |      |     |     |            |      |     |     |          |

|       |        |      |             |        | -        | A        |           | <u></u>      | _1               | <u>49</u> | 33                |    |              |    | 4   |     |     |     | PAGE           |      |     |     | o <b>F</b> | 29   |     |     |          |

## 1. SCOPE

- 1.1 Scope. This drawing describes the requirements for N-channel, counter/timer and parallel I/O unit microcircuits. This drawing provides a level of microcircuit quality and reliability assurance for acquisition of microcircuits in accordance with MIL-M-38510.

- 1.2 Part number. The complete part number shall be as shown in the following example:

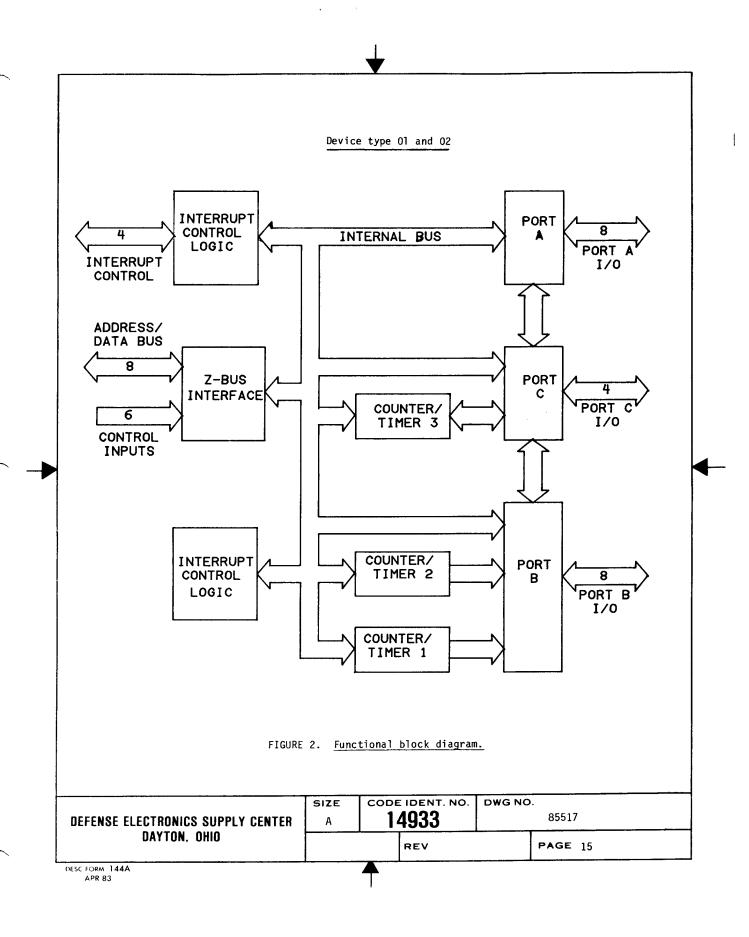

1.2.1 Device types. The device types shall identify the circuit function as follows:

| Device type | Generic number | Frequency | Circuit                                                                 |

|-------------|----------------|-----------|-------------------------------------------------------------------------|

| 01          | Z8036A         | 6.0 MHz   | Counter/timer and parallel I/O unit Counter/timer and parallel I/O unit |

| 02          | Z8036          | 4.0 MHz   |                                                                         |

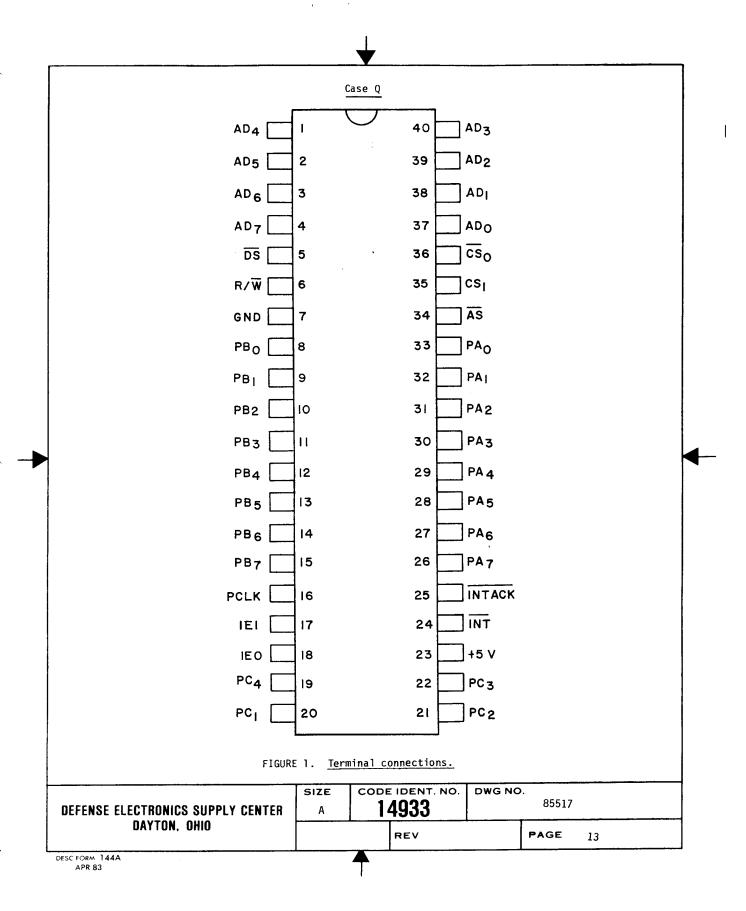

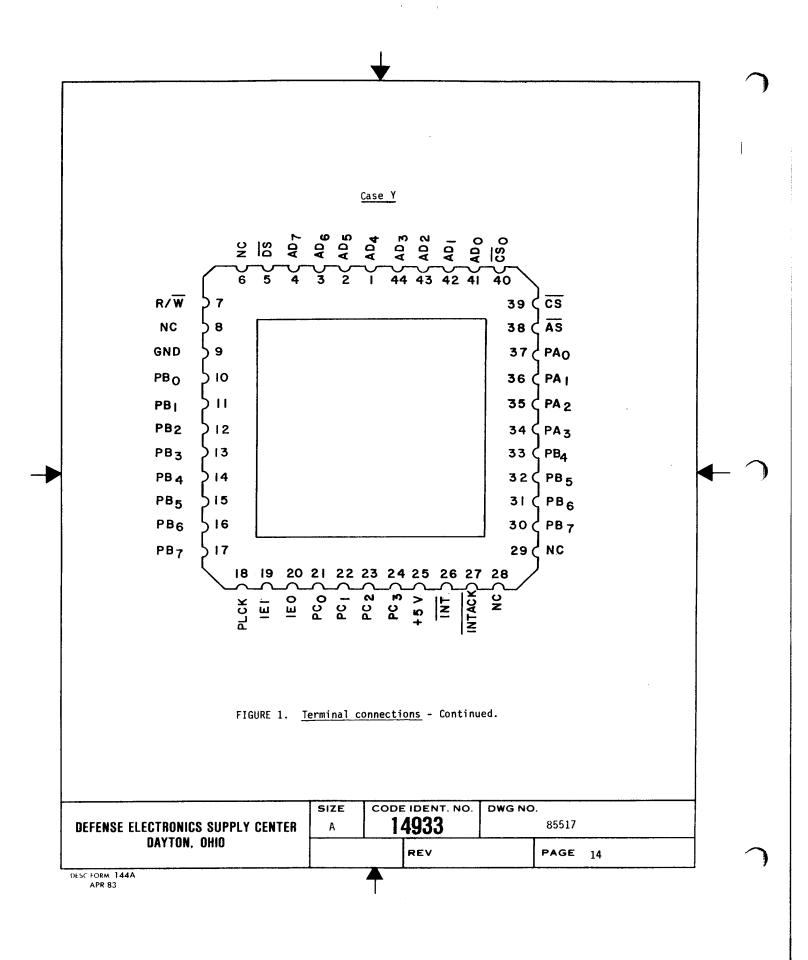

1.2.2 Case outlines. The case outlines shall be as designated in appendix C of MIL-M-38510, and as follows:

Outline letter

Q

D-5 (40-lead, 9/16" x 2"), dual-in-line package

Y

C-5 (44-terminal, .650" x .650"), square chip

carrier package

1.3 Absolute maximum ratings.

1.4 Recommended operating conditions.

| Supply voltage Minimum high level input voltage ( $V_{IL}$ ) Maximum low level input voltage ( $V_{IL}$ ) | 4.5 V dc minimum to 5.5 V dc maximum 2.2 V dc 0.8 V dc  |

|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| Frequency of operation:  Device type 01                                                                   | 0.5 MHz to 6.0 MHz                                      |

| Clock rise and fall times  Device type 01                                                                 | 10 ns maximum fall; 15 ns maximum rise<br>20 ns maximum |

| DEFENSE ELECTRONICS SUPPLY CENTER | SIZE | 14933 | DWG NO.<br>85517 |   |

|-----------------------------------|------|-------|------------------|---|

| DAYTON, OHIO                      |      | REV   | PAGE             | 2 |

## 2. APPLICABLE DOCUMENTS

2.1 Government specification and standard. Unless otherwise specified, the following specification and standard, of the issue listed in that issue of the Department of Defense Index of Specifications and Standards specified in the solicitation, form a part of this drawing to the extent specified herein.

## SPECIFICATION

MILITARY

MIL-M-38510

Microcircuits, General Specification for.

**STANDARD**

MILITARY

MIL-STD-883

Test Methods and Procedures for Microelectronics.

(Copies of the specification and standard required by manufacturers in connection with specific acquisition functions should be obtained from the contracting activity or as directed by the contracting activity.)

## 3. REQUIREMENTS

- $\frac{3.1}{\text{specified herein.}}$  The individual item requirements shall be in accordance with MIL-M-38510, and as specified herein. The country of manufacture requirement of MIL-M-38510 does not apply.

- 3.2 <u>Design, construction, and physical dimensions</u>. The design, construction, and physical dimensions shall be as specified in MIL-M-38510 and herein.

- 3.2.1 <u>Design documentation</u>. The design documentation shall be in accordance with MIL-M-38510 and, unless otherwise specified in the contract or purchase order, shall be retained by the manufacturer but be available for review by the acquiring activity or contractor upon request.

- 3.2.2 <u>Terminal connections</u>. The terminal connections shall be as specified on figure 1.

- 3.2.3 Block diagram. The block diagram shall be as specified on figure 2.

- 3.2.4 <u>Case outlines</u>. The case outlines shall be in accordance with 1.2.2.

- 3.3 Lead material and finish. The lead material and finish shall be in accordance with MIL-M-38510.

- 3.4 <u>Electrical performance characteristics</u>. Unless otherwise specified, the electrical performance characteristics are as specified in table I and apply over the full recommended case operating temperature range.

- 3.5 Marking. Marking shall be in accordance with MIL-M-38510, except the part number shall be in accordance with 1.2 herein. The Vendor Similar Part Number may also be marked in accordance with 6.10 herein. Both part numbers, when used, shall be printed on the same surface. The "M38510/XXX" part number and the "JAN" or "J" mark shall not be used. Lead finish letter "X" is used only as specified in MIL-M-38510 and shall not be marked on the microcircuit or its packaging. The country of origin shall be marked on the microcircuit.

- 3.6 Quality assurance requirements. Microcircuits furnished under this drawing shall have been subjected to, and passed all the requirements, tests, and inspections detailed herein including screening and quality conformance inspections.

| DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A | 14933 | DWG NO.<br>85517 |  |

|-----------------------------------|-----------|-------|------------------|--|

| DAYTON. OHIO                      |           | REV   | PAGE 3           |  |

|                                           | TABLE             | I. Electrical performan                            | nce characte         | ristics.    |                   |               |            |

|-------------------------------------------|-------------------|----------------------------------------------------|----------------------|-------------|-------------------|---------------|------------|

| Test                                      | Symbo             |                                                    | Group A<br>  subgrou | <del></del> | ا د               | nits<br>  Max | Unit       |

| Input high voltage                        | V <sub>IH</sub>   |                                                    | 1, 2,                | 3 ALL       | 2.2               | 1/<br>VCC+0.3 | v          |

| Input low voltage                         | VIL               |                                                    | 1, 2,                | 3 ALL       | -0.3 1/           | 0.8           | V          |

| Low output voltage                        | V <sub>OL</sub>   | I <sub>OL</sub> = 2.0 mA                           | 1, 2, 3              | ALL         | <del> </del>      | 0.4           | i v        |

| High output voltage                       | АОН               | I <sub>OH</sub> = -250 μA                          | 1, 2, 3              | ALL         | 2.4               | <br>          | <br>  V    |

| Power supply current                      | Icc               | T <sub>C</sub> = -55°C<br> V <sub>CC</sub> = 5.5 V | 1, 2, 3              | ALL         | <u> </u><br> <br> | 200           | mA         |

| Output leakage current<br>low             | ILOL              | V <sub>IN</sub> = 0.4 V                            | 1, 2, 3              | ALL         | -10               | +10           | μА         |

| Output leakage current<br>high            | ILOH              | V <sub>IN</sub> = 2.4 V                            | 1, 2, 3              | ALL         | -10               | +10           | μА         |

| Input low current                         | IIL               | V <sub>IN</sub> = 0.4 V                            | 1, 2, 3              | ALL         | -10               | +10           | μА         |

| Input high current                        | IIH               | V <sub>IN</sub> = 2.4 V                            | 1, 2, 3              | ALL         | -10               | +10           | μА         |

| aximum frequency 1/<br>low-output current | FMAX              |                                                    | 9, 10, 11            | 01<br>02    | 6.0               | <del></del>   | MHz<br>MHz |

| nput capacitance 2/                       | CIN               |                                                    | 4                    | ALL         |                   | 10            | pF         |

| utput capacitance 2/                      | COUT              |                                                    | 4                    | ALL         |                   | 15            | pF         |

| directional capacitance <u>2</u> /        | c <sub>I</sub> \0 |                                                    | 4                    | ALL         | <del></del>       | 20            | pF         |

| footnotes at end of tal                   | ole.              |                                                    |                      | -           |                   |               |            |

| FENSE ELECTRONICS SUP<br>Dayton, Ohio     | PLY CENTE         | R A 1493                                           |                      | G NO.       | 5517              |               |            |

|                                           |                   | REV                                                |                      |             |                   |               |            |

| TAR                                                                                                  | UE I Clo                     | at mi a a l            | Lacatora                                                              | anco chanact  | · · · · · · · · · · · · · · · · · · · |                | ontinue |               |           |     |                 |        |

|------------------------------------------------------------------------------------------------------|------------------------------|------------------------|-----------------------------------------------------------------------|---------------|---------------------------------------|----------------|---------|---------------|-----------|-----|-----------------|--------|

| Test                                                                                                 | SLE 1. <u>Ele</u><br> Symbol |                        | Condition                                                             | ance characte | <br> Group #                          | <del>-  </del> | Refer-  | ia.           | Limit     | ts  |                 | Unii   |

| 1030                                                                                                 |                              | -55°<br>V <sub>C</sub> | $\frac{C}{C} \stackrel{<}{\sim} \frac{T_C}{5.0} \stackrel{<}{\sim} V$ | +125°C        | subgrou                               |                | ence    | i             | )1<br>Max |     | )2<br> <br> Max | -<br>- |

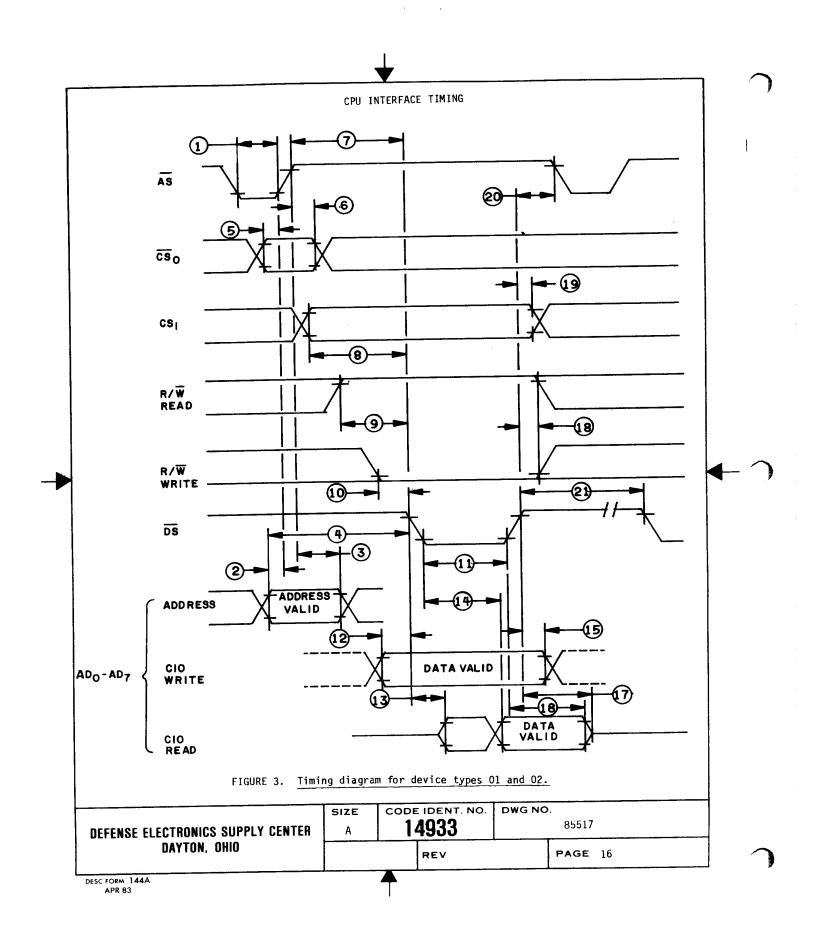

| AS low width                                                                                         | Twas                         | C <sub>L</sub> = 5     | 0 pF ±10%                                                             |               | 9, 10,                                | 11             | 1       | 1             |           |     | 2000            | ns     |

| Address to $\overline{\text{AS}} + \underline{3}/$ setup time                                        |                              | See fi                 |                                                                       |               | 19, 10,                               | 11             | 2       | 10            |           | 30  |                 | ns     |

|                                                                                                      | ThA(AS)                      | <b>-</b><br>i          |                                                                       |               | 9, 10,                                | 11             | 3       | <br>  30 <br> |           | 50  |                 | ns     |

| Address to $\overline{DS}$ + $\underline{2}$ /, $\underline{3}$ / setup time                         | TsA(DS)                      |                        |                                                                       |               | 9, 10,                                | 11             | 4       | 100           |           | 130 |                 | ns     |

| $\overline{\text{CS}}_0$ to $\overline{\text{AS}}$ † $\underline{2}$ /, $\underline{3}$ / setup time | TsCSO(AS)                    |                        |                                                                       |               | 9, 10,                                | 11             | 5       | 0             |           | 0   |                 | ns     |

| $\overline{CS}_0$ to $\overline{AS}$ hold time $\underline{3}$                                       | <br> ThCSO(AS) <br>          |                        |                                                                       |               | 9, 10,                                | 11             | 6       | 40            |           | 60  |                 | ns     |

| $\overline{AS}$ † to $\overline{DS}$ ‡ delay $2/3/$                                                  | TdAS(DS)                     | -                      |                                                                       |               | 9, 10,                                | 11             | 7       | 55            |           | 85  |                 | ns     |

| CS $_1$ to $\overline{	extsf{DS}}$ $\downarrow$ setup time                                           | TsCS1(DS)                    | <b>-</b>               |                                                                       |               | 9, 10,                                | 11             | 8       | 80            |           | 100 |                 | ns     |

| R/W (Read) to DS + set up time                                                                       | TsRWR(DS)                    |                        |                                                                       |               | 9, 10,                                | 11             | 9       | <br>  80 <br> |           | 100 |                 | ns     |

| R/W (Write) to DS + 2/<br>setup time                                                                 | <br> TsRWW(DS) <br>          |                        |                                                                       |               | 9, 10,                                | 11             | 10      | 0             |           | 0   |                 | ns     |

| $\overline{DS}$ low width $\underline{2}$ /                                                          | TwDS                         |                        |                                                                       |               | 9, 10,                                | 11             | 11      | 250           |           | 390 |                 | ns     |

| Write data to $\overline{DS} \downarrow \underline{2}/$ setup time                                   | TsDW(DSf)                    |                        |                                                                       |               | 9, 10,                                | 11             | 12      | 20            |           | 30  |                 | ns     |

| DS (Read) ↓ to address<br>data bus driven                                                            | TdDS(DRV)                    |                        |                                                                       |               | 9, 10,                                | 11             | 13      | 0             |           | 0   |                 | ns     |

| DS ↓ to read data valid delay                                                                        | TdDSf(DR)                    |                        |                                                                       |               | 9, 10,                                | 11             | 14      |               | 180       |     | 250             | ns     |

| Write data to $\overline{DS} + \underline{2}/$                                                       | ThDW(DS)                     |                        |                                                                       |               | 9, 10,                                | 11             | 15      | 20            |           | 30  |                 | ns     |

| DS † to read data <u>2/</u><br>not valid delay                                                       | TdDSr(DR)                    |                        |                                                                       |               | 9, 10,                                | 11             | 16      | 0             |           | 0   |                 | ns     |

| ee footnotes at end of t                                                                             | table.                       |                        |                                                                       |               |                                       |                |         |               |           |     |                 |        |

| DEFENSE ELECTRONICS S                                                                                | -                            | NTER                   | SIZE                                                                  | 1493          | _                                     | DW             | VG NO.  | 85517         | ,         |     |                 |        |

| DAYTON, O                                                                                            | าเป                          |                        |                                                                       | REV           |                                       |                |         | PAGE          | : 5       |     |                 |        |

| Tank                                                                            | [Cumb o ]                    |                           | anditions             |          |            | Pofon         | Ţ            | Limits             | 5                   |                              | Uni               |

|---------------------------------------------------------------------------------|------------------------------|---------------------------|-----------------------|----------|------------|---------------|--------------|--------------------|---------------------|------------------------------|-------------------|

| Test                                                                            | Symbol                       | -55°C                     | onditions<br>≤ Tc ≤ + | 125°C    | subgroups  | Refer-        |              | 01                 | 02                  |                              | [<br>[            |

| !                                                                               | <br>                         | unless                    | = 5.0 V<br>otherwise  | specifie | d          |               | Min          | Max                | Min                 | Max                          | <u> </u>          |

| $\frac{2}{DS}$ + to read data float delay                                       | <u> </u>                     | unless                    | pF ±10%<br>otherwise  | specifie | 9, 10, 11  | 17            | <br> <br>    | 45                 |                     | 70                           | ns                |

| R/W to DS † 2/<br>hold time                                                     | ThRW(DS)                     | See fig<br> <br> -        | ure 3                 |          | 9, 10, 11  | 18            | 40           | <br> <br>          | 55                  |                              | ns                |

| CS <sub>1</sub> to $\overline{DS}$ † $\underline{2}/$                           | ThCS <sub>1</sub> (DS)       |                           |                       |          | 9, 10, 11  | 19            | 40           | !<br> <br>         | 55                  | <br>                         | ns                |

| DS + to AS + delay <u>2</u> /                                                   | TdDS(AS)                     |                           |                       |          | 9, 10, 11  | 20            | 25           | <br> <br>          | 50                  |                              | ns                |

| Valid access <u>2/5/</u><br>recovery time                                       | TrC                          | <br> <br>                 |                       |          | 9, 10, 11  | 21            | 650          |                    | 1000                | <u> </u>                     | ns                |

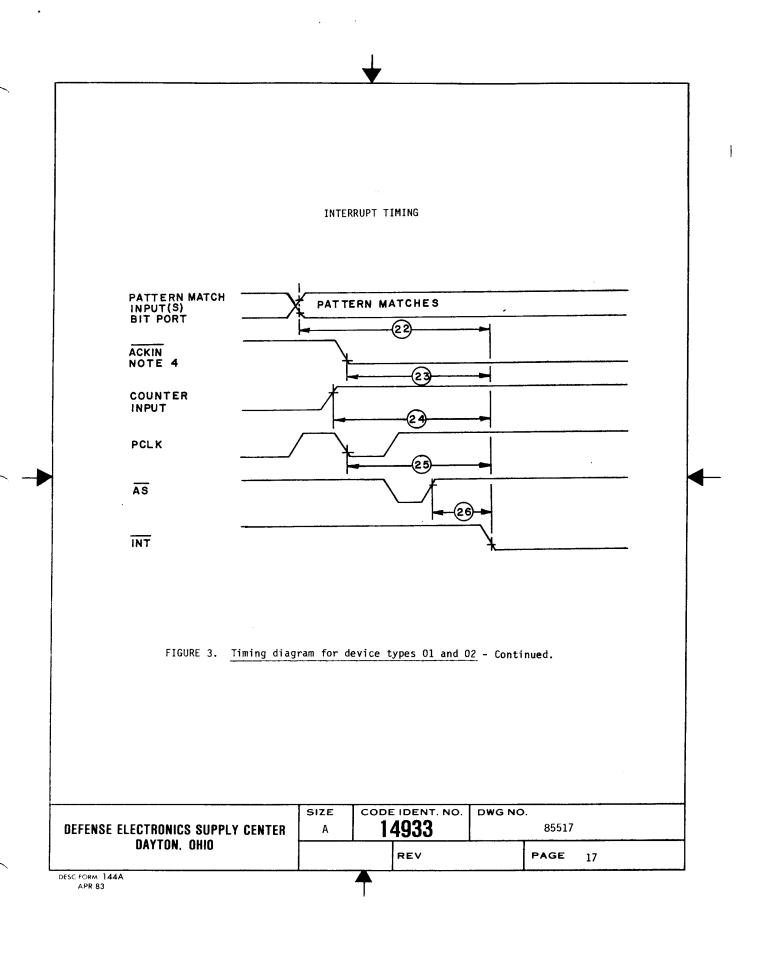

| 2/ 6/<br>Pattern match to INT<br>delay (bit port)                               | TdPM(INT)                    | <br> <br>                 |                       |          | 9, 10, 11  | 22            |              | 1+800<br>          |                     | 1+800                        | ns                |

| ACKIN to INT delay<br>(Port with<br>handshake) <u>2</u> / <u>6</u> / <u>7</u> / | <br> TdACK(INT) <br> <br>    | 1<br> <br> <br> -         |                       |          | 9, 10, 11  | 23            | <br> -<br> - | 4+600<br>          |                     | <br>  <b>4</b> +600<br> <br> | ns                |

| Counter input to INT<br>delay 2/ 6/<br>(counter mode)                           | <br> TdC1(INT)<br>           | <br> <br> <br>            |                       |          | 9, 10, 11  | 24            |              | <br> 1+700<br>     | <br> <br>           | <br> 1+700<br>               | !<br>  ns<br>     |

| PCLK to TNT delay<br>(timer mode) <u>2</u> / <u>6</u> /                         | TdPC(INT)<br>                | !<br> <br>                |                       |          | 9, 10, 11  | 25            |              | 1+700<br>          |                     | 1+700<br>                    | ns                |

| AS to INT delay 2/                                                              | <br> TdAS(INT)<br>           | <br> <br> -               |                       |          | 9, 10, 11  | 26            |              | <br>               |                     | 300                          | ns                |

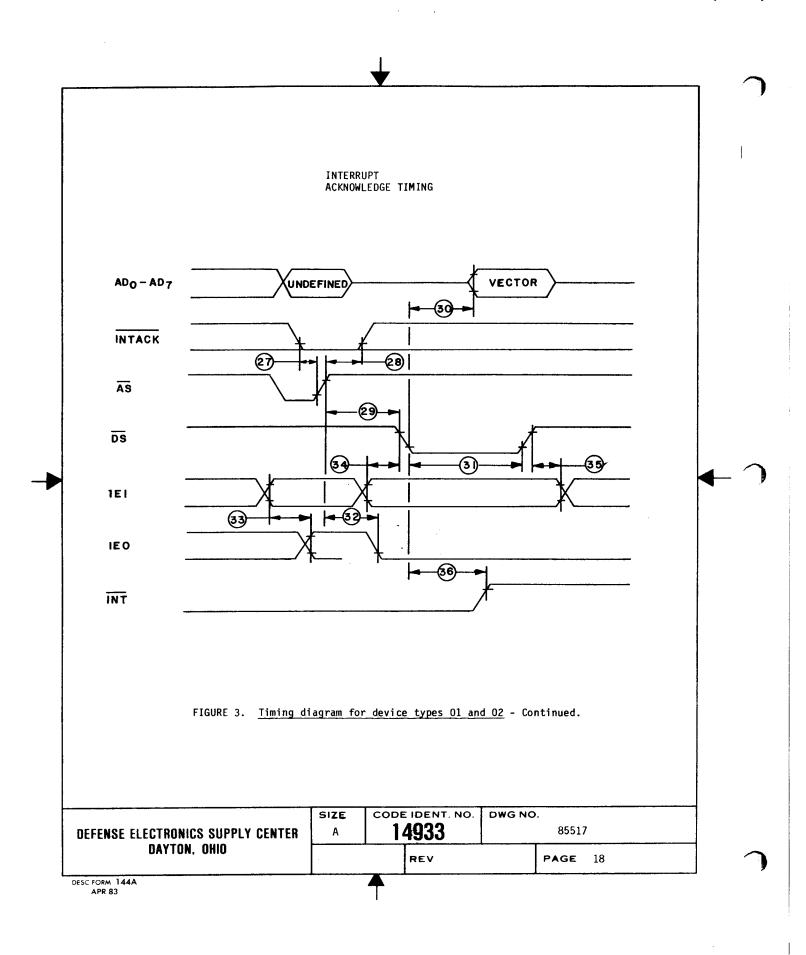

| INTACK to AS + setup time                                                       | <br> Ts1A(AS)<br>            | <br> <br> <br>            |                       |          | 9, 10, 11  | <br>   27<br> | 0 2/         | •                  | 0                   | <br> <br> <br>               | l<br>lns<br>l     |

| INTACK to AS † hold time                                                        | <br> Th1A(AS)<br>            | Γ<br> <br> -              |                       |          | 9, 10, 1   | 28            | 250          | <br>               | 250                 | <br> <br>                    | l<br>l ns         |

| AS + to DS<br>(acknowledge) +<br>setup time <u>2</u> / <u>8</u> /               | <br> TsAS(DSA)<br> <br> <br> | i<br> <br> <br> <br> <br> |                       |          | 9, 10, 11  | 29            | 250          | <br> -<br> -<br> - | <br>  350<br> <br>  | <br> <br> <br> <br>          | <br>  ns<br> <br> |

| DS (acknowledge) + to<br>read data valid<br>delay <u>2</u> /                    | <br> TdDSA(DR)<br> <br> <br> | T<br> <br> -<br> <br>     |                       |          | 19, 10, 11 | 30            |              | <br>  180<br> <br> | <br> <br> <br> <br> | <br>  250<br> <br> <br>      | ns                |

| ee footnotes at end o                                                           | f table.                     |                           |                       |          |            |               |              |                    |                     |                              |                   |

| DEFENSE ELECTRONIC                                                              |                              | ENTER                     | SIZE<br>A             | 149      | 133        | DWG NO        |              | 517                |                     |                              |                   |

| DAYTON,                                                                         | UHIU                         |                           |                       | R        | EV         |               | PAG          | SE                 | 6                   |                              |                   |

|                                                                              | T                             | τ                         |                                |                      |             |       |              | <u></u>         | <del></del>     | Limits     | <u> </u> |                 | Γ                 |

|------------------------------------------------------------------------------|-------------------------------|---------------------------|--------------------------------|----------------------|-------------|-------|--------------|-----------------|-----------------|------------|----------|-----------------|-------------------|

| Test                                                                         | Symbol                        | 55                        | Condition C < T <sub>C</sub> < | ns<br>+125°C         |             | oup   |              | Refer-<br>lence | ļ,              | 01         | - 0      |                 | i<br>Uni          |

|                                                                              |                               | 1                         | Vrr = 5.0                      | V ±10%<br>se specifi | I           | byr o | ups          | l               |                 | Γ          | Min      | T               | <u>†</u>          |

| DS (acknowledge) 2/<br>low width                                             | I<br>  Twdsa<br>              | <u>l</u> uñ1es            |                                | ኔ<br>se specifi      |             | 10,   | 11           | 31              | <br> 250<br>    | ]<br>      | 390      | <br> <br>       | ns                |

| 2/ 8/<br>AS ↑ to IEO → delay<br>INTACK cycle                                 | <br> TdAS(IEO)<br>            | See f                     | igure 3                        |                      | <br> 9,     | 10,   | 11           | 32              |                 | 250<br>    |          | l<br>l 350<br>l | l<br>  ns<br>     |

| IEI to IEO delay $\underline{2}$ , $\underline{8}$ /                         | <br> TdIEI(IEO)<br>           | T<br> <br> <br>           |                                |                      | 9,          | 10,   | 11           | 33              | ]<br> <br> <br> | 100        |          | <br>  150<br>   | <br>  ns<br> <br> |

| IEO to DS<br>(acknowledge)<br>↓ setup time 2/8/                              | <br> TsIEI(DSA)<br> <br> <br> | T<br> <br> <br> <br> <br> |                                |                      | 19,         | 10,   | 11           | 34              | 70              |            | 100      |                 | l ns              |

| IEI to DS<br>(acknowledge)<br>+hold time 2/                                  | <br> ThIEI(DSA)<br> <br>      | <br>                      |                                |                      | 9,          | 10,   | 11           | 35              | 70              |            | 100      |                 | l ns              |

| DS (acknowledge)<br>to INT + delay 2/                                        | <br> TdDSA(INT)<br>           | Ť<br> <br>                |                                |                      | <br> 9,<br> | 10,   | 11           | 36              | 1               | 600        |          | 600             | l ns              |

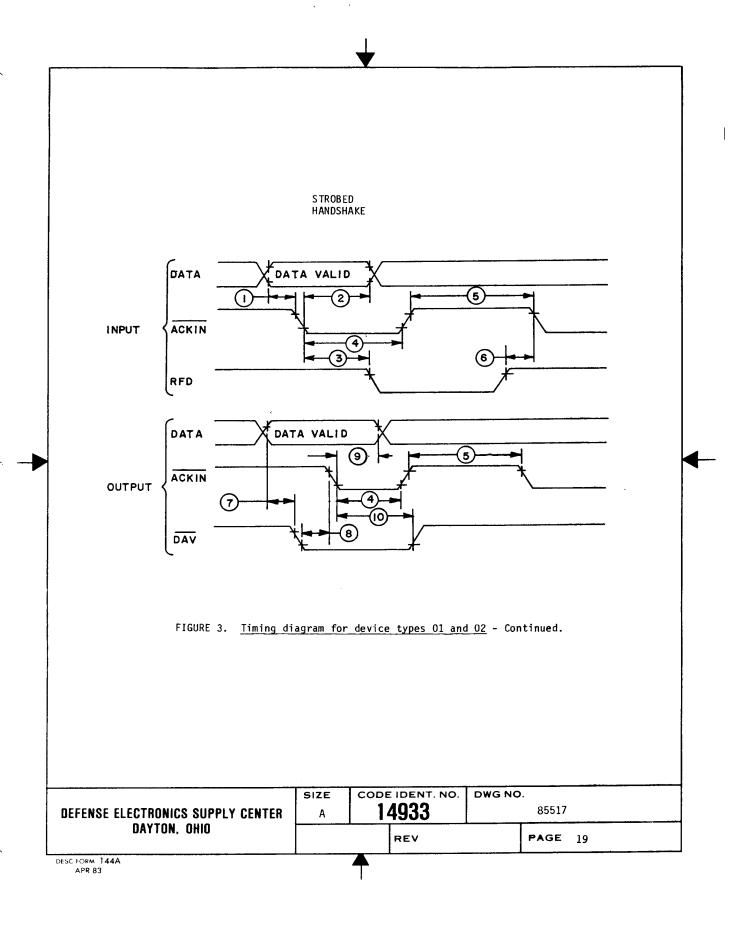

| 2/<br>Data input to ACKIN↓<br>setup time                                     | TsDI(ACK)                     | T<br>!<br>!               |                                |                      | 19,         | 10,   | 11           | 1               | 0               |            | 0        |                 | l ns              |

| 2/<br>Data input to ACKIN +<br>hold time - strobed<br>handshake              |                               | <br> <br>                 |                                |                      | <br> 9,<br> | 10,   | 11           | 2               | <br>            |            | 500      | ,               | l<br>l ns<br>l    |

| ACKIN + to RFD + delay                                                       | <br> TdACKf(RFD)<br>          | [<br>]<br>[               |                                |                      | <br> 9,<br> | 10,   | 11           | 3               | 0               | 1          | 0        |                 | l<br>I ns         |

| 2/<br>ACKIN low width -<br>strobed handshake                                 | <br> Twacki<br>               | <br>                      |                                |                      | <br> 9,<br> | 10,   | 11           | 4               |                 |            | 250      |                 | l<br>ns           |

| ACKIN high width -<br>strobed handshake                                      | TWACKI                        |                           |                                |                      | <br> 9,<br> | 10,   | 11           | 5               | <br> <br>       |            | 250      |                 | l ns              |

| RFD ↑ to ACKIN ↓ 2/<br>delay                                                 | TdRFDr(ACK)                   | F<br> <br>                |                                |                      | 9,          | 10,   | 11           | 6               | <br>  0 <br>    |            | 0        |                 | ns                |

| 2/, 9/<br>Data out to DAV ↓<br>setup time                                    | TsDO(DAV)                     | <br> <br>                 |                                |                      | 9,          | 10,   | 11 <br> <br> | 7               | 20              | ļ          | 25       |                 | ns                |

| DAV + to ACKIN + 2/ 1 delay                                                  | TdDAVf(ACK)                   | <br> <br>                 |                                |                      | <br> 9,<br> | 10,   | 11  <br>     | 8               | 0               | <br> <br>  | 0        |                 | ns                |

| $\frac{2}{10}$ , $\frac{10}{10}$<br>Data out to ACKIN $\downarrow$ hold time | ThDO(ACK)                     |                           |                                |                      | 9,          | 10,   | 11           | 9               | 1 1             | <br>  <br> | 1        |                 | ns                |

| ee footnotes at end of                                                       | table.                        |                           |                                |                      |             |       |              |                 |                 |            |          |                 |                   |

| DEFENSE ELECTRONICS                                                          |                               | TER                       | SIZE<br>A                      | 149                  |             | NO.   | D            | WG NO.          | 8551            | .7         |          |                 |                   |

| DAYTON,                                                                      | טווט                          |                           |                                | RE                   | v           |       |              |                 | PAG             | E 7        |          |                 |                   |

| Test                                                                    | Symbol                    | 1                      | Condition                                                    |        |                     |                |                |     | Refer- |                     | Limit        |                     |              | <br> Unit    |             |

|-------------------------------------------------------------------------|---------------------------|------------------------|--------------------------------------------------------------|--------|---------------------|----------------|----------------|-----|--------|---------------------|--------------|---------------------|--------------|--------------|-------------|

|                                                                         |                           | 1                      | °C < T <sub>C</sub> <<br>V <sub>CC</sub> = 5.0<br>s otherwis | V ±10% | ;                   | 1              | grou           |     | lence  | Min                 | )1<br>Max    | 0:<br> <br> Min     |              | <br>         |             |

| delay                                                                   | Tdack(dav)<br>            | lunles                 | 50 pF ±10%<br>s otherwis                                     |        |                     | 9,             | 10,            | 11  | 10     | 1                   | <br>         | 1                   | <br>         | ns           |             |

| 2/<br>Data input to RFD ↓<br>hold time - inter-<br>locked handshake     | <br> ThDI(RFD)<br>        | See f1<br> <br> <br> - | igure 3                                                      |        | ļ                   | 9,             | 10,            | 11  | 11     | 0                   |              | 0                   |              | ns           |             |

| RFD + to ACKIN +  delay - inter- locked handshake                       | <br> TdRFDf(ACK)<br>      | <br> <br> <br> <br> -  |                                                              |        |                     | 9,             | 10,            | 11  | 12     | 0                   |              | 0                   |              | ns           |             |

| RFD + delay-<br>interlocked and<br>3-wire handshake                     | <br> TdACKr(RFD)<br> <br> | <br> <br> <br> <br> -  |                                                              |        |                     | 9,             | 10,            | 11  | 13     | 0                   |              | 0                   | <br> <br>    | ns           |             |

| (RFD ↑ ) inter-<br>locked and 3-wire<br>handshake                       | TdDAVr(ACK)               |                        |                                                              |        | 1                   | 9,             | 10,            | 11  | 14     | 0                   |              | 0                   |              | ns           |             |

| ACKIN + (RFD + ) to DAV + delay - interlocked and 3-wire handshake      | TdACK(DAV)                | <br> <br>              |                                                              |        |                     | 9,             | 10,            | 11  | 15     | 0                   |              | 0<br>               |              | ns<br>!      |             |

| DAV + to DAC + delay<br>input 3-wire 2/<br>handshake                    | TdDAVIf(DAC)              | <br> <br> <br> -       |                                                              |        | ;<br>;<br>;         | 9,             | 10,            | 11  | 16     | <br>  0 <br>        |              | <br>  0 <br>        |              | ns           |             |

| hold time - 3-wire handshake                                            | ThDI(DAC)                 |                        |                                                              |        | <br> <br> <br>      | 9,             | 10,            | 11  | 17     | 0                   |              | <br>  0 <br>        |              | ns           |             |

| DAC ↑to DAV ↑ delay<br>input 3-wire<br>handshake                        | TdDACOr(DAV)              | <br> <br>              |                                                              |        |                     | <br> <br> <br> | 9,             | 10, | 11     | 18                  | 0            | ·                   | 0            |              | l ns        |

| DAV + to DAC + delay input 3-wire handshake                             | TdDAVIr(DAC)              | ! !<br>! !<br>T !      |                                                              |        |                     |                | 9,             | 10, | 11     | 19                  | <br>  0 <br> |                     | <br>  0 <br> | <br>         | ns<br> <br> |

| DAV + to DAC ↑ delay output 3-wire handshake                            | TdDAVOf(DAC)              |                        |                                                              |        |                     |                | <br> <br> <br> | 9,  | 10,    | 11                  | 20           | <br>  0 <br>        | ·            | <br>  0 <br> |             |

| Data output to DAC $\uparrow$ hold time - 3-wire handshake $2/$ , $10/$ |                           |                        |                                                              |        | <br> <br> <br> <br> | 9, 1           | 10,            | 11  | 21     | <br>  1 <br>   <br> |              | <br>  1 <br>   <br> |              | ns<br>       |             |

| ee footnotes at end of                                                  | f table.                  |                        |                                                              |        |                     |                |                |     |        |                     |              |                     |              |              |             |

| DEFENSE ELECTRONIC                                                      |                           | ITER                   | SIZE<br>A                                                    |        | 493                 | _              | 10.            | D   | WG NO. | 8551                | 7            |                     |              |              |             |

| DAYTON,                                                                 | טווט                      |                        |                                                              | REV    |                     |                |                |     | PAGE 8 |                     |              |                     | l            |              |             |

| 1                                                           |                       |                                      |                             |             |      |            |             |                |                |                     |                      |           |

|-------------------------------------------------------------|-----------------------|--------------------------------------|-----------------------------|-------------|------|------------|-------------|----------------|----------------|---------------------|----------------------|-----------|

|                                                             | TABLE I. Ele          | ctrical perfo                        | mance charact               | eri         | stic | <u>s</u> - | Contin      | ued.           |                |                     |                      |           |

| Test                                                        | Symbol                | Condit                               | ions                        | Gr          | oup  | Α          | Refer-      | 1              | Limit          | 5                   |                      | Uni       |

| 1030                                                        | !<br>!                | -55°C < Tc                           | < +125°C                    | sul         | bgro | ups        | ence        |                | 01             | 0                   |                      | Ţ         |

| 37                                                          | <br>                  | V <sub>CC</sub> = 5<br>lunless other | .℧ V ±10%<br>wise specified | <br>        |      |            | ]<br>]<br>  | Min            | <br> Max       | <br> Min            | Max                  | <br> <br> |

| DAC + to DAV + delay<br>output 3-wire<br>handshake          | 1                     |                                      | 10%<br>wise specified       |             | 10,  | 11         | 22<br> <br> | 1              | <br> <br> <br> | 1                   | <br>                 | ns        |

|                                                             | <br> TdDAVOr(DAC)<br> | !<br>                                |                             | 9,          | 10,  | 11         | 23          | 0              | <br> <br> <br> | 0                   | <br> <br>            | ns        |

| PCLK cycle time $11/$                                       | TcPC                  |                                      |                             | 9,          | 10,  | 11         | 1           | 165            | 4000           | 250                 | 4000                 | ns        |

| PCLK high width <u>2</u> /                                  | <br> TwPCh            |                                      |                             | 9,          | 10,  | 11         | 2           | 70             | 2000           | 105                 | <br>  2000<br>       | l ns      |

| PCLK low width                                              | TwPCI                 | Γ<br> <br>                           |                             | 9,          | 10,  | 11         | 3           | 70             | 2000           | 105                 | 2000                 | ns        |

| PCLK fall time                                              | TfPC                  | <b>"</b><br>                         |                             | 19,         | 10,  | 11         | 4           | <br> <br> <br> | 10             |                     | 1 20<br>1 <u>2</u> / | l ns      |

| PCLK rise time <u>2</u> /                                   | TrPC                  |                                      |                             | 9,          | 10,  | 11         | 5           | <del> </del>   | 15             |                     | 20                   | l ns      |

| Counter input cycle   time 2/                               | TcCI                  |                                      |                             | 9,          | 10,  | 11         | 6           | 330            |                | 500                 | <br>                 | l ns      |

| Counter input high  <br>width <u>2</u> /                    | TCIh                  |                                      |                             | 19,         | 10,  | 11         | 7           | 150            | <br>   <br>    | 230                 | <br> <br>            | l ns      |

| Counter input low   width 2/                                | TwCII                 |                                      |                             | 9,          | 10,  | 11         | 8           | 150            |                | 230                 |                      | ns        |

| Counter input fall   time 2/                                | TfCI                  | -                                    |                             | <br> 9,<br> | 10,  | 11         | 9           |                | 15             | <br>  <br>          | 20                   | ns        |

| Counter input rise time <u>2</u> /                          | TrCI                  | -                                    |                             | <br> 9,<br> | 10,  | 11         | 10          | <del> </del>   | 15             | <br> <br> <br>      | 20                   | ns        |

| 2/, 12/ Trigger input to   PCLK * setup time   (timer mode) | TsTI(PC)              | -                                    |                             | <br> 9,<br> | 10,  | 11         | 11          |                |                | 150  <br> <br> <br> |                      | ns        |

| Test                                                                           | Symbol            | T<br>I                     | Conditio                                                    | ns                               | <br> Gro              | oup A  | <br> Refer-            | T                    | Limit               |                 |                 | Unit        |

|--------------------------------------------------------------------------------|-------------------|----------------------------|-------------------------------------------------------------|----------------------------------|-----------------------|--------|------------------------|----------------------|---------------------|-----------------|-----------------|-------------|

|                                                                                |                   | -55<br> <br> unles         | °C < T <sub>C</sub> <<br>V <sub>CC</sub> = 5.0<br>s otherwi | +125°C<br>V ±10%<br>se specified | l sub                 | groups |                        | T                    | 01<br> <br> Max     | O:<br> <br> Min | 2               | Γ<br>Γ<br>Ι |

| 2/, 12/<br>Irigger input to<br>counter input ↓<br>setup time<br>(counter mode) | TsTI(CI)          | C <sub>L</sub> =<br> unles | 50 pF ±10                                                   |                                  | 9,                    | 10, 11 | 12                     | <br> <br> <br> <br>  |                     | 150             | <br> <br> -<br> | ns          |

| 2/<br>Trigger input pulse<br>width (high or low)                               |                   | <del> </del><br>           |                                                             |                                  | <br> 9,<br>           | 10, 11 | 13                     | †<br> <br> <br> <br> | <br>  <br>          | 200             | <br> <br> <br>  | ns          |

| Gate input to PCLK + setup time (timer mode) 2/, 12/                           | <br> TsGI(PC)<br> | <del> </del>               |                                                             |                                  | <br> 9,<br> <br>      | 10, 11 | <br>  14<br>           | <br> <br> <br>       | <br> <br> <br> <br> | 100             |                 | ns          |

| 2/, 12/<br>Gate input to counter<br>input ↓ setup time<br>(counter mode)       | TsGI(C1)          | Ť<br> <br> <br>            |                                                             |                                  | 9,                    | 10, 11 | 15<br> <br>            |                      |                     | 100             |                 | ns          |

| 2/, 12/ Gate input to PCLK + hold time (timer mode)                            | <br> ThGI(PC)<br> | <br>                       |                                                             |                                  | <br> 9,<br>           | 10, 11 | <br>  16<br>           |                      | <br> <br> <br>      | 100             |                 | ns          |

| 2/, 12/ Gate input to counter input + hold time (counter mode)                 | ThGI(C1)          | T<br>                      |                                                             |                                  | [<br> 9,<br> <br>     | 10, 11 | <br>  17<br>           | <br> <br> <br> <br>  | <br> <br> <br>      | 100             |                 | ns          |

| 2/<br>PCLK to counter<br>output delay<br>(timer mode)                          | TdPC(CO)          | <br> -<br> -               |                                                             |                                  | <br> 9,<br> <br>      | 10, 11 | <br>  18<br>           |                      | <br> <br> <br>      |                 | 475             | ns          |

| 2/<br>Counter input to<br>counter output<br>delay (counter<br>mode)            | TdCI(CO)          | <br> <br> <br>             |                                                             |                                  | <br> 9,<br> <br> <br> | 10, 11 | <br>  19<br> <br> <br> | <br> <br> <br> <br>  | <br> <br> <br> <br> |                 | 475             | ns          |

| $\frac{\overline{OS}}{4}$ to REQ + delay $\frac{2}{2}$                         | TdDS(REQ)         | T<br> <br> <br>            |                                                             |                                  | <br> 9,<br> <br>      | 10, 11 | !<br>  1<br>           | <br> <br> <br> <br>  | <br>                | <br> <br> <br>  | 500             | ns          |

| OS + to WAIT + delay                                                           | TdDS(WAIT)        | T<br> <br> <br>            |                                                             |                                  | <br> 9,<br>           | 10, 11 | 2                      | <br> <br> <br>       | <br>                |                 | 500             | ns          |

| PCLK + to REQ + delay                                                          | TdPC(REQ)         | T<br> <br> <br>            |                                                             |                                  | <br> 9,<br>           | 10, 11 | 3<br> <br>             | <br> <br>            |                     |                 | 300             | ns          |

| ee footnotes at end of                                                         | f table.          |                            |                                                             |                                  | _                     |        |                        |                      |                     |                 |                 |             |

|                                                                                |                   |                            | SIZE                                                        | CODE IDE                         | -                     | NO. E  | WG NO.                 |                      |                     |                 |                 |             |

| DEFENSE ELECTRONIC DAYTON.                                                     |                   | NTER                       | A                                                           | 1493                             | <u>ა</u>              |        |                        | 8551                 | 17                  |                 |                 | i           |

| T 4                                                                     | Secret 3                 |                                                                     |            |                  |             |                | In - 6          | Ţ                  | Limit          | s              |                    | lle.       |

|-------------------------------------------------------------------------|--------------------------|---------------------------------------------------------------------|------------|------------------|-------------|----------------|-----------------|--------------------|----------------|----------------|--------------------|------------|

| Test                                                                    | Symbol                   | Condition                                                           |            |                  | oup<br>ogro |                | Refer-<br> ence | \ <del></del>      | 01             | 0:             |                    | Uni<br>    |

|                                                                         | <u> </u>                 | V <sub>CC</sub> = 5.0<br> unless otherwi                            | √ V ±10%   | 1                |             |                | j<br>           | Min                | Max            | Min            | Max                | Γ<br> <br> |

| PCLK + to WAIT ↑<br>delay <u>2</u> /                                    | Ţ                        | <br> C <sub>L</sub> = 50 pF ±10<br> unless otherwi<br> See figure 3 |            |                  | 10,         | 11             | 4<br>  4<br>    | 1                  | <br> <br> <br> | <br> <br> <br> | 300<br>            | ns         |

| ACKIN + to REQ + delay 2/, 13/, 14/                                     | !<br> TdACK(REQ)<br>     | <br>                                                                |            | <br> 9,<br>      | 10,         | 11             | 5               | <br> <br>          | <br> <br> <br> |                | 3+2<br> +1000      |            |

| $\frac{ACKIN + to WAIT +}{delay}$                                       | <br> Tdack(wait)<br>     | ]<br> <br>                                                          |            | <br> 9,<br> <br> | 10,         | 11             | <br>  6<br>     |                    | <br> <br>      | <br> <br>      | <br>  10+<br>  600 | ns         |

| 2/<br>Delay from DS ↑ to<br>AS ↓ for no reset                           | <br> TdDSQ(AS)<br>       | T<br> <br>                                                          |            | <br> 9,<br>      | 10,         | 11             | 1               | 15                 | <br> <br>      | <br>  40<br>   | <br> <br> <br>     | ns         |

| <u>Z/</u><br>Delay from AS ↑ to<br>DS ↓ for no reset                    | i<br> TdASQ(DS)<br> <br> | Т<br> <br> <br>                                                     | -          | 9,               | 10,         | 11             | 2               | 30                 |                | 50             |                    | ns         |

| Minimu <u>m</u> width of AS<br>and DS both low for<br>reset <u>16</u> / | <br> Twres<br> <br>      | <br>                                                                | -          | 9,<br> <br>      | 10,         | 11             | 3               | 170                |                | 250            |                    | ns         |

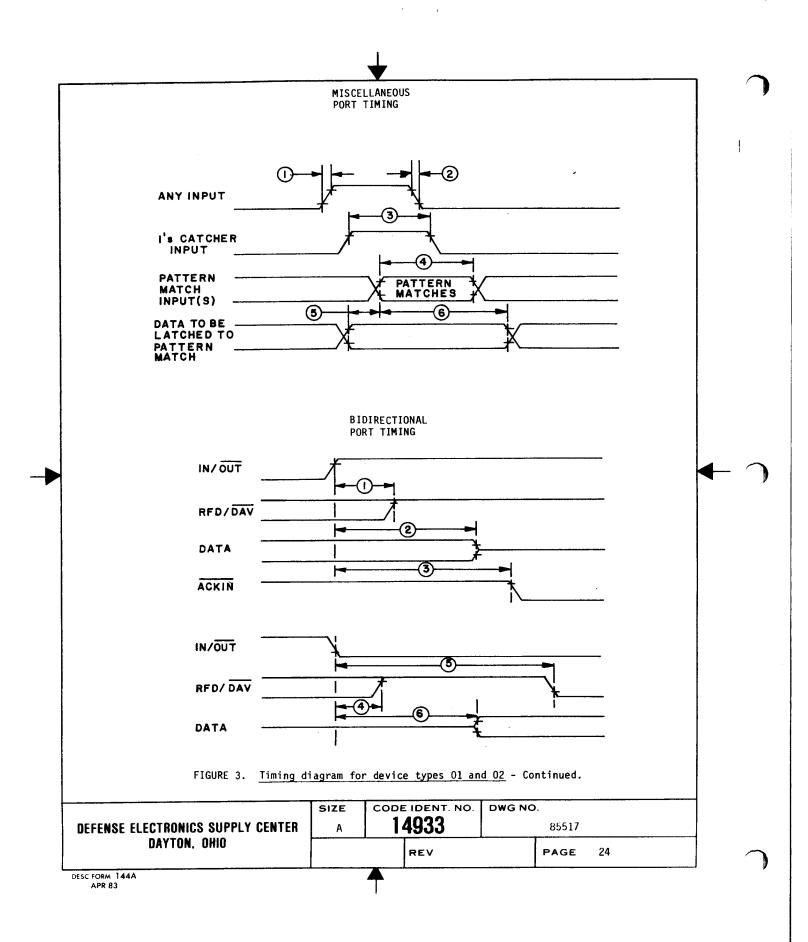

| Any input rise time                                                     | <br> TrI<br>             | Г<br>!<br>!                                                         | -          | <br> 9,<br>      | 10,         | 11             | 1               | <br> <br> <br>     | 100            |                | 100                | ns         |

| Any input fall time $\frac{2}{4}$                                       | <br> TfI<br>             |                                                                     |            | 9,               | 10,         | 11             | 2               |                    | 100            |                | 100                | ns         |

| 1's catcher high<br>width <u>2</u> /, <u>17</u> /                       | Twl's                    | T<br> <br>                                                          |            | 9,               | 10,         | 11             | 3               | 170                |                | 250            |                    | ns         |

| Pattern match input<br>valid (bit port) 2/                              | TwPM                     |                                                                     |            | 9,               | 10,         | 11             | 4               | <br> 500 <br>      |                | 750            |                    | ns         |

| Data latched on pattern match setup time (bit port) 2/                  |                          |                                                                     |            | 9,               | 10,         | 11             | 5               | 0                  |                | 0              | <br>               | ns         |

| Data latched on pattern match hold   time (bit port) 2/                 | ThPMD I                  | <b>T</b>                                                            | )<br> <br> | 9,               | 10,         | 11             | 6               | <br> 650 <br> <br> | <br> <br> <br> | 1000           |                    | ns         |

| ee footnotes on next p                                                  | age.                     | <del> </del>                                                        | <u> </u>   |                  |             | _ , _ <u>'</u> |                 | ·                  | <u> </u>       | •              | · · · · · · ·      |            |

| DEFENSE ELECTRONICS                                                     |                          | TER A                                                               | 1493       |                  | VО.         | D              | wg no.          | 8551               | .7             |                |                    |            |

| DAYTON,                                                                 | UNIU                     |                                                                     | REV        |                  |             |                |                 | PAG                | E 11           |                |                    |            |

| Test                                                                                                        | Symbol                   | Conditions                                                                       | Gro                                                                                    | oup /  | ——<br>А       | <br> Refer-      | T              | Limit          | _               |                    | <br> Uni     |

|-------------------------------------------------------------------------------------------------------------|--------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--------|---------------|------------------|----------------|----------------|-----------------|--------------------|--------------|

|                                                                                                             |                          | -55°C < Tc < +125°C   subgroups lence   0                                        | -55°C < T <sub>C</sub> < +125°C   subgroups lence   01<br>V <sub>CC</sub> = 5.0 V ±10% |        | subgroupsence |                  | 01             | 02             |                 | Ţ                  |              |

|                                                                                                             |                          | unless otherwise specified                                                       | <u> </u>                                                                               | Min Ma | Max           | Min              | Max            |                |                 |                    |              |

| I/O + to RFD/DAV high<br>delay <u>2</u> /                                                                   | TdIOr(DAV)<br> <br>      | <br> C <sub>L</sub> = 50 pF ±10%<br> unless otherwise specified<br> See figure 3 |                                                                                        | 10,    | 11            | 1                | <br> <br> <br> | 500<br> <br>   | ]<br> <br> <br> | <br>  500<br> <br> | ns           |

| $I/\overline{0}$ † to data float delay $\underline{2}/$                                                     | <br> TdIOr(DRZ)<br> <br> | <u> </u><br>                                                                     | 9,                                                                                     | 10,    | 11            | 2                | <br> <br> <br> | 500<br>        |                 | 500                | l ns         |

| I/O + to ACKIN + delay 18/                                                                                  | <br> TdIOr(ACK)<br> <br> |                                                                                  | <br> 9,<br>                                                                            | 10,    | 11            | <br>  3<br> <br> | <br> <br> <br> | <br> <br> <br> |                 | !<br> <br> <br>    | l ns         |

| I/O + to RFD/DAV<br>high delay <u>2</u> /                                                                   | TdIOf(RFD)               |                                                                                  | 9,                                                                                     | 10,    | 11            | 4                | 1              | 500<br>        | !<br>           | <br>  500<br>      | <br>  ns<br> |

| $I/\overline{0} + \text{tc RFD}/\overline{\text{DAV}} + \text{delay} \qquad \underline{2}, \underline{19}/$ | TdIOf(DAV)<br>           | T<br>                                                                            | 9,                                                                                     | 10,    | 11            | <br>  5<br>      | 3              | <br> <br> <br> | 3               | <br> <br> <br>     | l ns<br>l    |

| I/ <del>0</del> + to data bus<br>driven 2/, 19/                                                             | <br> TdDO(10)<br>        | T<br> <br>                                                                       | 9,                                                                                     | 10,    | 11            | 6                | <br>  2<br>    |                | 2               |                    | l ns         |

Guaranteed by characterization/design.

Guaranteed, if not tested.

Parameter does not apply to interrupt acknowledge transactions.

Float delay is measured to the time when the output has changed 0.5 V from steady state with minimum AC load and maximum DC load.

This is the delay from  $\overline{DS}$  + of one CIO access to  $\overline{DS}$  + of another CIO access.

Units equal to AS cycle + ns.

The delay is from DAV + for 3-wire input handshake. The delay is from DAC + for 3-wire output handshake. One additional AS cycle is required for ports in the single buffered mode.

The parameters for the devices in any particular daisy chain must meet the following constraint: the delay from  $\overline{AS}$   $\uparrow$  to  $\overline{DS}$   $\uparrow$  must be greater than the sum of TdAS(IEO) for the highest priority peripheral. TsIEI(DSA) for the lowest priority peripheral, and TdIEI(IEO) for each peripheral separating them in the chain.

This time can be extended through the use of the deskew timers.

Units equal to AS cycle.

PCLK is only used with the counter/timers (in timer mode), the deskew timers, and the REQUEST/WAIT logic. If these functions are not used, the PCLK input can be held low. These parameters must be met to guarantee the trigger or gate is valid for the next  $\Pi$ /

counter/timer cycle

The delay is from DAV + for the 3-wire input handshake. The delay is from DAC ↑ for the 3-wire 13/ output handshake.

Units equal to AS cycles + PCLK cycles + ns.

Units equal to PCLK cycles + ns.

Internal circuitry allows for the reset provided by the Z8 (DS held low while AS pulses) to be sufficient.

If the input is programmed inverting, a low-going pulse of the same width will be detected.

18/ Minimum delay is four AS cycles or one AS cycle after the corresponding IP is cleared, whichever is longer.

Units equal to AS cycles.

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO | SIZE<br>A | 14933 | DWG NO.<br>85517 |  |  |

|------------------------------------------------|-----------|-------|------------------|--|--|

|                                                |           | REV   | PAGE 12          |  |  |

| DESC FORM 144A                                 |           |       |                  |  |  |

APR 83

Powered by ICminer.com Electronic-Library Service CopyRight 2003

- 3.6.1 Screening. Screening shall be in accordance with method 5004, class B of MIL-STD-883 and 4.2 herein.

- 3.6.2 Qualification. Qualification inspection for the device types specified herein shall not be required.

- 3.6.3 Quality conformance inspection. Quality conformance inspection shall be in accordance with MIL-M-38510 and 4.4 herein.

- 3.6.4 Burn-in test circuit documentation. The burn-in test circuit documentation shall be made available to the acquiring activity on request.

- 3.7 Manufacturer eligibility. To be eligible to supply microcircuits to this drawing, a manufacturer shall have manufacturer certification in accordance with MIL-M-38510 for at least one line and have part I listing on Qualified Products List QPL-38510 for at least one device type (not necessarily the one for which the acquisition of this drawing is to apply).

- 3.8 Certificate of compliance. A certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply (see 6.9 and 6.10).

- 4. QUALITY ASSURANCE PROVISIONS

- 4.1 Sampling and inspection. Sampling and inspection procedures shall be in accordance with MIL-M-38510 and method 5005 of MIL-STD-883, except as modified herein.

- 4.2 <u>Screening</u>. Screening shall be in accordance with method 5004 of MIL-STD-883, and shall be conducted on all devices prior to quality conformance inspection. The following additional criteria shall apply:

- a. Burn-in test (method 1015 of MIL-STD-883).

- (1) Test condition A, B, C, or D.

- (2)  $T_A = +125$ °C, minimum.

- b. Interim and final electrical test parameters shall be as specified in table II herein, except interim electrical parameter tests prior to burn-in are optional at the discretion of the manufacturer.

- c. The percent defective allowable (PDA) shall be as specified in MIL-M-38510.

- 4.3 Qualification inspection. Qualification inspection for the device types specified herein shall not be required.

- 4.4 Quality conformance inspection. Quality conformance inspection shall be in accordance with MIL-M-38510 and method 5005 of MIL-STD-883. Groups A and B inspections shall be performed on each inspection lot or as specified in method 5005 of MIL-STD-883. Groups C and D shall be performed on a periodic basis in accordance with MIL-M-38510. Generic test data (see 6.5) may be used to satisfy the requirements for groups C and D inspections. Manufacturers shall keep lot records for 5 years (minimum), monitor for compliance to the prescribed procedures, and observe that satisfactory manufacturing conditions and records on lots are maintained for these devices. The records, including an attributes summary of all screening and quality conformance inspections conducted on each lot shall be available for review by customers at all times.

| DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A | 14933 | DWG NO.<br>85517 |    |

|-----------------------------------|-----------|-------|------------------|----|

| DAYTON, OHIO                      |           | REV   | PAGE             | 25 |

DESC FORM 144A

APR 83

| MIL-STD-883 test requirements                                      | Subgroups<br>  (per method<br>  5005, table I) |

|--------------------------------------------------------------------|------------------------------------------------|

| Interim electrical parameters (method 5004)                        |                                                |

| Final electrical test parameters<br>(method 5004)                  | 1, 2, 3, 9                                     |

| Group A test requirements (method 5005)                            | 1, 2, 3, 7, 8,<br>9, 10, 11**                  |

| Groups C and D end-point<br>electrical parameters<br>(method 5005) | 1, 2, 3                                        |

|                                                                    |                                                |

- \* PDA applies to subgroup 1 (see 4.2c).

- \*\* Subgroups 10 and 11, if not tested, shall be guaranteed to the specified limits in table I.

- 4.4.1 Group A inspection. Group A inspection shall consist of the test subgroups and LTPD values shown in table I of method 5005 of MIL-STD-883, class B, and as follows: