# UNISONIC TECHNOLOGIES CO., LTD

# PA3332

Preliminary

CMOS IC

# 2.6W STEREO AUDIO AMPLIFIER

# DESCRIPTION

The UTC **PA3332** is a stereo audio power amplifier. When the device is idle, it enters SHDN mode for some low current consumption applications. The current dissipation is thus reduced below 5µA. Mute function is included to mute the output.

Operating on a 5V power supply, the UTC **PA3332** is capable of driving a 4.0  $\Omega$  BTL load at a continuous average RMS output of 2.0W per channel with a less than 1% THD. %

There are two input paths, therefore, two different gain loops can be set in the same PCB. We could choose one of the two gain paths through the logic level of  $\overline{IN}/IN$  pin. This increases the flexibility of the hardware design. In order to prevent the speakers from burned-out, the UTC **PA3332** also has a function of maximum output power clamping is designed.

#### FEATURES

#### \* Including de-pop circuit

- \* Output power at 1% THD+N, VDD=5V 2.0W/CH (TYP.) into a 4Ω Load 1.3W/CH (TYP.) into a 8Ω Load

- \* Output power at 10% THD+N, VDD=5V 2.6W/CH (typical) into a 4Ω Load 1.6W/CH (typical) into a 8Ω Load

- DTL mode (Dridge Tied Load)

- \* BTL mode (Bridge-Tied Load)

- \* Maximum output power clamping circuitry contained

- \* Mute and shutdown control available

- \* Stereo input MUX

- \* Halogen Free

#### ORDERING INFORMATION

| Ordering      | Number                                                              | Package   | Dooking   |

|---------------|---------------------------------------------------------------------|-----------|-----------|

| Lead Free     | Lead Free Halogen Free                                              |           | Packing   |

| PA3332L-N24-T | PA3332G-N24-T                                                       | HTSSOP-24 | Tube      |

| PA3332L-N24-R | PA3332L-N24-R PA3332G-N24-R                                         |           | Tape Reel |

| PA3332L-N24-T | PA3332L-N24-T<br>(1)Packing Type<br>(2)Package Type<br>(3)Lead Free |           | Free      |

# PA3332

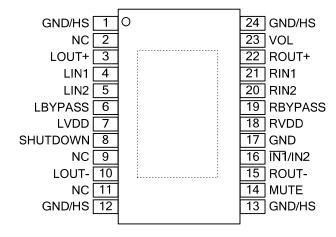

# PIN CONFIGURATION

Note: Recommend connecting the Thermal Pad to the GND for excellent power dissipation.

#### ■ PIN DESCRIPTION

| PIN NO.          | PIN NAME | DESCRIPTION                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1, 12,<br>13, 24 | GND/HS   | Ground connection for circuitry, directly connected to thermal pad.                                                                                                                                                                                                                                                                          |  |  |  |

| 2, 9, 11         | NC       | Embedded test mode pin, please keep it floating.                                                                                                                                                                                                                                                                                             |  |  |  |

| 3                | LOUT+    | Left channel + output in BTL mode                                                                                                                                                                                                                                                                                                            |  |  |  |

| 4                | LIN1     | Left channel IN1 input, selected when IN1 /IN2 pin is held low.                                                                                                                                                                                                                                                                              |  |  |  |

| 5                | LIN2     | Left channel IN2 input, selected when IN1 /IN2 pin is held high.                                                                                                                                                                                                                                                                             |  |  |  |

| 6                | LBPASS   | Connect to voltage divider for left channel internal mid-supply bias.                                                                                                                                                                                                                                                                        |  |  |  |

| 7                | LVDD     | Supply voltage input for left channel and for primary bias circuits.                                                                                                                                                                                                                                                                         |  |  |  |

| 8                | SHUTDOWN | Shutdown mode control signal input, places entire IC in shutdown mode when held high, $I_{DD}$ < 5µA.                                                                                                                                                                                                                                        |  |  |  |

| 10               | LOUT-    | Left channel - output in BTL mode.                                                                                                                                                                                                                                                                                                           |  |  |  |

| 14               | MUTE     | Mode control signal input, hold low for activation, hold high for mute.                                                                                                                                                                                                                                                                      |  |  |  |

| 15               | ROUT-    | Right channel - output in BTL mode                                                                                                                                                                                                                                                                                                           |  |  |  |

| 16               | IN1/IN2  | MUX control input, hold high to select in2 inputs (5,20), hold low to select in1 inputs (4,21).                                                                                                                                                                                                                                              |  |  |  |

| 17               | GND      | Ground connection for circuitry.                                                                                                                                                                                                                                                                                                             |  |  |  |

| 18               | RVDD     | Supply voltage input for right channel.                                                                                                                                                                                                                                                                                                      |  |  |  |

| 19               | RBYPASS  | Connect to voltage divider for right channel internal mid-supply bias.                                                                                                                                                                                                                                                                       |  |  |  |

| 20               | RIN2     | Right channel in2 input, selected when IN1 /IN2 pin is held high.                                                                                                                                                                                                                                                                            |  |  |  |

| 21               | RIN1     | Right channel in1 input, selected when IN1 /IN2 pin is held low.                                                                                                                                                                                                                                                                             |  |  |  |

| 22               | ROUT+    | Right channel + output in BTL mode                                                                                                                                                                                                                                                                                                           |  |  |  |

| 23               | VOL      | The output power can be clamped by setting a low bound voltage to this pin. The high bound voltage will be generated internally. The output voltage will be clamped between high/low bound voltages. Then the output power is lim-ited. It is weakly pull-low internally, let this pin floating or tied to GND can deactivate this function. |  |  |  |

| Thermal<br>Pad   |          | Recommend connecting the Thermal Pad to the GND for excellent power dissipation.                                                                                                                                                                                                                                                             |  |  |  |

# PA3332

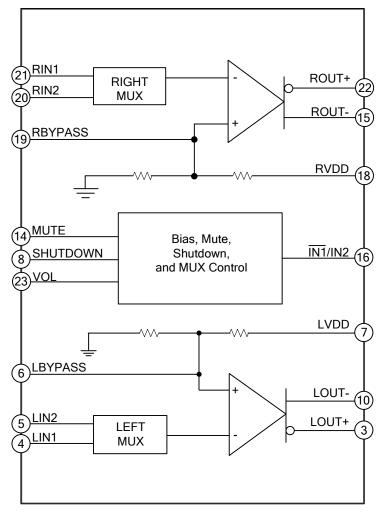

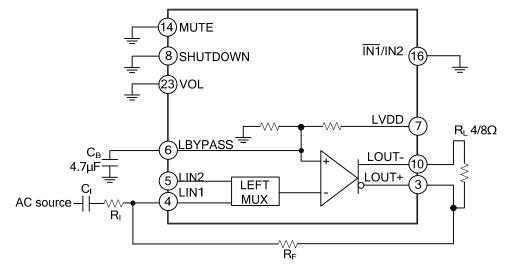

### BLOCK DIAGRAM

### ABSOLUTE MAXIMUM RATING

| PARAMETER                                  |                       | SYMBOL           | RATINGS                   | UNIT |  |

|--------------------------------------------|-----------------------|------------------|---------------------------|------|--|

| Supply Voltage                             |                       | V <sub>DD</sub>  | 6                         | V    |  |

| Input Voltage                              |                       | V <sub>IN</sub>  | -0.3~V <sub>DD</sub> +0.3 | V    |  |

| Operating Ambient Temperature              |                       | T <sub>A</sub>   | -40 ~ +85                 | °C   |  |

| Junction Temperature                       |                       | ТJ               | 150                       | °C   |  |

| Storage Temperature                        |                       | T <sub>STG</sub> | -65 ~ +150                | °C   |  |

| Reflow Temperature (soldering, 10sec)      |                       |                  | 260                       | °C   |  |

|                                            | T <sub>A</sub> ≤ 25°C |                  | 2.7                       | W    |  |

| Power Dissipation (Note 2)                 | T <sub>A</sub> ≤ 70°C | PD               | 1.7                       |      |  |

|                                            | T <sub>A</sub> ≤ 85°C |                  | 1.4                       |      |  |

| Electrostatic Discharge<br>Human Body Mode |                       | V <sub>ESD</sub> | -3000 ~ 3000 (Note 3)     | V    |  |

Notes: 1. Absolute maximum ratings are those values beyond which the device could be permanently damaged. Absolute maximum ratings are stress ratings only and functional device operation is not implied.

2. Recommended PCB Layout

3. Human body model : C = 100pF, R =  $1500\Omega$ , 3 positive pulses plus 3 negative pulses

### ELECTRICAL CHARACTERISTICS

| PARAMETER                                         | TEST CO                 | MIN                                                                           | TYP                 | MAX    | UNIT |    |        |  |

|---------------------------------------------------|-------------------------|-------------------------------------------------------------------------------|---------------------|--------|------|----|--------|--|

| DC Electrical Characteristics (T <sub>A</sub> =+2 | 25°C)                   |                                                                               |                     |        |      |    |        |  |

| Supply Current in Mute Mode                       | l==                     | V <sub>DD</sub> =3.3V                                                         | Stereo BTL          |        | 7    | 13 | m^     |  |

|                                                   | I <sub>DD(MTE)</sub>    | $V_{DD} = 5V$                                                                 | Stereo BTL          |        | 8    | 16 | mA     |  |

| DC Differential Output Voltage                    | V <sub>O(DIFF)</sub>    | V <sub>DD</sub> = 5V,Gain = 2                                                 | 2                   |        | 5    | 50 | mV     |  |

| I <sub>DD</sub> in Shutdown                       | I <sub>SD</sub>         | $V_{DD} = 5V$                                                                 |                     |        | 2    | 5  | μA     |  |

| AC Operation Characteristics (V <sub>DD</sub> =   | 5.0V, T <sub>A</sub>    | =+25°C, R <sub>L</sub> = 4Ω, ι                                                | Inless otherwise    | noted) |      |    |        |  |

|                                                   |                         | THD = 1%, BTL, I                                                              |                     | 2.0    |      |    |        |  |

| Output Power (Note 1)                             | Pout                    | THD = 1%, BTL, I                                                              |                     | 1.3    |      | W  |        |  |

|                                                   |                         | THD = 10%, BTL,                                                               |                     | 2.6    |      |    |        |  |

|                                                   |                         | THD = 10%, BTL,                                                               |                     | 1.6    |      |    |        |  |

|                                                   |                         | P <sub>0</sub> = 1.6W, BTL,                                                   | R <sub>L</sub> = 4Ω |        | 100  |    |        |  |

| Total Harmonic Distortion Plus Noise              | THD+N                   | $P_0 = 1W, BTL, R_L$                                                          | = 8Ω                |        | 60   |    | m%     |  |

|                                                   |                         | V <sub>I</sub> = 1V, R <sub>L</sub> = 10K                                     | Ω, G = 1            |        | 10   |    |        |  |

| Max Output Power Bandwidth                        | B <sub>OM</sub>         | G = 1, THD = 1%                                                               |                     |        | 20   |    | kHz    |  |

| Phase Margin                                      |                         | $R_L = 4\Omega$ , Open Lo                                                     | ad                  |        | 60   |    | 0      |  |

| Power Supply Ripple Rejection                     | PSRR                    | f = 120Hz                                                                     |                     |        | 65   |    | dB     |  |

| Mute Attenuation                                  |                         |                                                                               |                     |        | 90   |    | dB     |  |

| Channel-To-Channel Output                         |                         | f = 1kHz                                                                      |                     |        | 80   |    | dB     |  |

| Separation                                        |                         |                                                                               |                     |        | 80   |    | uБ     |  |

| IN1/IN2 Input Separation                          |                         |                                                                               |                     |        | 80   |    | dB     |  |

| Input Impedance                                   | ZI                      |                                                                               |                     |        | 2    |    | MΩ     |  |

| Signal-To-Noise Ratio                             |                         | P <sub>O</sub> = 500mW, BT                                                    | _                   |        | 90   |    | dB     |  |

| Output Noise Voltage                              | Vn                      | Output noise volta                                                            | age                 |        | 55   |    | μV(rms |  |

| AC Operation Characteristics (V <sub>DD</sub> =   | =3.3V, T <sub>A</sub> = | +25°C, R <sub>L</sub> = 4Ω, u                                                 | nless otherwise r   | noted) |      |    |        |  |

|                                                   | Роит                    | THD = 1%, BTL, I                                                              | R <sub>L</sub> = 4Ω |        | 0.85 |    |        |  |

| Output Bower (Note 1)                             |                         | THD = 1%, BTL, I                                                              |                     | 0.55   |      | W  |        |  |

| Output Power (Note 1)                             |                         | THD = 10%, BTL, $R_L = 4\Omega$                                               |                     |        | 1.1  |    | vv     |  |

|                                                   |                         | THD = 10%, BTL,                                                               |                     | 0.7    |      |    |        |  |

|                                                   | THD+N                   | $P_{O} = 0.7W, BTL, R_{L} = 4\Omega$<br>$P_{O} = 0.45W, BTL, R_{L} = 8\Omega$ |                     |        | 270  |    | m%     |  |

| Total Harmonic Distortion Plus Noise              |                         |                                                                               |                     |        | 100  |    |        |  |

|                                                   |                         | $V_1 = 1V, R_L = 10K\Omega, G = 1$ 10                                         |                     |        |      |    |        |  |

| Max Output Power Bandwidth                        | Вом                     | G = 1, THD = 1%                                                               |                     |        | 20   |    | kHz    |  |

| Phase Margin                                      |                         | $R_L = 4\Omega$ , Open Lo                                                     | ad                  |        | 60   |    | 0      |  |

| Power Supply Ripple Rejection                     | PSRR                    | f = 120Hz                                                                     |                     |        | 65   |    | dB     |  |

| Mute Attenuation                                  |                         |                                                                               |                     |        | 90   |    | dB     |  |

| Channel-To-Channel Output                         |                         |                                                                               |                     |        | 00   |    | 40     |  |

| Separation                                        |                         | f = 1kHz                                                                      |                     |        | 80   |    | dB     |  |

| IN1/IN2 Input Separation                          |                         |                                                                               |                     |        | 80   |    | dB     |  |

| Input Impedance                                   | Zı                      |                                                                               |                     |        | 2    |    | MΩ     |  |

| Signal-To-Noise Ratio                             |                         | P <sub>0</sub> = 500mW, BT                                                    |                     |        | 90   |    | dB     |  |

| Output Noise Voltage                              | Vn                      | Output noise volta                                                            | age                 |        | 55   |    | µV(rms |  |

Note 1: Output power is measured at the output terminals of the IC at 1kHz.

#### APPLICATION INFORMATION

#### Input MUX Operation

For the UTC **PA3332**, there exist two input signal paths (IN<u>1</u> and IN2). Thus, for different input sources, the UTC **PA3332** has different gains with this prompt setting. When the IN1 / IN2 pin is in active high, this device operates in IN2 input source; when it is in active low, this device operates in IN1 input source.

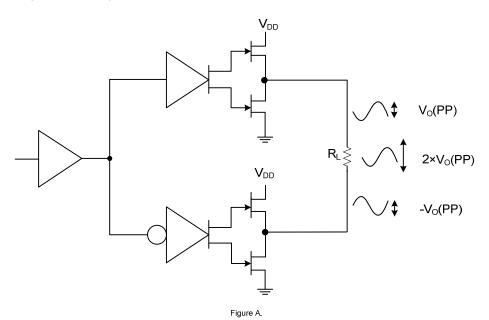

#### Bridged-Tied Load Mode Operation

The following figure A shows the BTL (Bridged-Tied Load) mode operation. The two linear amplifiers drive both ends of the speaker load.

There are several advantages for using the BTL mode: first of all, the differential driving to the speaker load means that when one side is slewing up, the other side is slewing down, and vice versa. The voltage swing on the load is two times that on a ground reference load. In this mode, the peak-to-peak voltage  $V_0(PP)$  on the load will be double a ground reference configuration. 4 times output power on the load will be generated at the same power supply rail and loading due to the voltage on the load is doubled. Further more, this BTL operation can cancel the dc offsets which save the using of dc coupling capacitor that is needed to cancel dc offsets in the ground reference configuration. Then the input network and speaker responses can only limit the low-frequency performance. Moreover, the saving of dc coupling capacitors can minimize PCB space and the cost.

Circuits with mute and shutdown functions are contained in the UTC **PA3332**, which is designed to reduce I<sub>DD</sub> (supply current) to the absolute minimum level during nonuse periods for battery-power conservation.

When pulling the shutdown pin (pin 8) high, all linear amplifiers will be deactivated to mute the amplifier outputs. Then the device enters an extremely low current consumption condition, the supply current is less than  $5\mu$ A. When the mute pin (pin 14) is pulled high, it will force the activated linear amplifier to supply the VDD/2 dc voltage on the output & shutdown the second linear amplifiers to mute the AC performance. The current dissipation will be smaller in the mute mode operation than that in the BTL mode.

It is not allowed to leave the shutdown and mute pins floating, or unexpected conditions would occur for the amplifier operations.

#### Maximum Power Clampping Function

The UTC **PA3332** incorporated the maximum power clamping function that effectively reduces damage the speaker due to the larger power through the speaker. The Vol pin (pin 23) is weakly pull-low internally. If a non-zero voltage applies in the Vol pin, the UTC **PA3332** will generate a high boundary voltage which the difference between the VDD/2 and the high boundary voltage is the same as the difference between the VDD/2 and the low boundary voltage. (i.e.  $V_{OH} - VDD/2 = VDD/2 - V_{OL}$ ). Then the outputs of linear amplifiers will be effectively limited between the high/low boundary voltage, the maximum output power is clamped. Thus, the maximum power is controlled perfectively by means of setting the value of Vol,

Note that if this function is not used, the Vol pin should be connected to the GND or be floated.

#### **Optimizing DEPOP Operation**

The UTC **PA3332** contains a circuit that can reduce poping to minimum during the power-up or shutdown mode. The poping can be generated as long as a voltage step is applied to the speaker and the differential voltage generated at the two ends of the speaker.

To get a minimum poping, the bypass capacitor is critical,  $1/(C_Bx100k\Omega) \leq 1/(C_I^*(R_I+R_F))$ . (Where  $C_B$  is the mid-rail bypass capacitor,  $100k\Omega$  is the output impedance of the mid-rail generator,  $R_I$  is the input impedance,  $C_I$  is the input coupling capacitor,  $R_F$  is the gain setting impedance which is on the feedback path.  $C_B$  is the most important capacitor. It can be applied in reducing the poping together with determining the rate at which the amplifier starts up during startup or recovery from shutdown mode.)

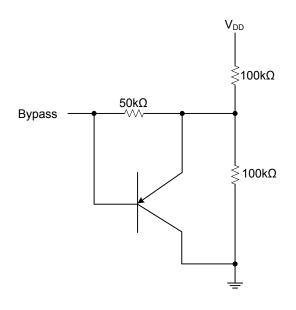

The Figure B shows the de-poping circuit for the UTC **PA3332**. The PNP transistor effectively controls the voltage drop across the  $50k\Omega$  by slewing the internal node slowly when power is applied.

At start-up, the voltage at BYPASS capacitor is zero. The PNP is ON to pull the mid-point of the bias circuit down. So the capacitor sees a lower effective voltage, and thus the charging is slower. This appears as a linear ramp (while the PNP transistor is conducting), followed by the expected exponential ramp of an RC circuit.

Figure B.

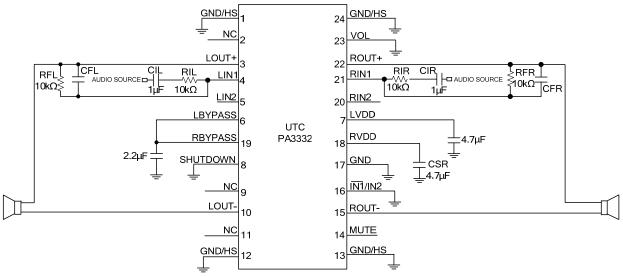

# TEST CIRCUIT

**BTL Mode Test circuit**

#### TYPICAL APPLICATION CIRCUIT

Logical Truth Table

|      | OUTPUT   |          |         |          |          |                 |

|------|----------|----------|---------|----------|----------|-----------------|

| Mute | 1IN /IN2 | Shutdown | Input   | L/R Out+ | L/R Out- | Mode            |

| Х    | Х        | High     | Х       | -        | -        | Shutdown (Mute) |

| Low  | Low      | Low      | L/R IN1 | Output   | Output   | BTL             |

| Low  | High     | Low      | L/R IN2 | Output   | Output   | BTL             |

| High | Low      | Low      | L/R IN1 | Output   | -        | Mute            |

| High | High     | Low      | L/R IN2 | Output   | -        | Mute            |

UTC assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all UTC products described or contained herein. UTC products are not designed for use in life support appliances, devices or systems where malfunction of these products can be reasonably expected to result in personal injury. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice.