## Am2817A

2048 x 8-Bit Electrically Erasable PROM

#### DISTINCTIVE CHARACTERISTICS

- 5-Volt-only operation

- Write-protect circuitry to preserve data on power up and power down

- Ready/Busy pin for end-of-write indication

- Self-timed write cycle with on-chip latches

- Minimum endurance of 10,000 write cycles per byte with a 10-year retention. For detailed information, see the Am9864 Reliability Report (PID #06891A)

#### GENERAL DESCRIPTION

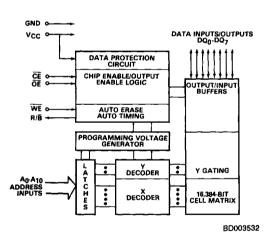

The Am2817A is a 16,384-bit Electrically Erasable Programmable Read-Only Memory (EEPROM). It is organized as 2048 words by 8 bits per word and offers a fast 200 ns read access time.

The 2817A has a fully self-timed write cycle with address, data, and control lines latched during the write operation.

The latched inputs and self-timed write cycle free the microprocessor to perform other processes during write. A transparent automatic erase before write enhances system performance.

To eliminate bus contention in a microprocessor system, this device offers separate Output Enable (OE) and Chip Enable (CE) controls.

The Am2817A is fabricated on AMD's highly manufacturable N-Channel silicon gate process and uses AMD's proprietary EEPROM technology to achieve electrically alterable, non-volatile storage.

#### **BLOCK DIAGRAM**

## MODE SELECT TABLE

| CE | ŌĒ    | WE     | Outputs    | R/B       | Mode          |

|----|-------|--------|------------|-----------|---------------|

| L  | L     | Н      | DOUT       | Hi-Z      | Read          |

| L  | Н     | Н      | Hi-Z       | Hi-Z      | Read Inhibit  |

| H  | Х     | Х      | Hi-Z       | Hi-Z      | Standby       |

| L  | н     | T      | DIN        | ъ         | Byte Write    |

|    | Autom | atic b | efore each | ''Write'' | Byte Erase    |

| X  | L     | Х      | -          | -         | Write Inhibit |

H = HIGH

L = LOW

X = Don't Care

∐ = Pulse

#### PRODUCT SELECTOR GUIDE

| Part<br>Number      | Am2817A-2 | Am2817A-20 | Am2817A | Am2817A-25 | Am2817A-3 | Am2817A-35 |  |

|---------------------|-----------|------------|---------|------------|-----------|------------|--|

| Access<br>Time      | 20        | 0 ns       | 25      | 0 ns       | 35        | 0 ns       |  |

| Supply<br>Tolerance | ±5%       | ±10%       | ±5%     | ±10%       | ±5%       | ±10%       |  |

<u>Amendment</u> Issue Date: May 1986

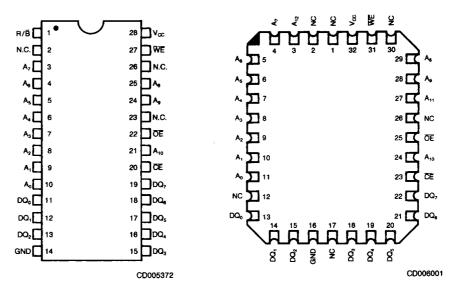

# CONNECTION DIAGRAMS Top View

Note: Pin 1 is marked for orientation.

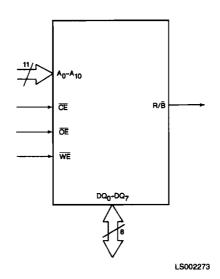

#### LOGIC SYMBOL

V<sub>CC</sub> = Power Supply GND = Ground

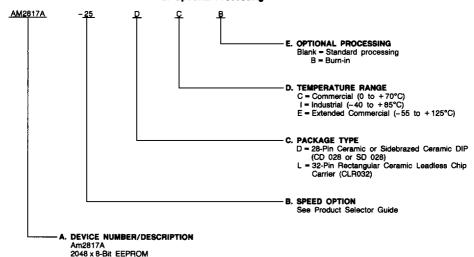

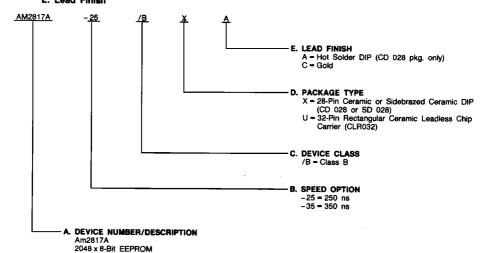

#### ORDERING INFORMATION

#### Standard Products

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of: **A. Device Number**

- B. Speed Option (if applicable)

- C. Package Type

- D. Temperature Range

- E. Optional Processing

| Valid Combinations |                               |  |  |  |  |

|--------------------|-------------------------------|--|--|--|--|

| AM2817A-2          |                               |  |  |  |  |

| AM2817A-20         |                               |  |  |  |  |

| AM2817A            | DC, DCB, DI,<br>DIB, DE, DEB, |  |  |  |  |

| AM2817A-25         | LC, LCB, LI,                  |  |  |  |  |

| AM2817A-3          | LIB, LE, LEB                  |  |  |  |  |

| AM2817A-35         |                               |  |  |  |  |

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

#### ORDERING INFORMATION

#### **APL Products**

AMD products for Aerospace and Defense applications are available in several packages and operating ranges. APL (Approved Products List) products are fully compliant with MIL-STD-883C requirements. CPL (Controlled Products List) products are processed in accordance with MIL-STD-883C, but are inherently non-compliant because of package, solderability, or surface treatment exceptions to those specifications. The order number (Valid Combination) for APL products is formed by a combination of: A. Device Number

- B. Speed Option (if applicable)

- C. Device Class

- D. Package Type

- E. Lead Finish

| Valid Combinations |            |  |  |  |  |

|--------------------|------------|--|--|--|--|

| AM2817A-25         | /BXA.      |  |  |  |  |

| AM2817A-35         | /BXC, /BUC |  |  |  |  |

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations or to check for newly released valid combinations.

**Valid Combinations**

#### **FUNCTIONAL DESCRIPTION**

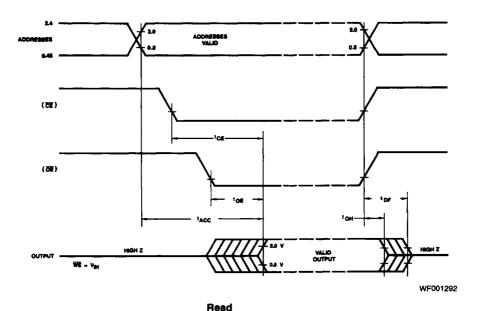

#### Read Mode

The Am2817A has two control functions, both of which must be logically satisfied in order to obtain data at the outputs. Chip Enable ( $\overline{\text{CE}}$ ) is the power control and should be used for device selection. Output Enable ( $\overline{\text{OE}}$ ) is the output control and should be used to gate data to the output pins independent of device selection. Assuming that addresses are stable, address access time ( $t_{\text{ACC}}$ ) is equal to the delay from  $\overline{\text{CE}}$  to output ( $t_{\text{CE}}$ ). Data is available at the outputs  $t_{\text{OE}}$  after the falling edge of  $\overline{\text{OE}}$ , assuming that  $\overline{\text{CE}}$  has been low and addresses have been stable for at least  $t_{\text{ACC}} - t_{\text{OE}}$ .

#### Standby Mode

The Am2817A has a standby mode which reduces the active power dissipation by 60% from 500 mW to 200 mW (values for 0 to 70°C). The Am2817A is placed in the standby mode by applying a TTL HIGH signal to the  $\overline{\text{CE}}$  input. When in the standby mode, the outputs are in a high-impedance state, independent of the  $\overline{\text{OE}}$  input.

#### **Data Protection**

The Am2817A incorporates several features that prevent unwanted write cycles during V<sub>CC</sub> power-up and power-down. These features protect the integrity of the stored data.

To avoid the initiation of a write cycle during  $V_{CC}$  power-up and power-down, a write cycle is locked out for  $V_{CC}$  less than 3.8 volts. It is the user's responsibility to insure that the control levels are logically correct when  $V_{CC}$  is above 3.8 volts.

There is a WE lockout circuit that prevents WE pulses of less than 10 ns\* duration from initiating a write cycle.

When the OE control is in logic zero condition, a write cycle cannot be initiated.

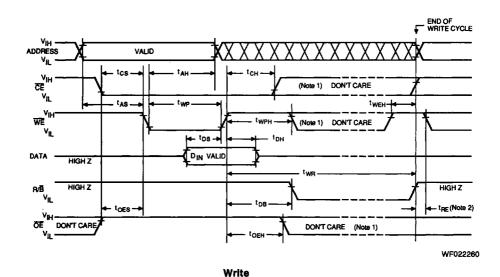

#### Write Mode

The Am2817A has a write cycle that is similar to that of a static RAM. The write cycle is completely self timed, and initiated by a LOW-going pulse on the WE pin. On the falling edge of WE the address information is latched. On the rising edge, the data and the control pins (ČE and ČE) are latched. The Ready/Busy (R/B) pin goes to a logic-LOW level indicating

that the Am2817A is in a write cycle which signals the microprocessor host that the system bus is free for other activity. When R/B̄ goes back to a HIGH, the Am2817A has completed writing and is ready to accept another cycle.

#### **Output OR-Tieing**

To accommodate mulitiple memory connections, a 2-line control function is provided to allow for:

- 1. Low memory power dissipation, and

- 2. Assurance that output bus contention will not occur.

It is recommended that  $\overline{CE}$  be decoded and used as the primary device selecting function, while  $\overline{OE}$  be made a common connection to all devices in the array and connected to the read line from the system control bus. This assures that all deselected memory devices are in their low-power standby mode and that the output pins are only active when data is desired from a particular memory device.

#### Ready/Busy Pin

The Ready/Busy (R/B) pin is an open-drain output which allows two or more R/B signals to be OR-tied together. The value of the pullup resistor required is as follows:

$$R_{pu} = \frac{4.6 \text{ V}}{2.1 \text{ mA} - l_{|L}}$$

III = total VII input current of devices connected to R/B.

A typical pullup resistor value for R/B is 3 k $\Omega$ , assuming I<sub>IL</sub> is less than 0.5 mA.

#### **APPLICATIONS**

During the switch between active and standby conditions, transient current peaks are produced on the rising and falling edges of Chip Enable. The magnitude of these transient current peaks is dependent on the output capacitance loading of the device. A 0.1-µF ceramic capacitor (high frequency, low inherent inductance) should be used on each device between V<sub>CC</sub> and GND to minimize transient effects. In addition, to overcome the voltage droop caused by the inductive effects of the printed circuit board traces on EEPROM arrays, a 4.7-µF bulk electrolytic capacitor should be used between V<sub>CC</sub> and GND for each eight devices. The location of the capacitor should be close to where the power supply is connected to the array.

<sup>\*</sup> This parameter is sampled and not 100% tested.

#### **ABSOLUTE MAXIMUM RATINGS**

| Storage Temperature65              | to   | +150°C  |

|------------------------------------|------|---------|

| Ambient Temperature with Power     |      |         |

| Applied – 65                       | to   | + 135°C |

| Voltage on All Inputs with Respect |      |         |

| to GND+6.50                        | ) to | -06 V   |

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

#### **OPERATING RANGES**

| Industrial (I) Devices                                                                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------|

| Temperature (T <sub>C</sub> )40 to +85°C<br>Supply Voltage (V <sub>CC</sub> ±5%)+4.75 to +5.25 V<br>(V <sub>CC</sub> ±10%)+4.50 to +5.50 V |

| Extended Commercial (E) Devices  Temperature (T <sub>C</sub> )                                                                             |

| Military (M) Devices Temperature (T <sub>C</sub> )                                                                                         |

Operating ranges define those limits between which the

functionality of the device is guaranteed.

## DC CHARACTERISTICS over operating range unless otherwise specified

| Parameter<br>Symbol | Parameter<br>Description               | Test Conditions                             | Min. | Тур. | Max.                | Units |

|---------------------|----------------------------------------|---------------------------------------------|------|------|---------------------|-------|

| IIL                 | Input Leakage Current                  | V <sub>IN</sub> = 0 to 5.5 V                |      |      | 10                  | μΑ    |

| lLO                 | Output Leakage Current                 | V <sub>OUT</sub> = 0 to 5.5 V               |      |      | 10                  | μA    |

| ICC1                | V <sub>CC</sub> Current (Standby)      | CE = V <sub>IH</sub> , OE = V <sub>IL</sub> |      |      | 40                  | mA    |

| ICC2                | V <sub>CC</sub> Current (Active)       | OE = CE = V <sub>IL</sub>                   |      |      | 100                 | mA    |

| lcc                 | V <sub>CC</sub> Current (Write)        | WE L, CE = VIL, OE = VIH                    |      |      | 100                 | mA    |

| VIL                 | Input LOW Voltage                      |                                             | -0.1 |      | .8                  | Volts |

| VIH                 | Input HIGH Voltage                     |                                             | 2.0  |      | V <sub>CC</sub> + 1 | Volts |

| VOL                 | Output LOW Voltage                     | I <sub>OL</sub> = 2.1 mA                    |      |      | .45                 | Volts |

| V <sub>OH</sub>     | Output HIGH Voltage                    | l <sub>OH</sub> = -400 μA                   | 2.4  |      |                     | Volts |

| Vwi                 | Write Inhibit Voltage                  |                                             | 3.3  | 3.8  | 1                   | Volts |

| V <sub>RB</sub>     | R/B Output LOW                         | I <sub>RB</sub> = 2.1 mA                    |      |      | .45                 | Volts |

| C <sub>IN</sub>     | Input Capacitance<br>(Notes 1, 2 & 3)  | V <sub>IN</sub> = 0 V                       |      | 4    | 10                  | pF    |

| C <sub>OUT</sub>    | Output Capacitance<br>(Notes 1, 2 & 3) | OE = CE = VIH, VOUT = 0 V                   |      | 8    | 12                  | pF    |

Notes 1. This parameter is sampled on a periodic basis and not 100% tested.

2. Freq. = 1 MHz @ 25°C.

3. Typical values are for nominal supply voltages.

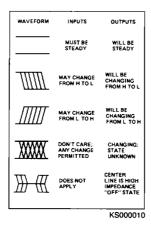

#### **KEY TO SWITCHING WAVEFORMS**

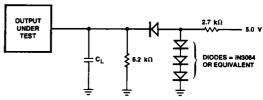

#### **Switching Test Conditions**

Output load: 1 TTL gate and C1 = 100 pF Input pulse levels: 0.45 V to 2.4 V

## Timing Measurements Reference Levels

Input: 0.8 V and 2.0 V Output: 0.8 V and 2.0 V

# SWITCHING TEST CIRCUIT

TC002491

$C_L = 100$  pF, including jig capacitance.

## SWITCHING CHARACTERISTICS over operating range unless otherwise specified

|      |                                  |                                                                     |                                                         |                              |      | m2817A-2, Am2817A<br>m2817A-20 Am2817A-2 |      |      | Am2817A-3,<br>5 Am2817A-35 |      |       |

|------|----------------------------------|---------------------------------------------------------------------|---------------------------------------------------------|------------------------------|------|------------------------------------------|------|------|----------------------------|------|-------|

| No.  | Parameter<br>Symbol              | Parameter<br>Description                                            | Test Condition                                          | ons                          | Min. | Max.                                     | Min. | Max. | Min.                       | Max. | Units |

| REA  | D                                |                                                                     |                                                         |                              |      |                                          |      | •    |                            |      |       |

| 1    | t <sub>ACC</sub><br>(Note 3)     | Address to Output Delay                                             | WE = VIH<br>Output Load: 1 TTL                          | CE = OE<br>= V <sub>IL</sub> |      | 200                                      |      | 250  |                            | 350  | ns    |

| 2    | ¢CE                              | CE to Output Delay                                                  | gate and C <sub>L</sub> = 100 pF<br>Input Rise and Fall | OE = VIL                     |      | 200                                      |      | 250  |                            | 350  | пѕ    |

| 3    | tOE<br>(Note 3)                  | Output Enable to Output Delay                                       | Times: ≤ 20 ns<br>Input Pulse Levels:<br>0.45 to 2.4 V  | CE - VIL                     |      | 75                                       |      | 100  |                            | 120  | ns    |

| 4    | t <sub>DF</sub><br>(Notes 1 & 4) | Output Enable HIGH to Output Float                                  | Timing Measurement<br>Reference Level:                  | CE = VIL                     | 0    | 60                                       | 0    | 60   | 0                          | 80   | ns    |

| 5    | t <sub>OH</sub><br>(Note 1)      | Output Hold from Addresses,<br>CE or OE Whichever<br>Occurred First | Inputs:<br>0.8 V and 2 V<br>Outputs:<br>0.8 V and 2 V   | CE = OE<br>- VIL             | 0    |                                          | 0    |      | 0                          |      | ns    |

| WRIT | TE                               |                                                                     |                                                         |                              |      |                                          |      |      | -                          |      |       |

| 6    | tas                              | Address to Write Setup Time                                         |                                                         |                              | 20   |                                          | 20   |      | 20                         |      | ns    |

| 7    | tcs                              | CE to Write Setup Time                                              |                                                         |                              | 30   |                                          | 30   |      | 30                         |      | ns    |

| 8    | twp                              | Write Pulse Width                                                   |                                                         |                              | 100  |                                          | 100  |      | 100                        |      | ns    |

| 9    | t <sub>A</sub> H                 | Address Hold Time                                                   |                                                         |                              | 50   |                                          | 50   |      | 50                         |      | ns    |

| 10   | t <sub>DS</sub>                  | Data Setup Time                                                     |                                                         |                              | 50   |                                          | 50   |      | 50                         |      | ns    |

| 11   | <sup>†</sup> DH                  | Data Hold Time                                                      |                                                         |                              | 20   |                                          | 20   |      | 20                         |      | ns    |

| 12   | tcн                              | CE Hold Time                                                        |                                                         |                              | 0    |                                          | 0    |      | 0                          |      | ns    |

| 13   | tOES                             | OE Setup Time                                                       |                                                         |                              | 20   |                                          | 20   |      | 20                         |      | ns    |

| 14   | <sup>t</sup> OEH                 | OE Hold Time                                                        |                                                         |                              | 35   |                                          | 35   |      | 35                         |      | ns    |

| 15   | t <sub>DB</sub>                  | Time to Device Busy                                                 |                                                         |                              |      | 100                                      |      | 100  |                            | 100  | ns    |

| 16   | twr                              | Bytes Write Cycle                                                   |                                                         |                              |      | 10                                       |      | 10   |                            | 10   | ms    |

| 17   | twpH                             | Write Control Recovery                                              |                                                         |                              | 50   |                                          | 50   |      | 50                         |      | ns    |

| 18   | t <sub>RE</sub>                  | Write Recovery Time<br>(Note 6)                                     |                                                         |                              | 0    |                                          | 0    |      | 0                          |      | ns    |

| 19   | t <sub>RBO</sub>                 | R/B to Output Time<br>(Notes 2 & 6)                                 |                                                         |                              |      | 50                                       |      | 50   |                            | 50   | ns    |

| 20   | tweh<br>(Note 6)                 | WE HIGH Recovery from R/B                                           |                                                         |                              | 10   |                                          | 10   |      | 10                         |      | μs    |

|      | (Notes 1 & 5)                    | Number of Writes per Byte                                           |                                                         |                              | 10   |                                          | 10   |      | 10                         |      | x1000 |

Notes: 1. This parameter is sampled on a periodic basis to worst-case test conditions and not 100% tested.

- 2. If  $\overline{CE}$  and  $\overline{OE} = V_{IL}$  when R/ $\overline{B}$  is going to  $V_{OH}$ , then DQ<sub>0-7</sub> becomes valid after  $t_{RBO} + t_{ACC}$  ns.

- OE may be delayed up to t<sub>ACC</sub> t<sub>OE</sub> after the falling edge of CE without impact on t<sub>ACC</sub>.

t<sub>DF</sub> is specified from OE or CE, which ever occurs first.

- 5. See Am9864 Reliability Report (PID #06891A).

- 6. This parameter is for information only. It is not tested nor characterized.

Notes: 1.  $\overline{\text{OE}}$  may be delayed up to  $t_{\text{ACC}}$  -  $t_{\text{OE}}$  after the falling edge of  $\overline{\text{CE}}$  without impact on  $t_{\text{ACC}}$ .

2.  $t_{\text{DF}}$  is specified from  $\overline{\text{OE}}$  or  $\overline{\text{CE}}$ , whichever occurs first.

Notes: 1. After twpH and before the end of the Write cycle (R/B̄ goes HIGH), WE, CE, and OĒ are Don't Cares. However, in order to prevent an accidental write when R/B̄ returns HIGH, it is recommended that at least one of the following conditions after twpH: WE HIGH, CE HIGH, or OĒ LOW.

After the Write cycle is completed (R/B HIGH), the user must meet one of the following conditions: OE LOW, CE HIGH, or WE HIGH.

## **GROUP A SUBGROUP TESTING**

## DC CHARACTERISTICS

| Parameter<br>Symbol | Subgroups |

|---------------------|-----------|

| IIL                 | 1, 2, 3   |

| ILO                 | 1, 2, 3   |

| ICC1                | 1, 2, 3   |

| I <sub>CC2</sub>    | 1, 2, 3   |

| lcc                 | 1, 2, 3   |

| VIL                 | 1, 2, 3   |

| ViH                 | 1, 2, 3   |

| VOL                 | 1, 2, 3   |

| V <sub>OH</sub>     | 1, 2, 3   |

| Vwi                 | 7, 8      |

| V <sub>RB</sub>     | 1, 2, 3   |

| C <sub>IN</sub>     | 4         |

| COUT                | 4         |

#### **SWITCHING CHARACTERISTICS**

| No. | Parameter<br>Symbol | Subgroups | No. | Parameter<br>Symbol | Subgroups |

|-----|---------------------|-----------|-----|---------------------|-----------|

| 1   | tACC                | 9, 10, 11 | 9   | t <sub>A</sub> H    | 9, 10, 11 |

| 2   | tCE                 | 9, 10, 11 | 10  | t <sub>DS</sub>     | 9, 10, 11 |

| 3   | <sup>‡</sup> OE     | 9, 10, 11 | 11  | t <sub>DH</sub>     | 9, 10, 11 |

| 4   | tDF                 | 9, 10, 11 | 12  | t <sub>CH</sub>     | 9, 10, 11 |

| 5   | фн                  | 9, 10, 11 | 13  | toes                | 9, 10, 11 |

| 6   | t <sub>AS</sub>     | 9, 10, 11 | 14  | <sup>t</sup> OEH    | 9, 10, 11 |

| 7   | tcs                 | 9, 10, 11 | 15  | t <sub>DB</sub>     | 9, 10, 11 |

| 8   | twp                 | 9, 10, 11 | 16  | twn                 | 9, 10, 11 |

|     |                     |           | 17  | twph                | 9, 10, 11 |

#### **MILITARY BURN-IN**

Military burn-in is in accordance with the current revision of MIL-STD-883, Test Method 1015, Conditions A through E. Test conditions are selected at AMD's option.