## **Low Voltage OR-ing FET Controller**

#### **ISL6146**

The ISL6146 represents a family of OR-ing MOSFET controllers capable of OR-ing voltages from 1V to 18V. Together with suitably sized N-channel power MOSFETs, the ISL6146 increases power distribution efficiency when replacing a power OR-ing diode in high current applications. It provides gate drive voltage for the MOSFET(s) with a fully integrated charge pump.

The ISL6146 allows users to adjust with external resistor(s) the  $V_{OUT}$  -  $V_{IN}$  trip point, which adjusts the control sensitivity to system power supply noise. An open drain FAULT pin will indicate if a conditional or FET fault has occurred.

The ISL6146A and ISL6146B are optimized for very low voltage operation, down to 1V with an additional independent bias of 3V or greater.

The ISL6146C provides a voltage compliant mode of operation down to 3V with programmable Undervoltage Lock Out and Overvoltage Protection threshold levels

The ISL6146D and ISL6146E are like the ISL6146A and ISL6146B respectively but do not have conduction state reporting via the fault output.

**TABLE 1. KEY DIFFERENCES BETWEEN PARTS IN FAMILY**

| PART NUMBER | KEY DIFFERENCES                               |

|-------------|-----------------------------------------------|

| ISL6146A    | Separate BIAS and VIN with Active High Enable |

| ISL6146B    | Separate BIAS and VIN with Active Low Enable  |

| ISL6146C    | VIN with OVP/UVLO Inputs                      |

| ISL6146D    | ISL6146A wo Conduction Monitor & Reporting    |

| ISL6146E    | ISL6146B wo Conduction Monitor & Reporting    |

#### **Features**

- OR-ing Down to 1V and Up to 20V with ISL6146A, ISL6146B, ISL6146D and ISL6146E

- Programmable Voltage Compliant Operation with ISL6146C

- VIN Hot Swap Transient Protection Rating to +24V

- High Speed Comparator Provides Fast <0.3µs Turn-off in Response to Shorts on Sourcing Supply

- Fastest Reverse Current Fault Isolation with 6A Turn-off Current

- · Very Smooth Switching Transition

- Internal Charge Pump to Drive N-channel MOSFET

- User Programmable V<sub>IN</sub> V<sub>OUT</sub> Vth for Noise Immunity

- Open Drain FAULT Output with Delay

- Short between any two of the OR-ing FET Terminals

- GATE Voltage and Excessive FET VDS

- Power-Good Indicator (ISL6146C)

- MSOP and DFN Package Options

### **Applications**

- N+1 Industrial and Telecom Power Distribution Systems

- . Uninterruptable Power Supplies

- · Low Voltage Processor and Memory

- · Storage and Datacom Systems

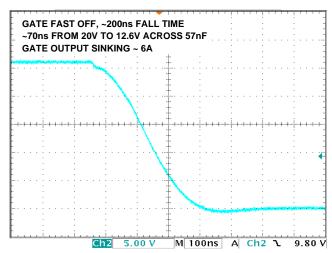

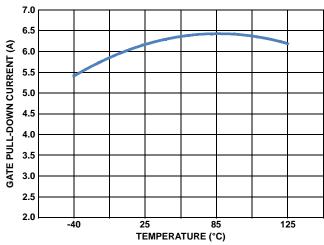

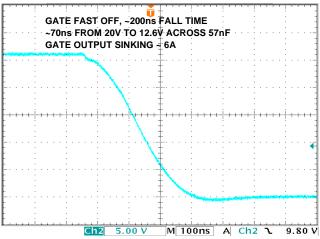

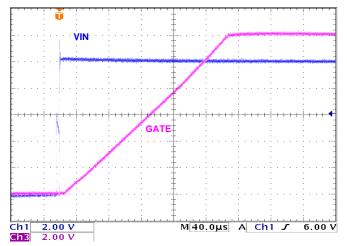

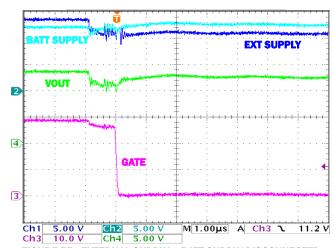

FIGURE 2. ISL6146 GATE HIGH CURRENT PULL-DOWN

## **Block Diagram**

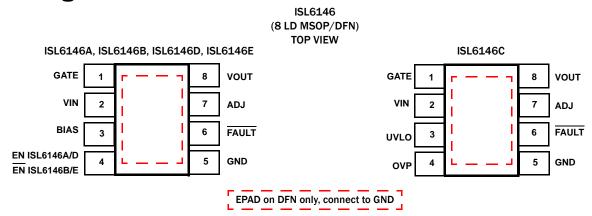

# **Pin Configuration**

## **Pin Descriptions**

| MSOP/<br>DFN                                      | SYMBOL | DESCRIPTION                                                                                                                                                                                                                                                                                                                                |

|---------------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                                 | GATE   | Gate Drive output to the external N-Channel MOSFET generated by the IC internal charge pump. Gate turn-on time is typically <1ms. Allows active control of external N-Channel FET gate to perform OR-ing function. The GATE drive is between $V_{IN}$ + 7V at $V_{IN}$ = 3.3V and $V_{IN}$ +12V at $V_{IN}$ = 18V.                         |

| 2                                                 | VIN    | Connected to the sourcing supply side (OR-ing MOSFET Source), this pin serves as the sense pin to determine the OR'd supply voltage. The OR-ing MOSFET will be turned off when V <sub>IN</sub> becomes lower than V <sub>OUT</sub> by a value more than the externally set threshold or the defaulted internal threshold. Range: OV to 24V |

| 3<br>ISL6146A<br>ISL6146B<br>ISL6146D<br>ISL6146E | BIAS   | Primary bias pin. Connected to an independent voltage supply greater than or equal to 3V and greater than V <sub>IN</sub> . Range: 3.0 to 24V                                                                                                                                                                                              |

| 3<br>ISL6146C                                     | UVLO   | Programmable UVLO protection to prevent premature turn-on prior to VIN being adequately biased. Range: 0V to 24V                                                                                                                                                                                                                           |

| 4<br>ISL6146A<br>ISL6146D                         | EN     | Active high enable input to turn on the FET. Internally pulled low to GND through $2M\Omega.$ Range: 0V to $24V$                                                                                                                                                                                                                           |

# Pin Descriptions (Continued)

| MSOP/<br>DFN              | SYMBOL      | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4<br>ISL6146B<br>ISL6146E | EN          | Active low enable input to turn on the FET. Internally pulled high to BIAS through 2MΩ. Range: 0 to 24V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4<br>ISL6146C             | OVP         | Programmable OV protection to prevent continued operation when the monitored voltage is too high. A back-to-back FET configuration must be employed to implement the OVP capability. Range: OV to 24V                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5                         | GND         | Chip ground reference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 6                         | FAULT       | Open-Drain pull-down fault indicating output with internal on chip filtering ( $T_{FLT}$ ). The ISL6146 fault detection circuitry pulls down this pin to GND as it detects a fault or a disabled input (EN = '0' or $\overline{EN}$ = '1'). Different types of faults and their detection mechanisms are discussed in more detail on page 17. These faults include: a. GATE is OFF (GATE < $V_{IN}$ +0.2V) when enabled [this condition is not reported on the ISL6146D and ISL6146E] b. $V_{IN}$ - $V_{OUT}$ > 0.57V when ON. c. FET G-D or G-S or D-S shorts. d. $V_{IN}$ < POR <sub>L2H</sub> e. $V_{IN}$ < $V_{OUT}$ f. Over-Temperature Range: 0 to $V_{OUT}$ |

| 7                         | ADJ         | Resistor programmable $V_{IN}$ - $V_{OUT}$ Voltage Threshold (Vth) of the High Speed Comparator. This pin is either directly connected to VOUT or can be connected through a $5k\Omega$ to $100k\Omega$ resistor to GND. Allows for adjusting the voltage difference threshold to prevent unintended turn-off of the pass FET due to normal system voltage fluctuations. Range: 0.4 to $V_{OUT}$                                                                                                                                                                                                                                                                   |

| 8                         | VOUT        | The second sensing node for external FET control and connected to the Load side (OR-ing MOSFET Drain). This is the common connection point for multiple paralleled supplies. V <sub>OUT</sub> is compared to V <sub>IN</sub> to determine when the OR-ing FET has to be turned off. Range: 0V to 24V                                                                                                                                                                                                                                                                                                                                                               |

| PAD                       | Thermal Pad | Connect to GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

# **Ordering Information**

| PART NUMBER<br>(Notes 1, 2, 3) | PART<br>MARKING | TEMP RANGE<br>(°C) | PACKAGE<br>(Pb-free)       | PKG.<br>DWG. # |

|--------------------------------|-----------------|--------------------|----------------------------|----------------|

| ISL6146AFUZ                    | 6146A           | -40 to +125        | 8 Ld MSOP                  | M8.118         |

| ISL6146AFUZ-T                  | 6146A           | -40 to +125        | 8 Ld MSOP Tape and Reel    | M8.118         |

| ISL6146AFUZ-T7A                | 6146A           | -40 to +125        | 8 Ld MSOP Tape and Reel    | M8.118         |

| ISL6146AFUZ-TK                 | 6146A           | -40 to +125        | 8 Ld MSOP Tape and Reel    | M8.118         |

| ISL6146AFRZ                    | 46AF            | -40 to +125        | 8 Ld 3x3 DFN               | L8.3x3J        |

| ISL6146AFRZ-T                  | 46AF            | -40 to +125        | 8 Ld 3x3 DFN Tape and Reel | L8.3x3J        |

| ISL6146AFRZ-T7A                | 46AF            | -40 to +125        | 8 Ld 3x3 DFN Tape and Reel | L8.3x3J        |

| ISL6146AFRZ-TK                 | 46AF            | -40 to +125        | 8 Ld 3x3 DFN Tape and Reel | L8.3x3J        |

| ISL6146BFUZ                    | 6146B           | -40 to +125        | 8 Ld MSOP                  | M8.118         |

| ISL6146BFUZ-T                  | 6146B           | -40 to +125        | 8 Ld MSOP Tape and Reel    | M8.118         |

| ISL6146BFUZ-T7A                | 6146B           | -40 to +125        | 8 Ld MSOP Tape and Reel    | M8.118         |

| ISL6146BFUZ-TK                 | 6146B           | -40 to +125        | 8 Ld MSOP Tape and Reel    | M8.118         |

| ISL6146BFRZ                    | 46BF            | -40 to +125        | 8 Ld 3x3 DFN               | L8.3x3J        |

| ISL6146BFRZ-T                  | 46BF            | -40 to +125        | 8 Ld 3x3 DFN Tape and Reel | L8.3x3J        |

| ISL6146BFRZ-T7A                | 46BF            | -40 to +125        | 8 Ld 3x3 DFN Tape and Reel | L8.3x3J        |

| SL6146BFRZ-TK                  | 46BF            | -40 to +125        | 8 Ld 3x3 DFN Tape and Reel | L8.3x3J        |

| SL6146CFUZ                     | 6146C           | -40 to +125        | 8 Ld MSOP                  | M8.118         |

# Ordering Information (Continued)

| PART NUMBER (Notes 1, 2, 3) | PART<br>MARKING   | TEMP RANGE<br>(°C)                                                                            | PACKAGE<br>(Pb-free)                       | PKG.<br>DWG.#    |  |

|-----------------------------|-------------------|-----------------------------------------------------------------------------------------------|--------------------------------------------|------------------|--|

| SL6146CFUZ-T                | 6146C             | -40 to +125                                                                                   | 8 Ld MSOP Tape and Reel                    | M8.118           |  |

| SL6146CFUZ-T7A              | 6146C             | -40 to +125                                                                                   | 8 Ld MSOP Tape and Reel                    | M8.118           |  |

| SL6146CFUZ-TK               | 6146C             | -40 to +125                                                                                   | 8 Ld MSOP Tape and Reel                    | M8.118           |  |

| SL6146CFRZ                  | 46CF              | -40 to +125                                                                                   | 8 Ld 3x3 DFN                               | L8.3x3J          |  |

| SL6146CFRZ-T                | 46CF              | -40 to +125                                                                                   | 8 Ld 3x3 DFN Tape and Reel                 | L8.3x3J          |  |

| SL6146CFRZ-T7A              | 46CF              | -40 to +125                                                                                   | 8 Ld 3x3 DFN Tape and Reel                 | L8.3x3J          |  |

| SL6146CFRZ-TK               | 46CF              | -40 to +125                                                                                   | 8 Ld 3x3 DFN Tape and Reel                 | L8.3x3J          |  |

| SL6146DFUZ                  | 6146D             | -40 to +125                                                                                   | 8 Ld MSOP                                  | M8.118           |  |

| SL6146DFUZ-T                | 6146D             | -40 to +125                                                                                   | 8 Ld MSOP Tape and Reel                    | M8.118           |  |

| SL6146DFUZ-T7A              | 6146D             | -40 to +125                                                                                   | 8 Ld MSOP Tape and Reel                    | M8.118           |  |

| SL6146DFUZ-TK               | 6146D             | -40 to +125                                                                                   | 8 Ld MSOP Tape and Reel                    | M8.118           |  |

| SL6146DFRZ                  | 46DF              | -40 to +125                                                                                   | 8 Ld 3x3 DFN                               | L8.3x3J          |  |

| SL6146DFRZ-T                | 46DF              | -40 to +125                                                                                   | 8 Ld 3x3 DFN Tape and Reel                 | L8.3x3J          |  |

| SL6146DFRZ-T7A              | 46DF              | -40 to +125                                                                                   | 8 Ld 3x3 DFN Tape and Reel                 | L8.3x3J          |  |

| SL6146DFRZ-TK               | 46DF              | -40 to +125                                                                                   | 8 Ld 3x3 DFN Tape and Reel                 | L8.3x3J          |  |

| SL6146EFUZ                  | 6146E             | -40 to +125                                                                                   | 8 Ld MSOP                                  | M8.118           |  |

| SL6146EFUZ-T                | 6146E             | -40 to +125                                                                                   | 8 Ld MSOP Tape and Reel                    | M8.118           |  |

| SL6146EFUZ-T7A              | 6146E             | -40 to +125                                                                                   | 8 Ld MSOP Tape and Reel                    | M8.118           |  |

| SL6146EFUZ-TK               | 6146E             | -40 to +125                                                                                   | 8 Ld MSOP Tape and Reel                    | M8.118           |  |

| SL6146EFRZ                  | 46EF              | -40 to +125                                                                                   | 8 Ld 3x3 DFN                               | L8.3x3J          |  |

| SL6146EFRZ-T                | 46EF              | -40 to +125                                                                                   | 8 Ld 3x3 DFN Tape and Reel                 | L8.3x3J          |  |

| SL6146EFRZ-T7A              | 46EF              | -40 to +125                                                                                   | 8 Ld 3x3 DFN Tape and Reel                 | L8.3x3J          |  |

| SL6146EFRZ-TK               | 46EF              | -40 to +125                                                                                   | 8 Ld 3x3 DFN Tape and Reel                 | L8.3x3J          |  |

| SL6146AEVAL1Z               | ISL6146A Evaluat  | ion Board (If desired w                                                                       | rith ISL6146D, please contact support)     | 1                |  |

| SL6146BEVAL1Z               | ISL6146B Evaluat  | ion Board (If desired w                                                                       | rith ISL6146E, please contact support)     |                  |  |

| SL6146CEVAL1Z               | ISL6146C Evaluat  | ISL6146C Evaluation Board                                                                     |                                            |                  |  |

| SL6146DEVAL1Z               | 1 pair of ISL6146 | 1 pair of ISL6146D Mini Development Boards (If desired with ISL6146A, please contact support) |                                            |                  |  |

| SL6146EEVAL1Z               | 1 pair of ISL6146 | E Mini Development Bo                                                                         | pards (If desired with ISL6146B, please of | contact support) |  |

#### NOTES:

- 1. Please refer to TB347 for details on reel specifications.

- These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte

tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil

Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- 3. For Moisture Sensitivity Level (MSL), please see device information page for ISL6146. For more information on MSL please see techbrief TB363.

# **Table of Contents**

| Absolute Maximum Ratings                                                          | . 6 |

|-----------------------------------------------------------------------------------|-----|

| Thermal Information                                                               | . 6 |

| Recommended Operating Conditions                                                  | . 6 |

| Electrical Specifications                                                         | . 6 |

| Typical Performance Curves                                                        | . 9 |

| Functional Description                                                            |     |

| Applications Information  Power-Up Considerations.  Typical Applications Circuits | .18 |

| ISL6146 Evaluation Platforms                                                      |     |

| Revision History                                                                  | 26  |

| About Intersil                                                                    | 26  |

| Package Outline Drawing<br>L8.3x3J                                                | .27 |

### **Absolute Maximum Ratings**

| BIAS, VIN, VOUT                                  | -0.3V to +24V            |

|--------------------------------------------------|--------------------------|

| GATE                                             | 0.3V to 40V              |

| EN, EN, UVLO, OVP                                | 0.3V to +24V             |

| ADJ                                              | 0.3V to V <sub>OUT</sub> |

| FAULT                                            | 0.3V to V <sub>OUT</sub> |

| ESD Rating                                       |                          |

| Human Body Model (Tested per JESD22-A114E)       | 2.5kV                    |

| Machine Model (Tested per JESD22-A115-A)         | 250V                     |

| Latch Up (Tested per JESD-78B; Class 2, Level A) | 100mA                    |

|                                                  |                          |

#### **Thermal Information**

| Thermal Resistance (Typical)              | $\theta_{JA}$ (°C/W) | $\theta_{JC}$ (° C/W) |

|-------------------------------------------|----------------------|-----------------------|

| MSOP Package (Notes 4, 7)                 | 140                  | 41                    |

| DFN Package (Notes 5, 6)                  | 46                   | 5                     |

| Maximum Junction Temperature (Plastic Pac | kage)                | +150°C                |

| Storage Temperature Range                 | 6                    | 65°C to +150°C        |

### **Recommended Operating Conditions**

| Bias Supply Voltage Range           | +3V to +20V   |

|-------------------------------------|---------------|

| OR'd Supply Voltage Range           | . +1V to BIAS |

| Temperature Range (T <sub>A</sub> ) | °C to +125°C  |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES

- 4.  $\theta_{\text{JA}}$  is measured with the component mounted on a high effective thermal conductivity test board in free air. See Tech Brief <u>TB379</u> for details.

- 5. θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief TB379.

- 6. For  $\theta_{\text{JC}}$ , the "case temp" location is the center of the exposed metal pad on the package underside.

- 7. For  $\theta_{\text{IC}}$ , the "case temp" location is taken at the package top center

# **Electrical Specifications** $V_{CC}$ = BIAS = 12V, unless otherwise stated. $T_A$ = +25°C to +85°C. Boldface limits apply over the operating temperature range, -40°C to +125°C.

| SYMBOL                | PARAMETERS                              | TEST CONDITIONS                                                                       | MIN<br>(Note 8)     | TYP                  | MAX<br>(Note 8)        | UNITS |

|-----------------------|-----------------------------------------|---------------------------------------------------------------------------------------|---------------------|----------------------|------------------------|-------|

| BIAS                  |                                         | ·                                                                                     | •                   | •                    |                        |       |

| POR <sub>L2H</sub>    | POR Rising                              | BIAS Rising, GATE Rising                                                              | 1.9                 | 2.5                  | 2.95                   | V     |

| PORHYS                | POR Hysteresis                          |                                                                                       |                     | 189                  |                        | mV    |

| IBIAS_en_18           | ISL6146A/B/D/E BIAS Current             | BIAS, $V_{IN}$ = 18V, ADJ, $V_{OUT}$ = 16.98V, enabled                                |                     | 3.6                  | 5                      | mA    |

| IVIN_en_18            | ISL6146A/B/D/E V <sub>IN</sub> Current  | BIAS, $V_{IN}$ = 18V, ADJ, $V_{OUT}$ = 16.98V, enabled                                |                     | 25                   | 40                     | μΑ    |

| IVIN_en_18            | ISL6146C V <sub>IN</sub> Current        | V <sub>IN</sub> = 18V, ADJ, V <sub>OUT</sub> = 16.98V, enabled                        |                     | 3                    | 4.5                    | mA    |

| IVOUT_en_18           | ISL6146A/B/D/E V <sub>OUT</sub> Current | BIAS, V <sub>IN</sub> = 18V, V <sub>OUT</sub> = 16.98V, enabled                       |                     | 14                   | 20                     | μΑ    |

| VOUT_en_18            | ISL6146C V <sub>OUT</sub> Current       | V <sub>IN</sub> = 18V, V <sub>OUT</sub> = 16.98V, enabled                             |                     | 400                  | 500                    | μΑ    |

| IBIAS_den_18          | ISL6146A/B/D/E BIAS Current             | BIAS, $V_{IN}$ = 18V, ADJ, $V_{OUT}$ = 16.98V, disabled                               |                     | 1.7                  | 3                      | mA    |

| IVIN_den_18           | ISL6146A/B/D/E V <sub>IN</sub> Current  | BIAS, $V_{IN}$ = 18V, ADJ, $V_{OUT}$ = 16.98V, disabled                               |                     | 27                   | 37                     | μΑ    |

| IVIN_den_18           | ISL6146C V <sub>IN</sub> Current        | V <sub>IN</sub> = 18V, ADJ, V <sub>OUT</sub> = 16.98V, disabled                       |                     | 1.3                  | 1.5                    | mA    |

| IVOUT_den_18          | ISL6146A/B/D/E V <sub>OUT</sub> Current | BIAS, V <sub>IN</sub> = 18V, V <sub>OUT</sub> = 16.98V, disabled                      |                     | 14                   | 20                     | μΑ    |

| IVOUT_den_18          | ISL6146C V <sub>OUT</sub> Current       | V <sub>IN</sub> = 18V, V <sub>OUT</sub> = 16.98V, disabled                            |                     | 385                  | 500                    | μΑ    |

| t <sub>BIAS2GTE</sub> | BIAS to GATE Delay                      | BIAS > POR <sub>L2H</sub> to GATE Rising                                              |                     | 150                  | 210                    | μs    |

| GATE                  |                                         |                                                                                       |                     |                      | 11                     |       |

| V <sub>GH_3</sub>     | Charge Pump Voltage                     | V <sub>IN</sub> , BIAS = 3V V <sub>IN</sub> - V <sub>OUT</sub> > V <sub>FWD_VR</sub>  | V <sub>IN</sub> +5V | V <sub>IN</sub> +7V  | V <sub>IN</sub> +10.5V | V     |

| V <sub>GH_12</sub>    | Charge Pump Voltage                     | V <sub>IN</sub> , BIAS = 12V V <sub>IN</sub> - V <sub>OUT</sub> > V <sub>FWD_VR</sub> | V <sub>IN</sub> +9V | V <sub>IN</sub> +10V | V <sub>IN</sub> +17.5V | V     |

| V <sub>GH_18</sub>    | Charge Pump Voltage                     | V <sub>IN</sub> , BIAS = 18V V <sub>IN</sub> - V <sub>OUT</sub> > V <sub>FWD_VR</sub> | V <sub>IN</sub> +9V | V <sub>IN</sub> +10V | V <sub>IN</sub> +18V   | V     |

| V <sub>GL</sub>       | Low Voltage Level                       | V <sub>IN</sub> - V <sub>OUT</sub> < OV                                               |                     | 0                    | 0.1                    | V     |

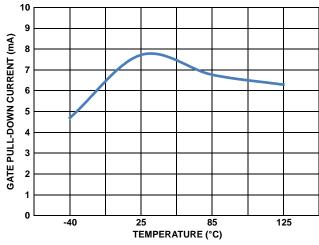

| I <sub>PDL</sub>      | Low Pull-Down Current                   | V <sub>IN</sub> = 12V, V <sub>OUT</sub> = 12.2V ADJ = 11V                             | 5                   | 8.4                  | 13                     | mA    |

| I <sub>PDH</sub>      | High Pull-Down Current                  | V <sub>IN</sub> falling from 12V to 10V in 2μs                                        | 3.5                 | 6.5                  |                        | Α     |

| t <sub>toff</sub>     | Fast Turn-off Time                      | $V_{IN} = V_{BIAS} = 12V$ , $V_{GATE} = 18V$ to 10V, $C_{GATE} = 57nF$                |                     | 65                   | 130                    | ns    |

**Electrical Specifications**  $V_{CC}$  = BIAS = 12V, unless otherwise stated.  $T_A$  = +25°C to +85°C. Boldface limits apply over the operating temperature range, -40°C to +125°C. (Continued)

| SYMBOL                   | PARAMETERS                                                              | TEST CONDITIONS                                                                                                                                      | MIN<br>(Note 8) | TYP  | MAX<br>(Note 8) | UNITS |

|--------------------------|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------|-----------------|-------|

| t <sub>toffs</sub>       | Slow Turn-off Time                                                      | V <sub>IN</sub> = V <sub>BIAS</sub> = 12V, V <sub>GATE</sub> = 18V to 10V,<br>C <sub>GATE</sub> = 57nF                                               |                 | 58   | 80              | μs    |

| I <sub>ON</sub>          | Turn-On Current                                                         | BIAS = 12V, VG = 0V                                                                                                                                  |                 | 1    |                 | mA    |

|                          |                                                                         | BIAS = 12V, VG = 20V                                                                                                                                 |                 | 0.15 |                 | mA    |

| V <sub>VG_FLTr</sub>     | GATE to V <sub>IN</sub> Rising Fault Voltage                            | GATE > V <sub>IN</sub> , enabled, FLT output is high.<br>(Does not apply to ISL6146D and ISL6146E)                                                   | 320             | 440  | 560             | mV    |

| V <sub>VG_FLTf</sub>     | GATE to V <sub>IN</sub> Falling Fault Voltage                           | GATE > V <sub>IN</sub> , enabled, FLT output is low.<br>(Does not apply to ISL6146D and ISL6146E)                                                    | 140             | 220  | 300             | mV    |

| CONTROL AND F            | REGULATION I/O                                                          |                                                                                                                                                      |                 |      |                 |       |

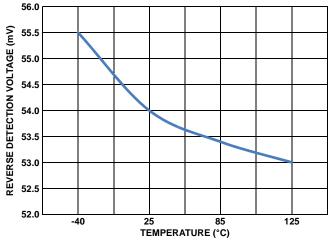

| V <sub>Rr</sub>          | Reverse Voltage Detection<br>Rising V <sub>OUT</sub> Threshold          | V <sub>OUT</sub> rising                                                                                                                              | 35              | 57   | 79              | mV    |

| V <sub>Rf</sub>          | Reverse Voltage Detection<br>Falling V <sub>OUT</sub> Threshold         | V <sub>OUT</sub> falling                                                                                                                             | 10              | 30   | 51              | mV    |

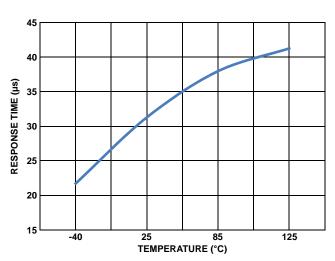

| t <sub>Rs</sub>          | Reverse Voltage Detection Response<br>Time                              |                                                                                                                                                      |                 | 10   |                 | μs    |

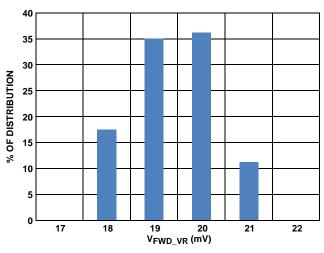

| V <sub>FWD_VR</sub>      | Amplifier Forward Voltage Regulation                                    | ISL6146 controls voltage across FET $V_{DS}$ to $V_{FWD\_VR}$ during static forward operation at loads resulting in Id* $r_{DS(ON)}$ < $V_{FWD\_VR}$ | 11              | 19   | 28              | mV    |

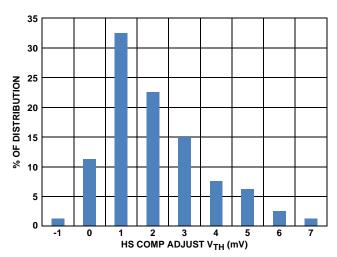

| V <sub>OS_HS</sub>       | HS Comparator Input Offset Voltage                                      |                                                                                                                                                      | -14             | 0.7  | 14              | mV    |

| V <sub>TH(HS5k)</sub>    | ADJ Adjust Threshold with 5k to GND                                     | $R_{ADJ} = 5k\Omega$ to GND                                                                                                                          | 0.57            | 0.8  | 1.1             | V     |

| V <sub>TH(HS100k)</sub>  | ADJ Adjust Threshold with 100k to GND                                   | $R_{ADJ} = 100k\Omega$ to GND                                                                                                                        | 10              | 40   | 95              | mV    |

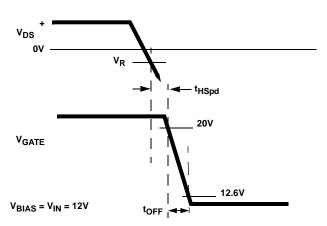

| t <sub>HSpd</sub>        | HS Comparator Response Time                                             | V <sub>OUT</sub> > V <sub>IN</sub> , 1ns transition, 5V differential                                                                                 |                 | 170  |                 | ns    |

| V <sub>FWD_FLT</sub>     | V <sub>IN</sub> to V <sub>OUT</sub> Forward Fault Voltage               | V <sub>IN</sub> > V <sub>OUT</sub> , GATE is fully on, FLT output is low                                                                             | 330             | 450  | 570             | mV    |

| V <sub>FWD_FLT_HYS</sub> | V <sub>IN</sub> to V <sub>OUT</sub> Forward Fault Voltage<br>Hysteresis | V <sub>IN</sub> > V <sub>OUT</sub> , GATE is fully on, FLT output is high                                                                            |                 | 44   |                 | mV    |

| FAULT OUTPUT             |                                                                         |                                                                                                                                                      | 1               |      | 1               | .1    |

| I <sub>FLT_SINK</sub>    | FAULT Sink Current                                                      | BIAS = 18V FAULT = 0.5V, V <sub>IN</sub> < V <sub>OUT</sub> , V <sub>GATE</sub> = V <sub>GL</sub>                                                    | 5               | 9    |                 | mA    |

| I <sub>FLT_LEAK</sub>    | FAULT Leakage Current                                                   | FAULT = "V <sub>FLT_H</sub> ", V <sub>IN</sub> > V <sub>OUT</sub> , V <sub>GATE</sub> = V <sub>IN</sub> + V <sub>GQP</sub>                           |                 | 0.04 | 10              | μΑ    |

| t <sub>FLT_L2H</sub>     | FAULT Low to High Delay                                                 | GATE = V <sub>GQP</sub> to FAULT output is high                                                                                                      |                 | 10   | 23              | μs    |

| t <sub>FLT_H2L</sub>     | FAULT High to Low Delay                                                 | GATE = V <sub>IN</sub> to FAULT output is low                                                                                                        |                 | 1.7  | 3               | μs    |

| ENABLE UVLO/C            | VP/ADJ INPUTS                                                           |                                                                                                                                                      | 1               |      | 1               | .1    |

| VthRa                    | ISL6146A/D EN Rising Vth                                                |                                                                                                                                                      | 580             | 606  | 631             | mV    |

| VthR_hysa                | ISL6146A/D EN Vth Hysteresis                                            |                                                                                                                                                      |                 | -90  |                 | mV    |

| VthFb                    | ISL6146B/E EN Falling Vth                                               |                                                                                                                                                      | 580             | 606  | 631             | mV    |

| VthF_hysb                | ISL6146B/E EN Vth Hysteresis                                            |                                                                                                                                                      |                 | +90  |                 | mV    |

| VthFc                    | ISL6146C OVP Falling Vth                                                |                                                                                                                                                      | 580             | 606  | 631             | mV    |

| VthF_hysc                | ISL6146C OVP Vth Hysteresis                                             |                                                                                                                                                      |                 | +90  |                 | mV    |

| VthRc                    | ISL6146C UVLO Rising Vth                                                |                                                                                                                                                      | 580             | 606  | 631             | mV    |

| VthR_hysc                | ISL6146C UVLO Vth Hysteresis                                            |                                                                                                                                                      |                 | -90  |                 | mV    |

| t <sub>EN2GTER</sub>     | EN/UVLO Rising to GATE Rising Delay                                     |                                                                                                                                                      |                 | 10   | 12              | μs    |

|                          | EN/OVP Falling to GATE Rising Delay                                     |                                                                                                                                                      |                 | 9    | 12              | μs    |

**Electrical Specifications**  $V_{CC}$  = BIAS = 12V, unless otherwise stated.  $T_A$  = +25°C to +85°C. Boldface limits apply over the operating temperature range, -40°C to +125°C. (Continued)

| SYMBOL               | PARAMETERS                            | TEST CONDITIONS                                   | MIN<br>(Note 8) | TYP  | MAX<br>(Note 8) | UNITS |

|----------------------|---------------------------------------|---------------------------------------------------|-----------------|------|-----------------|-------|

| t <sub>EN2GTEF</sub> | EN/UVLO Falling to GATE Falling Delay |                                                   |                 | 2    | 4               | μs    |

|                      | EN/OVP Rising to GATE Falling Delay   |                                                   |                 | 2    | 4               | μs    |

| Ren_h                | ENABLE Pull-Down Resistor             | ISL6146A, ISL6146D                                |                 | 2    |                 | МΩ    |

| Ren_I                | ENABLE Pull-Up Resistor               | ISL6146B, ISL6146E                                |                 | 2    |                 | МΩ    |

| Vadj                 | ADJ Pin Voltage                       | $R_{ADJ}$ 5k $\Omega$ to 100k $\Omega$            |                 | 0.4  |                 | V     |

| Radj                 | ADJ Pull-Up Resistor                  | Internal ADJ Pull-up Resistor to V <sub>OUT</sub> |                 | 3.85 |                 | МΩ    |

| OTS                  | Over-Temperature Sense                | Fault signals in operation                        |                 | 140  |                 | °C    |

| OTS <sub>HYS</sub>   | Over-Temperature Sense Hysteresis     |                                                   |                 | 20   |                 | °C    |

| HTS                  | High Temperature Sense                | Fault signals upon enabling                       |                 | 125  |                 | °C    |

#### NOTE:

<sup>8.</sup> Compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design.

## **Typical Performance Curves**

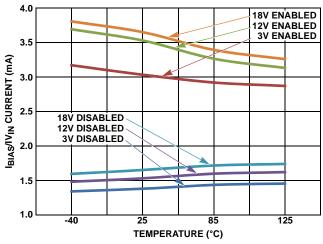

FIGURE 3. ISL6146A/B/D/E BIAS AND ISL6146C  $\rm V_{IN}$  CURRENT vs TEMPERATURE

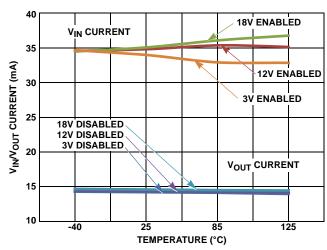

FIGURE 4. ISL6146A/B/C/D/E  $V_{\mbox{\scriptsize IN}}$  AND  $V_{\mbox{\scriptsize OUT}}$  CURRENT vs TEMPERATURE

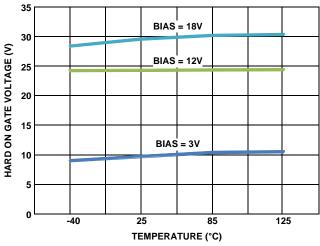

FIGURE 5. GATE VOLTAGE vs TEMPERATURE

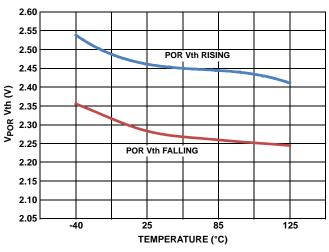

FIGURE 6. POR Vth RISING AND FALLING VOLTAGE

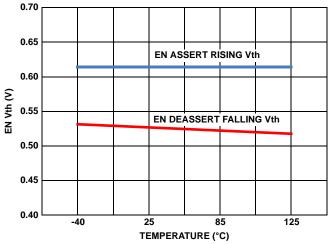

FIGURE 7. ISL6146A/D EN Vth vs TEMPERATURE

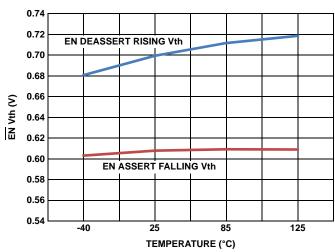

FIGURE 8. ISL6146B/E EN Vth vs TEMPERATURE

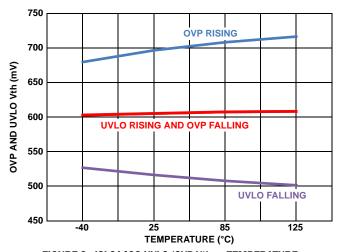

FIGURE 9. ISL6146C UVLO/OVP Vth vs TEMPERATURE

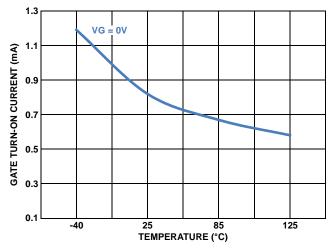

FIGURE 10. GATE TURN-ON CURRENT VIN = 12V

FIGURE 11. GATE HARD TURN-OFF CURRENT

FIGURE 12. GATE SLOW TURN-OFF CURRENT

FIGURE 13. INCREASING REVERSE VOLTAGE DETECTION Vth

FIGURE 14. REVERSE VOLTAGE RESPONSE TIME

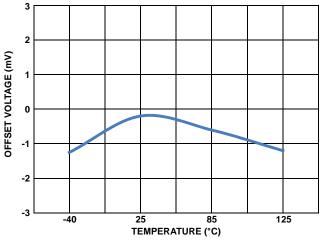

FIGURE 15. HIGH SPEED COMPARATOR OFFSET VOLTAGE

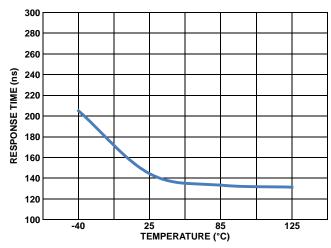

FIGURE 16. HIGH SPEED COMPARATOR RESPONSE TIME

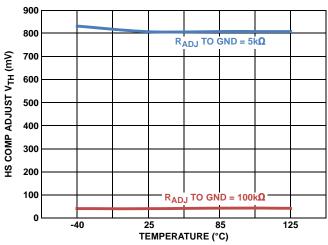

FIGURE 17. HS COMPARATOR ADJUSTABLE Vth

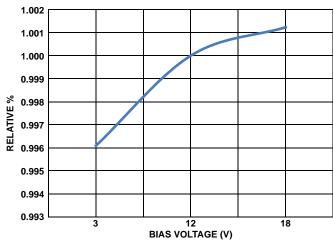

FIGURE 18. EN/EN/OVP/UVLO Vth DELTA vs BIAS VOLTAGE NORMALIZED TO BIAS = 12V

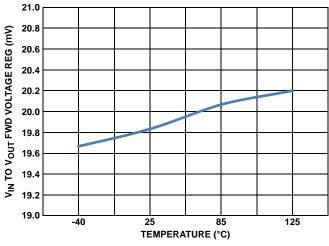

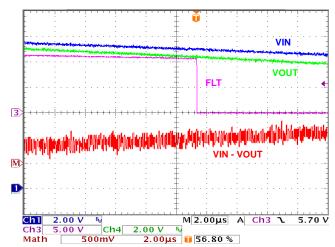

FIGURE 19. FORWARD VOLTAGE REGULATION

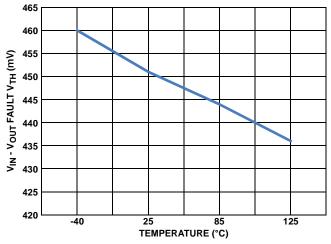

FIGURE 20.  $V_{\text{IN}}$  to  $V_{\text{OUT}}$  forward fault voltage

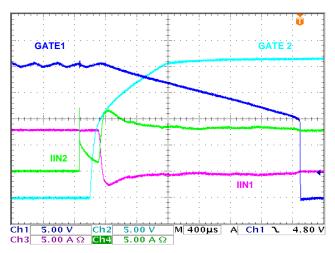

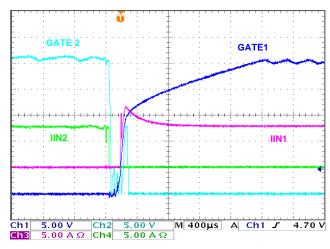

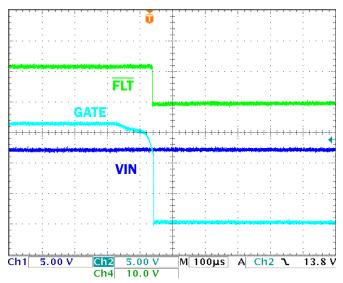

FIGURE 21. ISL6146C SLOW RAMP CONNECT 12V OR-ing

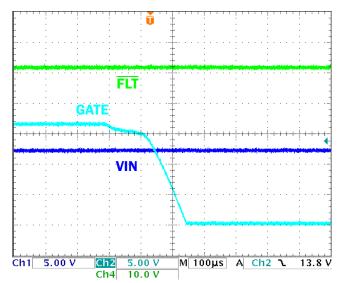

FIGURE 22. ISL6146C SLOW RAMP DISCONNECT 12V OR-ing

FIGURE 23. ISL6146C HOT SWAP CONNECT 12V OR-ing

FIGURE 24. ISL6146C HOT DISCONNECT 12V OR-ing

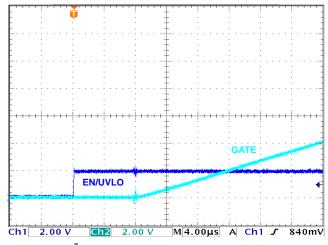

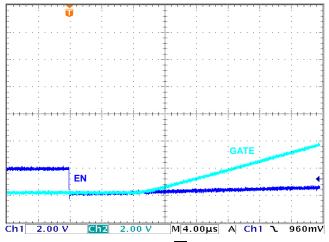

FIGURE 25.  $\bar{I}SL6146A/D$  EN/ISL6146C UVLO TO GATE ON DELAY

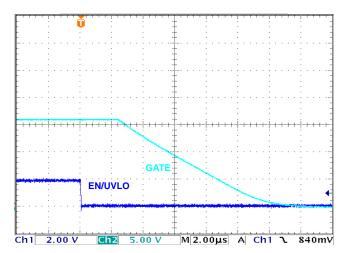

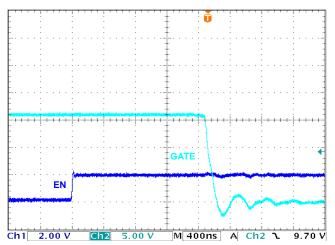

FIGURE 26. ISL6146A/D EN/ISL6146C UVLO TO GATE OFF DELAY

FIGURE 27. ISL6146B/E EN TO GATE ON DELAY

FIGURE 28. ISL6146B/E EN TO GATE OFF DELAY

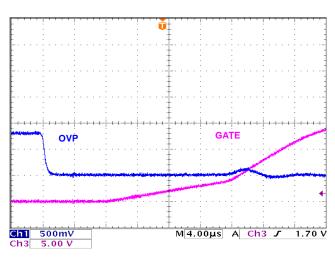

FIGURE 29. ISL6146C OVP TO GATE ON DELAY

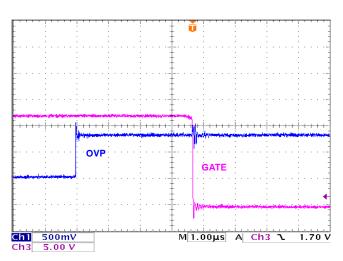

FIGURE 30. ISL6146C OVP TO GATE OFF DELAY

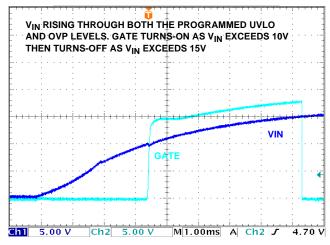

FIGURE 31. ISL6146C RISING  $V_{\mbox{\scriptsize IN}}$ , UVLO AND OVP FUNCTION

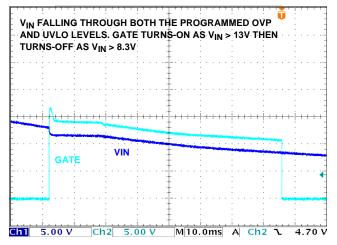

FIGURE 32. ISL6146C FALLING,  $V_{\mbox{\scriptsize IN}}$  OVP and UVLO FUNCTION

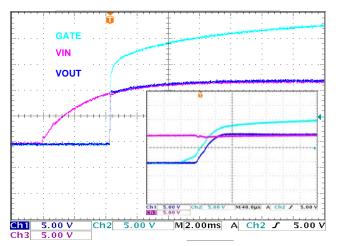

FIGURE 33. BACK-TO-BACK FET TURN\_ON DETAIL

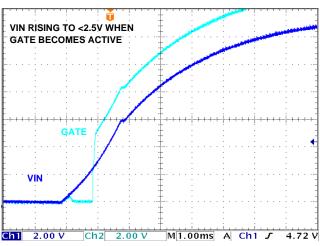

FIGURE 34. ISL6146 RISING POR Vth

FIGURE 35. FAST GATE TURN-OFF WITH 57nF GATE

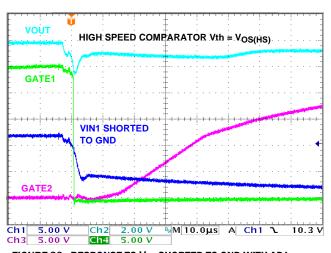

FIGURE 36. RESPONSE TO  $\rm V_{\sc in}$  shorted to GND with adj shorted to  $\rm V_{\sc out}$

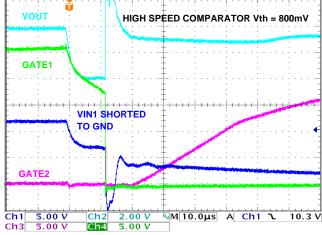

FIGURE 37. RESPONSE TO  $V_{\mbox{\footnotesize{IN}}}$  SHORTED TO GND WITH ADJ  $5k\Omega$  TO GND

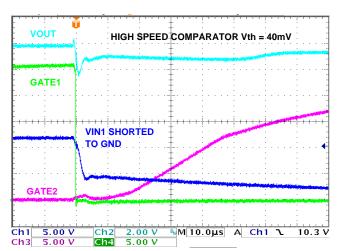

FIGURE 38. RESPONSE TO  $V_{IN}$  SHORTED TO GND WITH ADJ 100k $\Omega$  TO GND

FIGURE 39. V<sub>IN</sub> HOT SWAPPED TO GATE WITH BIAS = 12V NO LOAD

FIGURE 40. FAULT ASSERTING  $V_{IN}$  TO  $V_{OUT} > V_{FWD\_FLT}$

FIGURE 41. HIGH SPEED COMPARATOR OFFSET VOLTAGE DISTRIBUTION

FIGURE 42. FORWARD REGULATION VOLTAGE DISTRIBUTION

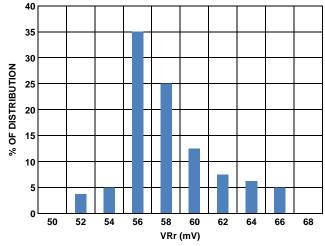

FIGURE 43. REVERSE DETECTION RISING VOLTAGE DISTRIBUTION

FIGURE 44. FAST RAMP REVERSE PROTECTION TIMING DIAGRAM

FIGURE 45. ISL6146A FLT RESPONSE TO NON-CONDUCTION

FIGURE 46. ISL6146D FLT RESPONSE TO NON-CONDUCTION

### **Functional Description**

#### **Functional Overview**

In a redundant power distribution system, similar potential and parallel power supplies each contribute to the load current through various active and passive current sharing schemes. Typically OR-ing power diodes are used to protect against reverse current flow in the event that one of the power supplies falls below the common bus voltage or develops a catastrophic failure. However, using a discrete OR-ing diode solution has some significant drawbacks. The primary downside is the increased power dissipation loss in the OR-ing diodes as system power requirements increase. At the lowest voltages where the ISL6146 is designed for use, the voltage distribution losses across an OR-ing diode can be a significant percentage, in some cases approaching 70%. Another disadvantage when using an OR-ing diode is failure to detect a shorted or opened current path, which jeopardizes system power availability and reliability. An open diode may reduce the system to a single point of failure while a shorted diode eliminates the system's power protection.

Using an active OR-ing FET controller, such as the ISL6146, helps with these potential issues. The use of a low on-resistance FET as the OR-ing component allows for a more efficient system design as the voltage across the FET is much lower than that across a forward biased diode. Additionally, the ISL6146 has a dedicated fault (FAULT) output pin that indicates when there is a conditional or FET fault short providing the diagnostic capability that a diode is unable to

The ISL6146 is designed to OR together voltages as low as 1V when supplied with a separate bias supply of 3V or greater. Otherwise, the ISL6146 is designed to be biased from and OR voltages across the 3V to 20V nominal supply range.

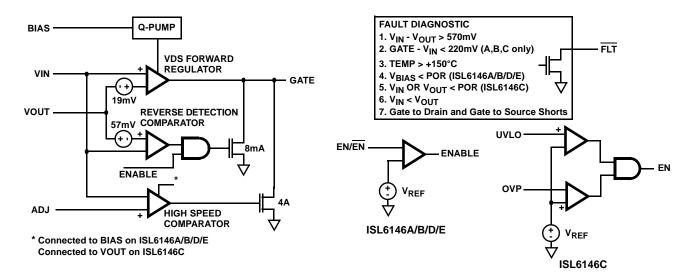

In a single FET configuration as voltage is first applied to a VIN pin, the FET body diode conducts providing all the ISL6146s connected on a common bus circuit, bias via the VOUT pins. As individual power supply voltages ramp up in excess of the rising POR threshold, the ISL6146's internal charge pump activates to provide a floating gate drive voltage for the external N-channel OR-ing MOSFET, thus turning the FETs on once  $V_{IN} > V_{OUT}$ . The ISL6146 continuously monitors the drain and source of the OR-ing FET and provides a reverse voltage (N-channel MOSFET VOLIT - VIN) detection threshold (VR) that, when exceeded, indicates a reverse current condition. Once this threshold is exceeded, the ISL6146 turns off the OR-ing FET by pulling down the GATE pin to GND. The ISL6146 also provides high speed V<sub>OUT</sub> > V<sub>IN</sub> transient protection as in the case of a catastrophic VIN failure. The ISL6146 additionally provides for adjustment of the VIN - VOLIT reverse voltage Vth(VR Vth) via the ADJ pin of the ISL6146 with an external resistor to GND. This allows adjusting the V<sub>IN</sub> - V<sub>OUT</sub> voltage threshold level to compensate for normal system voltage fluctuations, thus eliminating unnecessary reaction by the ISL6146.

The total  $V_{\text{IN}}$  -  $V_{\text{OUT}}$  VR Vth is the sum of both the internal offset and the external programmed VR Vth.

In the event of a  $V_{OUT} > V_{IN}$  condition, the ISL6146 responds either with a high or low current pull-down on the GATE pin depending on whether the High Speed comparator (HSCOMP) has been activated or not. The HSCOMP determines if the VR occurred within 1µs, by continuously monitoring the FET VDS and if so, the high pull-down current is used to turn off the OR-ing FET. In the event of a falling VIN transition in <1µs, (i.e., a catastrophic failure of the power source) the HSCOMP protects the common bus from the individual faulted power supply short by turning off the shorted supply's OR-ing MOSFET in less than 300ns, ensuring the integrity of the common bus voltage from reverse current to the damaged supply.

Once the correct  $V_{IN} > V_{OUT}$  relationship is established again, the ISL6146 again turns on the FET.

The FAULT pin is an open drain, active low output indicating that a fault or specific condition has occurred, these include:

- GATE is OFF (GATE < V<sub>IN</sub>+0.2V). Lack of conduction, not a fault, just not on. ISL6146D and ISL6146E do not respond to this condition

- Faults resulting in V<sub>IN</sub> V<sub>OUT</sub> > 0.57V when ON

- · An open FET resulting in body diode conduction

- · Excessive current through FET

- · FET Faults monitored and reported include

- G-D, gate unable to drive to Q-pump voltage

- G-S, gate unable to drive to Q-pump voltage

- D-S shorts, when GATE is OFF VDS < 2V

- V<sub>IN</sub> < POR

- Missing V<sub>IN</sub>

- VIN shorted to GND

On the ISL6146C version, a conditional fault is also signalled if the  $V_{\text{IN}}$  is not within the programmed UVLO and OVP levels.

The ISL6146 has an on-chip over-temperature fault threshold of ~+140°C with a 20°C hysteresis. Although the ISL6146 itself produces little heat, it senses the environment in which it is, likely including a close by FET.

The ISL6146A/D and ISL6146B/E are functional variants with an enabling input of either polarity. This feature is used when the need to interrupt the current path via signaling is necessary. This is accomplished by implementing two FETs in series so that there is a body diode positioned to block current in either direction. This functionality is considered an additional enhancement to the OR-ing diode it replaces.

The ISL6146C employs the use of a programmable Undervoltage Lock Out (UVLO) and a programmable Overvoltage Protection (OVP) input. This allows the GATE to only turn-on when the monitored voltage is between the programmed lower and upper levels. This application would use the back-to-back FET configuration. In the event that the current path does not need to be interrupted then the EN, UVLO and OVP inputs can all be overridden.

The ISL6146D and ISL6146E are variants of the ISL6146A and ISL6146B respectively, the difference being the former do not respond to a nonconduction condition (when enabled and VIN>VOUT, the GATE is not on) unlike the latter that do signal a fault.

## **Applications Information**

#### **Power-Up Considerations**

#### BIAS AND VIN CONSTRAINTS

Upon power-up when the  $V_{\mbox{IN}}$  supply is separate from the BIAS supply, the BIAS voltage must be greater or equal to the  $V_{\mbox{IN}}$  voltage at all times.

When using a single supply for both the ISL6146 bias and the OR-ing supply, the  $V_{\text{IN}}$  and BIAS pins can be configured with a low value resistor between the two pins to provide some isolation and decoupling to support the chip bias even as the OR'd supply experiences voltage droops and surges. Although not necessary to do so, it is a best design practice for particularly noisy environments.

#### **FET TO IC LAYOUT RECOMMENDATIONS**

Connections from the FET(s) to the ISL6146 VIN and VOUT pins must be Kelvin in nature and as close to the FET drain and source PCB pads as possible to eliminate any trace resistance errors that can occur with high currents. This connection placement is most critical to providing the most accurate voltage sensing particularly when the back-to-back FET configuration is used. Likewise, connections from OVP, UVLO and ADJ are also critical to optimize accuracy.

# ADJUSTING THE HS COMPARATOR REVERSE VOLTAGE THRESHOLD

The ISL6146 allows adjustment of the HS Comparator reverse voltage detection threshold (VR Vth), the difference in  $V_{OUT}$  -  $V_{IN}$ .

There are two valid ADJ pin configurations:

- ADJ connected to VOUT: This makes the HS comparator threshold equal to the intrinsic error in the HS comparator input. This is the default condition and the most likely used configuration.

- A single resistor is connected from ADJ pin to ground:

Making the HS comparator threshold = V<sub>OUT</sub> 4k/R<sub>ADJ</sub>.

So, for a 100k $\Omega$  R<sub>EXT</sub>, HS Comparator threshold = 40mV below VOUT and for a 5k $\Omega$  R<sub>EXT</sub> HS comparator threshold = ~ 800mV below VOUT.

The recommended resistor range is  $5k\Omega$  to  $100k\Omega$  for this voltage adjustment.

At power-up, the HS comparator threshold is default set to the internal device error first, and then released to the user programmed threshold after the related circuits are ready. It takes ~20 $\mu$ s for the circuit to switch from the default setting to the user programmed threshold after a POR startup.

The current out of the ADJ pin with a resistor to GND is equal to  $0.4V/R_{\text{EXT}}$ .

#### **BACK-TO-BACK FET CONFIGURATION**

When using the back-to-back FET configuration, the FET choice must be such that the voltage across both FETs at full current loading be less than the minimum forward voltage fault threshold of 400mV to avoid unintended fault notification.

In this configuration, it may be tempting to use the enable inputs to force a path by switching between the two as opposed to having both paths on, and having the higher voltage source provide current. The problem with that is the timing of the FETs on and off, so that excessive V<sub>OUT</sub> voltage droop is not introduced if the turn-off happens faster, or before the (or a slower) turn-on momentarily leaves the load with an inadequate power connection.

#### **Typical Applications Circuits**

There are four basic configurations that the ISL6146 can be used in:

- 1. For voltages >3V where the BIAS and V<sub>IN</sub> are common

- 2. For a very low OR-ing voltage, <3V operation, BIAS >3V

- 3. For a voltage window compliant operation and,

- 4. For a signaled operation where the current path is controlled by an input signal or minimum voltage condition.

Each of these configurations can be tailored for the High Speed Comparator (HS COMP) reverse threshold via the ADJ input being connected either to VOUT or to GND via a resistor as previously explained. Additionally, the voltage window is adjustable for both a minimum and maximum operating voltage via the UVLO and OVP inputs and a resistor divider also explained earlier. Also, soft-start and turn-on and turn-off characteristics can be tailored to suit.

The three evaluation platforms provided demonstrate the four basic configurations and provide for the additional tailoring of the various performance characteristics.

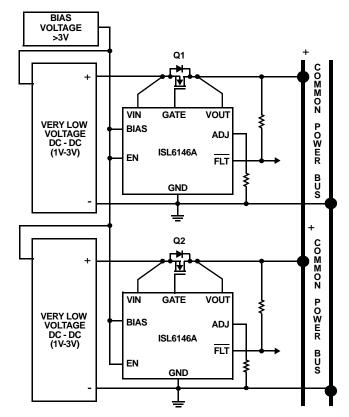

FIGURE 47. LOW VOLTAGE APPLICATION DIAGRAM

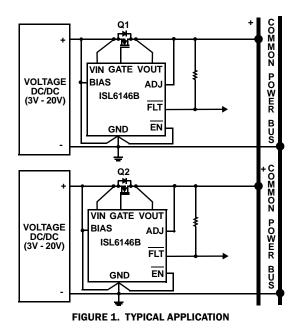

The Figure 1 circuit shown on page 1 is the basic circuit used for OR-ing voltages >3V to 20V.

The ISL6146A application shown in Figure 47 is the configuration for OR-ing very low voltages of 1V to 3V. Additionally, this application shows the utilization of the ADJ input with a single resistor tied to GND. This provides the user a programmable level of  $V_{OUT} > V_{IN}$  before the High Speed (HS) Comparator is activated and the GATE output is pulled down to allow for normal voltage fluctuations in the system.

Notice that in both of these circuits, the EN or  $\overline{\text{EN}}$  inputs are defaulted to enabled and have no current path on/off control. Failure to do so correctly will result in only body diode conduction and a resulting fault indication.

The  $V_{\text{IN}}$  and  $V_{\text{OUT}}$  to FET and GND to ADJ connections are drawn to emphasize the Kelvin connection necessary to correctly monitor the voltage across the FET, and for the VR Vth monitor to eliminate any stray resistance effects.

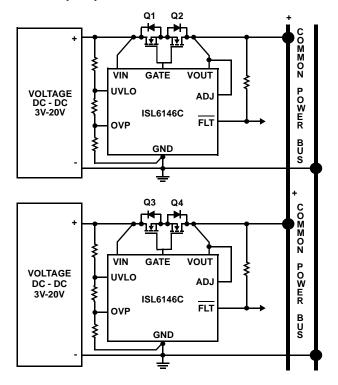

FIGURE 48. TYPICAL ISL6146C APPLICATION DIAGRAM

The ISL6146C application shown in Figure 48 is limited to the 3V to 20V  $V_{IN}$  range and must implement the back-to-back FET configuration to utilize the UVLO and OVP inputs and capabilities. As the  $V_{IN}$  voltage rises above the minimum programmed voltage, the related OR-ing FETs will turn on and stay on until either the minimum voltage requirement is no longer met or the  $V_{IN}$  voltage exceeds its programmed maximum. The minimum and maximum programmed voltage levels are done with the resistor divider on the UVLO and OVP pins. These levels should be programmed to take into account conduction path losses to the load in addition to the IC operational constraints.

When using the back-to-back FET configuration, the user must chose FETs to ensure (2r $_{DS(ON)}$  + PCB IR) I $_{LOAD}$  < 0.5V to avoid tripping the V $_{IN}$  - V $_{OUT}$  > 0.5V when ON fault.

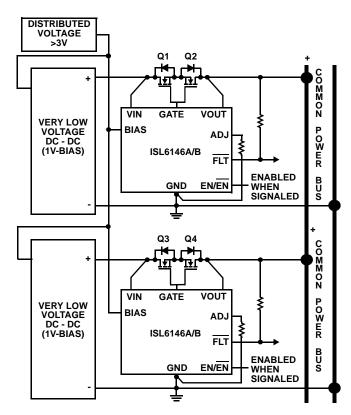

FIGURE 49. CONTROLLED ON/OFF APPLICATION DIAGRAM

The application diagram in Figure 49 shows the ISL6146A or ISL6146B utilizing the EN or  $\overline{\text{EN}}$  pin as a signalled input to open or close the conduction path from power supply to load. This feature can be implemented on OR-ing 1V to 20V but is shown for OR-ing <3V.

The enable input signaling can be simultaneous across the N+1 number of ISL6146s used.

Although not needed for thermal relief, connect the DFN EPAD to GND.

#### **SWITCH-OVER CIRCUITS**

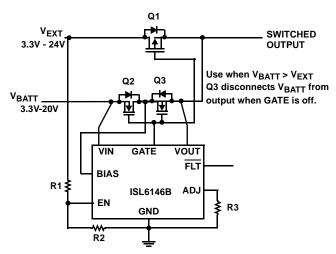

Switch over applications are different than OR-ing applications in that, the former are looking for the presence of or a condition of a preferred supply in order to switch to it. Whereas true OR-ing consists of a redundant N+1 configuration with no preferred source.

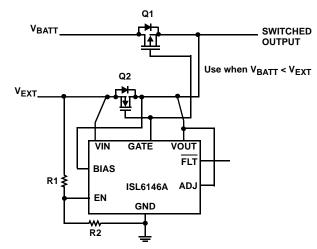

The following 2 circuits are simple single ISL6146 switchover circuits optimized for situations particular to the  $V_{BATT}$  and  $V_{EXT}$  voltages relative to each other. Figure 50 shows an ISL6146B switchover circuit where  $V_{EXT}$ , when present, is the preferred source and  $V_{BATT}$  could be lesser or greater than  $V_{EXT}$ . This circuit senses the presence of the preferred voltage supply to a programmable threshold level that when exceeded,  $V_{EXT}$  is passed to the output as  $V_{BATT}$  is disconnected from the output.

R1 & R2 program the V<sub>EXT</sub> level that must be preset for the preferred voltage to be passed to the output.

Q3 is necessary if  $V_{BATT}$  can ever exceed  $V_{EXT}$  to prevent current from flowing into  $V_{EXT}$  when present. The body diode of Q3

prevents that when Q1 is on regardless of the  $V_{BATT}$  voltage. The ISL6146 bias is pulled from the common drain node to ensure an always adequate bias from either source when the other is absent

FIGURE 50. ISL6146B EXTERNAL SWITCHOVER SCHEMATIC

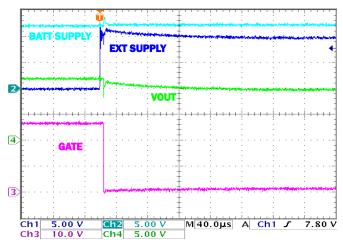

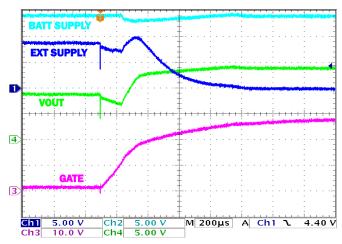

Figure 51 shows operational scope shots of the above circuit.

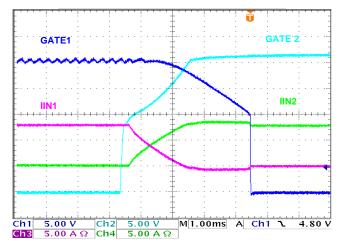

FIGURE 51. EXTERNAL SUPPLY < BATT SUPPLY CONNECTED

FIGURE 52. EXTERNAL SUPPLY < BATT SUPPLY DISCONNECTED

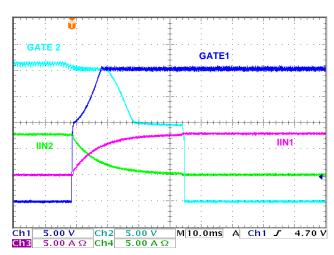

All of the scope shots were taken with a 5A load and 100  $\mu F$  of bulk load capacitance.

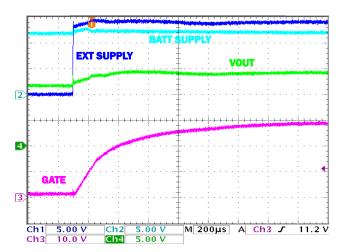

Figure 52 is a ISL6146A switchover circuit to use where the preferred  $V_{EXT}$  source is always greater than the  $V_{BATT}$ . Because this is so, there is no need for a 3rd FET for blocking as in Figure 50. Additionally, the preferred  $V_{EXT}$  source when present or at a programmed minimum threshold voltage via R1 and R2 divider will turn on Q2/turn-off Q1 but when absent or not minimally adequate, will do the opposite. In this circuit, with the ISL6146A not connected to the battery, and thus no constant  $I_{VIN}$  load on it, which allows for longer battery life.

Bias voltage is pulled from the common output to ensure an always adequate IC bias from either source.

FIGURE 53. ISL6146A EXTERNAL SWITCHOVER SCHEMATIC

FIGURE 54. EXTERNAL SUPPLY > BATT SUPPLY CONNECTED

FIGURE 55. EXTERNAL SUPPLY > BATT SUPPLY DISCONNECTED

### **ISL6146 Evaluation Platforms**

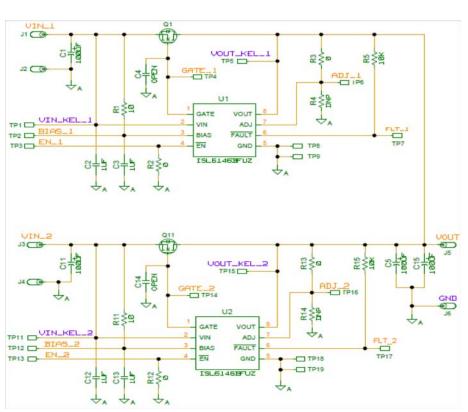

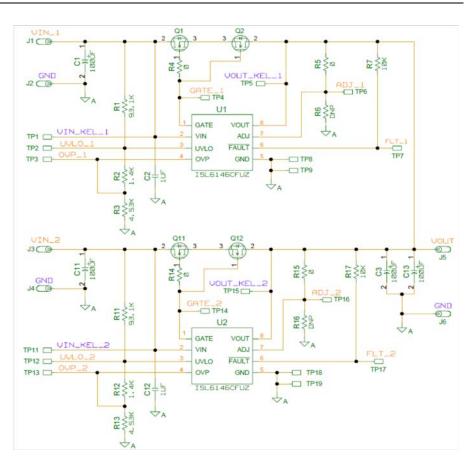

#### **Description and Use of the Evaluation Boards**

The three ISL6146 evaluation boards are used to demonstrate the four application configurations discussed earlier. All the boards have ADJ shorted to VOUT with the PCB layout having the component footprints to insert a resistor of choice between ADJ and GND to adjust the HS COMP Vth. Likewise, the VIN is connected to BIAS but these can be separated to provide an adequate BIAS voltage when OR-ing <3V supplies or if providing a separate from VIN voltage to BIAS.

The **ISL6146AEVAL1Z** is configured to have a 8.5V minimum turn-on threshold with a 1.2V hysteresis.

The **ISL6146BEVAL1Z** is configured as a minimally featured maximum performance OR-ing FET controller for 3V to 20V.

The **ISL6146CEVAL1Z** is configured to operate with a 10.8V lower turn on threshold and 14.9V upper turn-off threshold.

All three boards are equipped with 50A capable FETs for high current evaluations and with a minimum of  $V_{IN}$  and  $V_{OUT}$  bulk capacitance likely to be found in any power system design.

After determining the BIAS source along with  $V_{\text{IN}}$  voltage criteria and configuring the evaluation board if necessary, for the application to be evaluated the board is ready for power.

Apply the BIAS voltage first (via the test points labeled BIAS), if separate from VIN, then the  $V_{\text{IN}}$  voltage. Monitor the provided test points for device performance with current loads up to 50A.

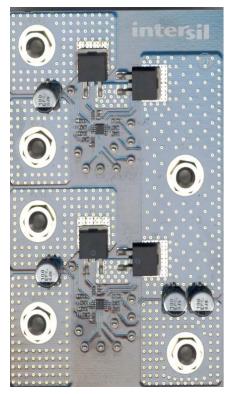

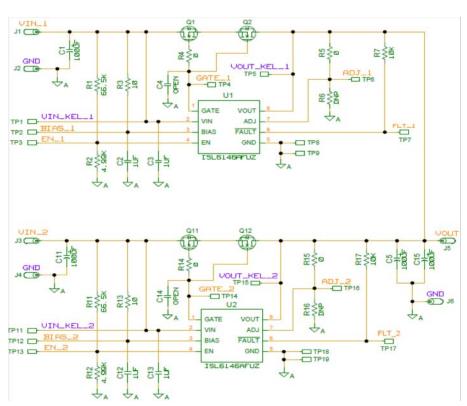

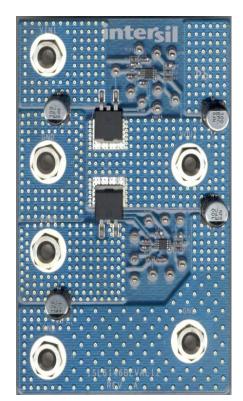

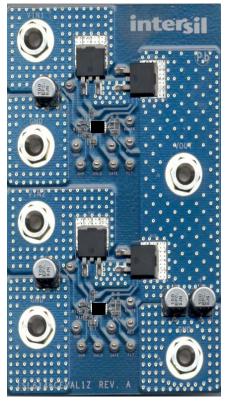

Figures 56 through 61 illustrate the three ISL6146 evaluation boards for the three typical applications in photograph and schematic form.

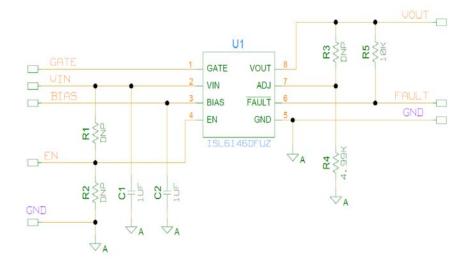

There are also 2 mini development boards named ISL6146DEVAL1 and ISL6146EEVAL1. These boards are provided as a matching pair of either the ISL6146D or ISL6146E part type directly from the website or with either the ISL6146A or ISL6146B installed from the factory (contact support if desired). The small size (1" x 0.5") is suitable for adding into an existing circuit using another OR-ing FET controller. These small and simple boards have only the necessary components for its implementation utilizing the already present MOSFET(s) in the circuit it is being added to.

The mini evaluation circuit is designed to give the user the flexibility in either defaulting or signaling the enable ON or to use a VIN voltage threshold to turn-on the IC function. Provided are access to the IC VIN, GATE and VOUT pins for best practices connections to the MOSFET(s) along with adjustable HS Vth via the ADJ pin and the  $\overline{\text{FAULT}}$  output.

The mini evaluation circuit is documented in Figures 62 & 63 and Table 2.

FIGURE 56. ISL6146AEVAL1Z

FIGURE 57. ISL6146AEVAL1Z SCHEMATIC

FIGURE 58. ISL6146BEVAL1Z

FIGURE 59. ISL6146BEVAL1Z SCHEMATIC

FIGURE 60. ISL6146CEVAL1Z

FIGURE 61. ISL6146CEVAL1Z SCHEMATIC

Dimensions are 1" x 0.5" (25.4mm x 12.7mm)

FIGURE 63. ISL6146EDEV1Z SCHEMATIC (Mini-eval)

#### TABLE 2. ISL6146xEVALZ BOM

| REFERENCE DESIGNATOR | VALUE         | DESCRIPTION                    | MANUFACTURER | PART NUMBER |

|----------------------|---------------|--------------------------------|--------------|-------------|

| ISL6146AEVAL1Z       |               | 1                              |              | 1           |

| U1, U2               |               | ISL6146A OR-ing FET Controller | Intersil     | ISL6146AFUZ |

| Q1, Q2, Q11, Q12     |               | 30V, 50A FET                   | Various      |             |

| R1, 11               | 66.5kΩ        | RES, SMD, 0603, 1%             | Generic      |             |

| R2, R12, R6, R16     | 4.99kΩ        | RES, SMD, 0603, 1%             | Generic      |             |

| R3, R13              | 10Ω           | RES, SMD, 0603, 1%             | Generic      |             |

| R4, R14              | 0Ω            | RES, SMD, 0603, 1%             | Generic      |             |

| R5, R15              | DNP           | RES, SMD, 0603, 1%             | Generic      |             |

| R7, R17              | <b>10</b> kΩ  | RES, SMD, 0603, 1%             | Generic      |             |

| C1, C11, C5 C15      | 100µF         | Alum. Elect SMD Cap            | Generic      |             |

| C2, C3, C12 C13      | 1µF           | CAP, SMD, 0603, 50V, 10%       | Generic      |             |

| C4, C14              | DNP           | CAP, SMD, 0603, 50V, 10%       | Generic      |             |

| TPx                  |               | Test Point                     | Generic      |             |

| Jx                   |               | Banana Jack                    | Generic      |             |

| ISL6146BEVAL1Z       |               |                                |              |             |

| U1, U2               |               | ISL6146B OR-ing FET Controller | Intersil     | ISL6146BFUZ |

| Q1, Q11              |               | 30V, 50A FET                   | Various      |             |

| R4, R14              | 4.99kΩ        | RES, SMD, 0603, 1%             | Generic      |             |

| R1, R10              | 10Ω           | RES, SMD, 0603, 1%             | Generic      |             |

| R2, R12              | Ω0            | RES, SMD, 0603, 1%             | Generic      |             |

| R3, R13              | DNP           | RES, SMD, 0603, 1%             | Generic      |             |

| R5, R15              | <b>10</b> kΩ  | RES, SMD, 0603, 1%             | Generic      |             |

| C1, C11, C5 C15      | 100µF         | Alum. Elect SMD Cap            | Generic      |             |

| C2, C3, C12 C13      | 1µF           | CAP, SMD, 0603, 50V, 10%       | Generic      |             |

| C4, C14              | DNP           | CAP, SMD, 0603, 50V, 10%       | Generic      |             |

| ТРх                  |               | Test Point                     | Generic      |             |

| Jx                   |               | Banana Jack                    | Generic      |             |

| SL6146CEVAL1Z        |               |                                |              | <u>'</u>    |

| U1, U2               |               | ISL6146C OR-ing FET Controller | Intersil     | ISL6146CFUZ |

| Q1, Q2, Q11, Q12     |               | 30V, 50A FET                   | Various      |             |

| R1, 11               | 93.1kΩ        | RES, SMD, 0603, 1%             | Generic      |             |

| R2, R12              | <b>1.4</b> kΩ | RES, SMD, 0603, 1%             | Generic      |             |

| R3, R13              | 4.53kΩ        | RES, SMD, 0603, 1%             | Generic      |             |

| R4, R14              | 0Ω            | RES, SMD, 0603, 1%             | Generic      |             |

| R5, R15              | DNP           | RES, SMD, 0603, 1%             | Generic      |             |

| R6, R16              | 4.99kΩ        | RES, SMD, 0603, 1%             | Generic      |             |

| R7, R17              | <b>10</b> kΩ  | RES, SMD, 0603, 1%             | Generic      |             |

| C1, C11, C3 C13      | 100µF         | Alum. Elect SMD Cap            | Generic      |             |

| C2, C12              | 1µF           | CAP, SMD, 0603, 50V, 10%       | Generic      |             |

| TPx                  |               | Test Point                     | Generic      |             |

| Jx                   |               | Banana Jack                    | Generic      |             |

#### TABLE 2. ISL6146xEVALZ BOM (Continued)

| REFERENCE DESIGNATOR | VALUE        | DESCRIPTION                    | MANUFACTURER                                 | PART NUMBER |

|----------------------|--------------|--------------------------------|----------------------------------------------|-------------|

| ISL6146DEVAL1Z       | *            |                                | <u>.</u>                                     |             |

| U1                   |              | ISL6146D OR-ing FET Controller | Intersil                                     | ISL6146DFUZ |

| R1, R2, R3           | DNP          | RES, SMD, 0603, 1%             | Generic                                      |             |

| R4                   | 4.99kΩ       | RES, SMD, 0603, 1%             | Generic                                      |             |

| R5                   | <b>10</b> kΩ | RES, SMD, 0603, 1%             | Generic                                      |             |

| C1, C2               | 1µF          | CAP, SMD, 0603, 50V, 10%       | Generic                                      |             |

| ISL6146EEVAL1Z       |              |                                | <u>,                                    </u> |             |

| U1                   |              | ISL6146E OR-ing FET Controller | Intersil                                     | ISL6146EFUZ |

| R1, R2, R3           | DNP          | RES, SMD, 0603, 1%             | Generic                                      |             |

| R4                   | 4.99kΩ       | RES, SMD, 0603, 1%             | Generic                                      |             |

| R5                   | <b>10</b> kΩ | RES, SMD, 0603, 1%             | Generic                                      |             |

| C1, C2               | 1µF          | CAP, SMD, 0603, 50V, 10%       | Generic                                      |             |

## **Revision History**

The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please go to web to make sure you have the latest revision.

| DATE               | REVISION | CHANGE                                                                                                                                                                                                                                                                                                                                            |

|--------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| April 3, 2013      | FN7667.4 | Added ISL6146DEVAL1Z and ISL6146EEVAL1Z related information. Figures 62 and 63. Corrected labels in Figure 61.                                                                                                                                                                                                                                    |

| September 27, 2012 | FN7667.3 | Added tape and reel parts to Ordering Information table for ISL6146A/B/C/D/E products.  Thermal Information - removed Pb-Free Reflow link                                                                                                                                                                                                         |

| June 18, 2012      | FN7667.2 | Added ISL6146D and ISL6146E. References to these products added throughout the datasheet. Added Figures 45 & 46 to illustrate the fault differences between ISL6146A/B and ISL6146D/E. Moved Figure 50 and revised the related text on page 20 before the evaluation board section. Added Figures 51 - 55 and related text on page 20 to page 21. |

| February 27, 2012  | FN7667.1 | Removed note "MSOP packaged parts to be released soon" from "Ordering Information" on page 3. Added Figures 42 & 43 on page 15.                                                                                                                                                                                                                   |

| December 16, 2011  | FN7667.0 | Initial Release                                                                                                                                                                                                                                                                                                                                   |

#### **About Intersil**

Intersil Corporation is a leader in the design and manufacture of high-performance analog, mixed-signal and power management semiconductors. The company's products address some of the largest markets within the industrial and infrastructure, personal computing and high-end consumer markets. For more information about Intersil, visit our website at <a href="https://www.intersil.com">www.intersil.com</a>.

For the most updated datasheet, application notes, related documentation and related parts, please see the respective product information page found at <a href="https://www.intersil.com/en/support/ask-an-expert.html">www.intersil.com/en/support/ask-an-expert.html</a>. Reliability reports are also available from our website at <a href="https://www.intersil.com/en/support/qualandreliability.html#reliability">https://www.intersil.com/en/support/qualandreliability.html#reliability</a>

For additional products, see <a href="www.intersil.com/product-tree">www.intersil.com/product-tree</a>

Intersil products are manufactured, assembled and tested utilizing ISO9000 quality systems as noted in the quality certifications found at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see <a href="https://www.intersil.com">www.intersil.com</a>

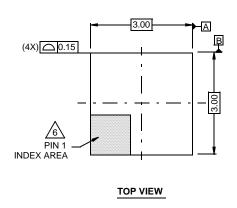

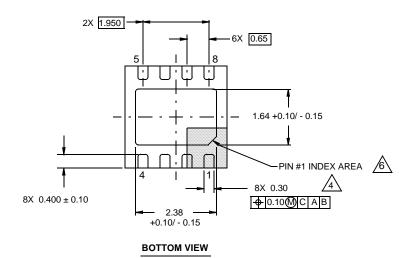

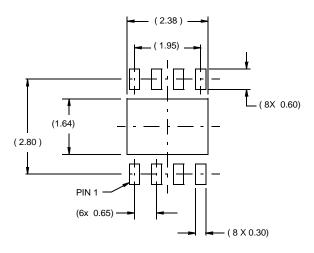

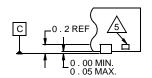

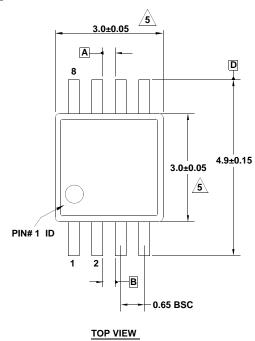

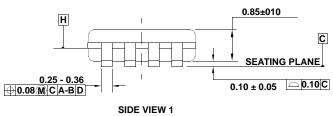

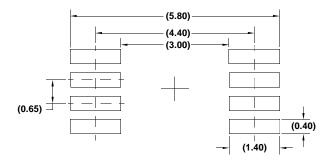

# Package Outline Drawing L8.3x3J

8 LEAD DUAL FLAT NO-LEAD PLASTIC PACKAGE Rev 0 9/09

TYPICAL RECOMMENDED LAND PATTERN

DETAIL "X"

#### NOTES:

- Dimensions are in millimeters.

Dimensions in ( ) for Reference Only.

- 2. Dimensioning and tolerancing conform to AMSE Y14.5m-1994.

- 3. Unless otherwise specified, tolerance : Decimal  $\pm 0.05$

- 4. Dimension applies to the metallized terminal and is measured between 0.15mm and 0.30mm from the terminal tip.

- 5. Tiebar shown (if present) is a non-functional feature.

- The configuration of the pin #1 identifier is optional, but must be located within the zone indicated. The pin #1 identifier may be either a mold or mark feature.

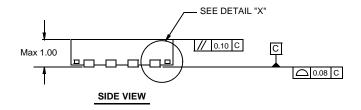

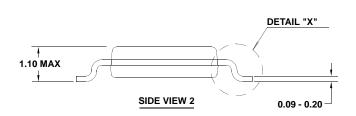

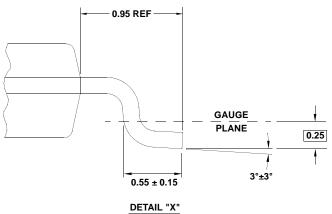

# **Package Outline Drawing**

#### M8.118

8 LEAD MINI SMALL OUTLINE PLASTIC PACKAGE Rev 4, 7/11

TYPICAL RECOMMENDED LAND PATTERN

#### NOTES:

- 1. Dimensions are in millimeters.

- Dimensioning and tolerancing conform to JEDEC MO-187-AA and AMSEY14.5m-1994.

- 3. Plastic or metal protrusions of 0.15mm max per side are not included

- 4. Plastic interlead protrusions of 0.15mm max per side are not included.

- 5. Dimensions are measured at Datum Plane "H".

- 6. Dimensions in ( ) are for reference only.