## AJAV-5501

# 3G Band I Power Amplifier

# **Data Sheet**

## **Description**

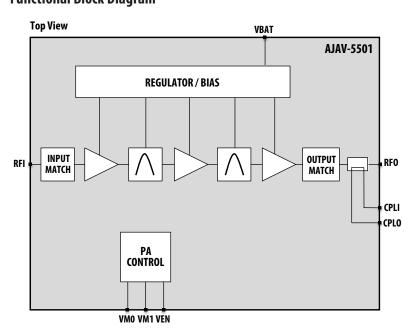

The AJAV-5501 is a complete, high-performance power amplifier for W-CDMA and HSPA wireless communications. Based on a unique, patented architecture, the AJAV-5501 integrates circuitry for TX filtering, RF coupling, power regulation, input and output matching and power control. The PA is powered by a single connection to the battery and is implemented in a standard CMOS process.

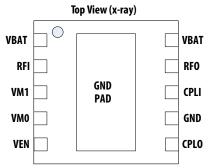

## **Pin Assignments**

US Patent # 7,728,661; 7,768,350; 7,872,528; 8,022,766 Other patents pending

# **Functional Block Diagram**

### **Features**

- High-performance 3G power amplifier

- UMTS Band I (1920 1980 MHz)

- W-CDMA, HSPA, and HSPA+ Compliant

- Integrated TX filtering

- Delivers best noise in the industry

- Integrated directional coupler

- Integrated regulators and PA bias

- Single direct connection to the battery

- No external switches or isolation inductors

- High linear efficiency

- Low average current

- High capacity CMOS process

- Small 3x3 mm package

### **Applications**

- Smartphones, data cards and 3G modules

- Tablets, netbooks and network PCs

- E-books and wireless electronic readers

## **Electrical Characteristics**

Table 1. Absolute Minimum and Maximum Ratings [1]

| Parameter                         | Symbol           | Condition                             | Min  | Тур | Max | Unit |

|-----------------------------------|------------------|---------------------------------------|------|-----|-----|------|

| Supply Voltage <sup>[2]</sup>     | $V_{BATT}$       |                                       | -0.3 | -   | 4.5 | V    |

| Control Voltage [3]               | $V_{CTRL}$       | V <sub>CTRL</sub> < V <sub>BATT</sub> | -0.3 | -   | 4.5 | V    |

| RF Input Power [4]                |                  |                                       | -    | -   | +10 | dBm  |

| Electrostatic Discharge (ESD) [5] |                  | Human Body Model (HBM)                | -    | -   | 3.0 | kV   |

| Storage Temperature               | T <sub>STG</sub> |                                       | -55  | -   | 125 | °C   |

#### Notes:

- 1. Permanent device damage may occur if the ratings above are exceeded. Functional operation is not guaranteed under these conditions and should be restricted to the recommended operating conditions in Table 2. Exposure to absolute ratings for extended periods may affect device reliability.

- 2. Supply voltage is applied to VBAT pin.

- 3. Control voltages are applied to VEN, VM0, VM1 pins.

- 4. RF input is applied to RFI, CPLI pins.

- 5. For all pins.

## Table 2. Operating Conditions [1]

| Parameter                  | Symbol          | Condition           | Min | Тур | Max        | Unit |

|----------------------------|-----------------|---------------------|-----|-----|------------|------|

| Supply Voltage [2]         | $V_{BATT}$      |                     | 3.2 | 3.8 | 4.2        | V    |

| Control Voltage – High [3] | V <sub>IH</sub> | $V_{IH} < V_{BATT}$ | 1.3 | 1.8 | $V_{BATT}$ | V    |

| Control Voltage – Low [3]  | V <sub>IL</sub> |                     | 0.0 | -   | 0.5        | V    |

| Ambient Temperature        | T <sub>A</sub>  |                     | -30 | 25  | 90         | °C   |

#### Notes

- 1. To ensure proper operation, the VEN pin should be asserted from V<sub>IL</sub> to V<sub>IH</sub> at least 2 µs after power is applied to the VBAT pin.

- 2. Device to remain functional down to  $V_{BATT} = 3.0 \text{ V}$  with degraded performance. At  $V_{BATT} < 3.4 \text{ V}$ , output power is derated by 0.5 dB.

- 3. Logic states for VEN, VM0, VM1 pins.

## Table 3. Mode Control Logic [1]

| Mode                 | Output Power Range <sup>[2]</sup>        | VEN  | VM0  | VM1  |  |

|----------------------|------------------------------------------|------|------|------|--|

| High Power Mode (HP) | $16.5 \text{ dBm} < P_{OUT} \le P_{MAX}$ | High | Low  | Low  |  |

| Mid Power Mode (MP)  | 6.0 dBm < P <sub>OUT</sub> ≤ 16.5 dBm    | High | High | Low  |  |

| Low Power Mode (LP)  | P <sub>OUT</sub> ≤ 6.0 dBm               | High | High | High |  |

| Powerdown            |                                          | Low  | Х    | X    |  |

### Notes:

- 1. The VM0 and VM1 pins are controlled externally to achieve maximum PA efficiency. High and low logic states are specified in Table 2.

- 2. Maximum linear output power, P<sub>MAX</sub>, is defined in Table 4.

Table 4. Electrical Specifications [1]

| Parameter                            | Symbol                            | Condition                          | Min   | Тур   | Max   | Unit   |

|--------------------------------------|-----------------------------------|------------------------------------|-------|-------|-------|--------|

| Frequency                            | F <sub>RF</sub>                   |                                    | 1920  | -     | 1980  | MHz    |

| Maximum Linear Output Power [2]      | P <sub>MAX</sub>                  | HP mode                            | +26.0 | +26.5 | -     | dBm    |

|                                      |                                   | MP mode                            | +16.0 | +16.5 | -     | dBm    |

|                                      |                                   | LP mode                            | +5.5  | +6.0  | -     | dBm    |

| Gain <sup>[2]</sup>                  | G                                 | HP mode                            | 27.0  | 28.5  | -     | dB     |

|                                      |                                   | MP mode                            | 17.0  | 18.5  | -     | dB     |

|                                      |                                   | LP mode                            | 8.0   | 10.0  | -     | dB     |

| RX Band Gain <sup>[2,3]</sup>        | G <sub>RX</sub>                   | RX Band, 190 MHz offset            | -     | -     | -15   | dBc    |

|                                      |                                   | GPS Band, 1524-1577 MHz            | -     | -     | -35   | dBc    |

|                                      |                                   | ISM Band, 2400-2484 MHz            | -     | -     | -34   | dBc    |

| Adjacent Channel Leakage Ratio [2,4] | ACLR1                             | ± 5 MHz offset                     | -     | -42   | -38   | dBc    |

|                                      | ACLR2                             | ± 10 MHz offset                    | -     | -53   | -48   | dBc    |

| Noise [4,5]                          | N                                 | RX Band, 190 MHz offset            | -     | -148  | -     | dBm/Hz |

|                                      |                                   | GPS Band, 1524-1577 MHz            | -     | -154  | -     | dBm/Hz |

|                                      |                                   | ISM Band, 2400-2484 MHz            | -     | -156  | -     | dBm/Hz |

| Error Vector Magnitude [2,4,5]       | EVM                               | $P_{OUT} \le P_{MAX}$              | -     | 1.5   | 3.35  | %      |

| Power Added Efficiency [2,5,6]       | PAE                               | HP mode                            | -     | 38    | -     | %      |

|                                      |                                   | MP mode                            | -     | 23    | -     | %      |

| Quiescent Idle Current               | I <sub>CQ</sub>                   | LP mode                            | -     | 8     | 10    | mA     |

| Average Current [2,5,7]              | I <sub>AVG</sub>                  | Total current from all pins        | -     | 26    | -     | mA     |

| Powerdown Current [4,8]              | I <sub>PD</sub>                   | $VEN = V_{IL}$                     | -     | 5     | 10    | μΑ     |

| Logic Current [4,9]                  | I <sub>CTRL</sub>                 |                                    | -     | 7     | 10    | μΑ     |

| Input Impedance [5]                  | Z <sub>IN</sub>                   |                                    | -     | 1.4:1 | 1.8:1 | VSWR   |

| Reverse Intermodulation [4,5,10]     |                                   | ± 5 MHz offset                     | -     | -     | -31   | dBc    |

|                                      |                                   | ± 10 MHz offset                    | -     | -     | -41   | dBc    |

| Harmonics [2,4,5]                    | 2F <sub>0</sub>                   | Second harmonic                    | -     | -     | -35   | dBc    |

|                                      | 3F <sub>0</sub> , 4F <sub>0</sub> | Third and fourth harmonic          | -     | -     | -35   | dBc    |

| Instantaneous Phase Change [4,5]     |                                   | Between power modes                | -     | 5     | 10    | degree |

| Coupling Factor [11]                 | s31                               |                                    | -     | -19.5 | -     | dB     |

| Daisy Chain Insertion Loss [5]       | s34                               | UMTS Band II                       | -     | -0.4  | -     | dB     |

|                                      |                                   | UMTS Band V, VIII                  | -     | -0.2  | -     | dB     |

| Daisy Chain Return Loss [5,11]       | s33, s44                          | UMTS Band II                       | -     | -18   | -     | dB     |

| ·                                    |                                   | UMTS Band V, VIII                  | -     | -27   | -     | dB     |

| Output Power Error [5,12]            |                                   | Load VSWR = 2.5:1                  | -1    | -     | +1    | dB     |

| Turn-on Time <sup>[13]</sup>         | T <sub>ON</sub>                   |                                    | -     | 9     | 12    | μS     |

| Turn-off Time [5,13]                 | T <sub>OFF</sub>                  |                                    | -     | 7     | 10    | <br>μs |

| Other Spurious [4,5]                 |                                   | Load VSWR ≤ 5:1                    | -     | -     | -70   | dBc    |

| Ruggedness <sup>[5]</sup>            |                                   | No permanent damage or degradation |       | _     | 10:1  | VSWR   |

### Notes:

- 1. Specifications at nominal operating conditions  $V_{IH} = 1.8 \text{ V}$ ,  $V_{EN} = 1.8 \text{ V}$ ,  $V_{BAT} = 3.8 \text{ V}$ ,  $V_{AT} = 25 \,^{\circ}\text{C}$ , RF ports at 50  $\Omega$ , guaranteed over the full range of operating frequency and guaranteed by production test unless indicated otherwise.

- 2. Specification is guaranteed using W-CDMA modulation RMC (12.2 kbps) in compliance with 3GPP Release 99.

- 3. RX band gain is specified relative to PA gain at 1880 MHz.

- 4. Specification is guaranteed over all power modes given in Table 3.

- 5. Specification is guaranteed by characterization.

- 6. Power added efficiency (PAE) includes total current consumption through all pins while PA is operating at maximum linear output power.

- 7. Calculated using three power modes (HP, MP, LP) with handset WCDMA transmitter power distribution in GSMA DG.09 specification assuming 3 dB of post-PA loss.

- 8. Total supply current measured when the PA is disabled.

- 9. Specification applies to each  $V_{\text{EN}}$ , VM0, and VM1 pin.

- 10. Interferer is CW at a relative power level of -40 dBc and offset from the W-CDMA modulated carrier.

- 11. Measured at CPLO pin.

- 12. Power variation measured at the RFO pin while power at CPLO pin is held constant.

- 13. Specified from the start of the PA enable transition to when the output power is within  $\pm 1$  dB of final value.

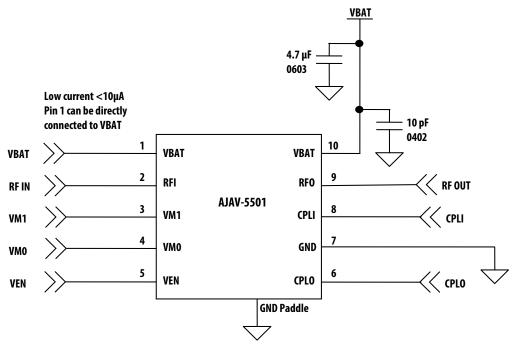

## **Application Information**

Figure 1. Typical Single-Band Application Circuit

The AJAV-5501 is the world's first 3G Band I power amplifier (PA) implemented in a standard CMOS process. The AJAV-5501 delivers low current and integrates TX filtering that produces the best noise in the industry. Only a single RF bypass capacitor is required, enabling a very low bill-of-materials (BOM). The AJAV-5501 is fully compliant with W-CDMA, HSPA, and HSPA+ standards through 3GPP Release 7 and supports power class 3 and 4.

Figure 1 shows the typical application circuit. The AJAV-5501 supports three power modes controlled by a standard CMOS interface enabling a direct connection to the baseband with no level shifters. The VEN, VM0 and VM1 power control pins are high impedance with logic levels defined in Table 2.

The AJAV-5501 may be powered by a single direct connection to the battery, or controlled with an external DC/DC converter. All power supply current flows through pin 10. Pin 1 is a low current input that can be directly connected to VBAT or any other high level signal. No external switches, isolation inductors, or bypass capacitors are required on Pin 1.

Standard RF practice should be followed for the PCB layout of the RF traces for pins 2, 6, 8, and 9. Multiple vias should be placed underneath the GND paddle to create a low resistance path to ground and to ensure good heat conduction. Refer to Application Note 5565, (AV02-4080EN) *AJAV-5xxx PCB Guidelines*, for additional information.

The AJAV-5501 features an integrated directional coupler that can be daisy chained through the CPLI and CPLO ports. For best performance, at least one port should see a 50  $\Omega$  path to GND. The CPLI port accepts an RF input or can be terminated. The CPLO port provides the coupled RF output that can be passed to the RF detector, terminated, or passed to the next PA in the daisy chain.

The AJAV-5501 includes integrated TX filtering that ensures excellent receiver sensitivity. As the RF signal passes through the PA, the unwanted out-of-band noise produced by the transceiver is filtered out. Furthermore, the thermal noise at the PA output is greatly reduced below the level of a conventional GaAs PA. The resulting signal at the output of the AJAV-5501 is spectrally very clean, ensuring the best receiver sensitivity and producing minimal interference to other radios in the system.

| Pin# | Name | Description       |  |

|------|------|-------------------|--|

| 1    | VBAT | DC Supply Voltage |  |

| 2    | RFI  | RF Input          |  |

| 3    | VM1  | Mode Control      |  |

| 4    | VM0  | Mode Control      |  |

| 5    | VEN  | PA Enable         |  |

| 6    | CPLO | Coupler Output    |  |

| 7    | GND  | Ground            |  |

| 8    | CPLI | Coupler Input     |  |

| 9    | RFO  | RF Output         |  |

| 10   | VBAT | DC Supply Voltage |  |

| epad | GND  | Ground            |  |

Figure 2. Pin Descriptions

## **TOP BRAND**

J5501 YWWXX RFAT

Pin 1 indicator: Laser dot Manufacturing part number: J5501 Trace code: YWWXX Y - Year

WW - Work week XX - Lot number

XX - Lot nur

Manufacturing information: RFAT

Figure 3. Package Marking

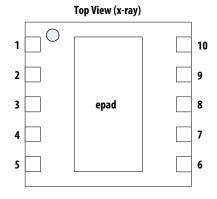

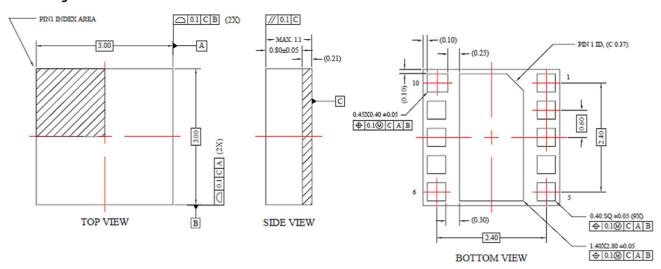

## **LGA Package Information**

## Notes

- 1. Controlling Dimension: Millimeters

- 2. Unless Specified TOL.: ± 0.076 [0.003]

- 3. Pads (including center) shown uniform size for reference only.

Actual pad size and location will vary within MIN. and MAX. dimensions according to specific laminate design

- 4. Unless specified dimensions are symmetrical about center lines shown

Figure 4. LGA Package Information

# **Ordering Guide**

| Part Number   | Description               | Package Type | Operating Temperature | Quantity | Container      |

|---------------|---------------------------|--------------|-----------------------|----------|----------------|

| AJAV-5501-BLK | 3G Band I Power Amplifier | 3x3 LGA      | -30 to 90 °C          | 100      | Antistatic bag |

| AJAV-5501-TR1 |                           | SXS LGA      |                       | 5000     | Tape & Reel    |

Note: Shipping method is tape and reel, quantity 5000 pieces per reel.