## **Charging System Safety Device**

#### **General Description**

The RT9719 is an integrated circuit (IC) designed to replace passive device in charging system with extra protection function. It is optimized to protect low voltage system from up to 28V high voltage input. The IC monitors the input voltage to make sure all parameters are operating in normal range. It also monitors its own temperature and turn off the MOSFET when the chip temperature exceeds 140°C. When the input voltage exceeds the threshold, the IC turns off the power MOSFET within 1us to remove the power before any damage occurs. User can monitor the adapter input voltage from CHRIN pin which has 50mA current capability. The gate of the P-MOSFET will be controlled by the external charging controller from GATEDRV pin if all parameters are operating in normal range.

The RT9719 is available in SOT-23-6 and WDFN-8L 2x2 tiny packages to achieve best solution for PCB space and total BOM cost saving considerations.

### **Ordering Information**

RT9719 Package Type E : SOT-23-6 QW : WDFN-8L 2x2 (W-Type) Lead Plating System G : Green (Halogen Free and Pb Free) OVP Default : 6.25V A : 7.20V

Note :

Richtek products are :

- RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- Suitable for use in SnPb or Pb-free soldering processes.

### **Marking Information**

For marking information, contact our sales representative directly or through a Richtek distributor located in your area.

#### Features

- No External Blocking Diode Requiring

- $\bullet$  Overvoltage Turn Off Time of Less Than 1 $\mu s$

- High Accuracy Protection Thresholds

- Over Temperature Protection

- High Immunity of False Triggering Under Transients

- Thermal Enhanced SOT-23-6 and 8-Lead WDFN Packages

- RoHS Compliant and Halogen Free

#### Application

- Cellular Phones

- Digital Cameras

- PDAs and Smart Phones

- Portable Instruments

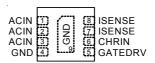

### Pin Configurations

(TOP VIEW)

WDFN-8L 2x2

SOT-23-6

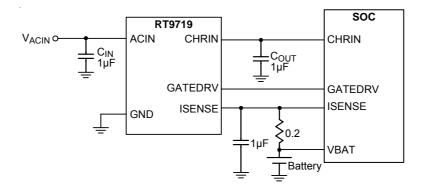

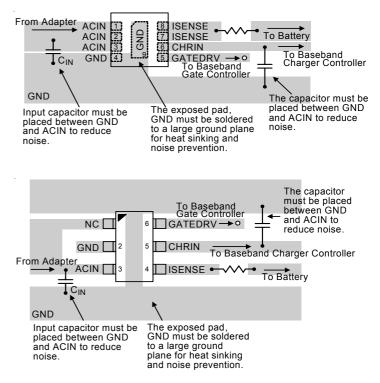

### **Typical Application Circuit**

### **Functional Pin Description**

| Pin No.                                                               |                                                                               | Pin Name                                                                                   | Pin Function                                                                                                    |  |

|-----------------------------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--|

| SOT-23-6                                                              | SOT-23-6 WDFN-8L 2x2                                                          |                                                                                            | Fin Function                                                                                                    |  |

| 1                                                                     |                                                                               | NC                                                                                         | No Internal Connection.                                                                                         |  |

| 2                                                                     | 4                                                                             | GND                                                                                        | Analog Ground.                                                                                                  |  |

| 3                                                                     | 1, 2, 3                                                                       | ACIN                                                                                       | The Input Power Source. The VIN can withstand up to 30V input.                                                  |  |

| 4                                                                     | 7, 8                                                                          | ISENSE                                                                                     | Connect to ISENSE resistor and ISENSE pin of charging controller.                                               |  |

| 5 6 CHRIN Voltage is equal to VIN as VIN in power good range and prov |                                                                               | Voltage is equal to VIN as VIN in power good range and providing ~25mA for system at most. |                                                                                                                 |  |

| 6                                                                     | 6 5 GATEDRV External control pin for controlling the P-MOSFET by charging col |                                                                                            | External control pin for controlling the P-MOSFET by charging controller.                                       |  |

|                                                                       |                                                                               | GND                                                                                        | Ground Pin. The exposed pad must be soldered to a large PCB and connected to GND for maximum power dissipation. |  |

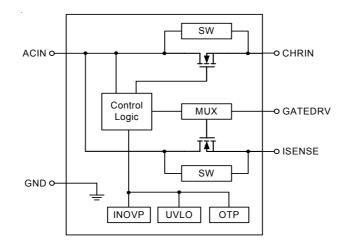

### **Function Block Diagram**

## RICHTEK

# **RT9719**

## Absolute Maximum Ratings (Note 1)

| <ul> <li>Supply Input Voltage, V<sub>IN</sub></li></ul>                                                                           | - –0.3V to 7V<br>- –0.3V to 4.5V |

|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| <ul> <li>Other Finst</li></ul>                                                                                                    | 0.3 v 10 0 v                     |

| SOT-23-6<br>WDFN-8L 2x2<br>• Package Thermal Resistance (Note 2)                                                                  |                                  |

| SOT-23-6, θ <sub>JA</sub>                                                                                                         | - 125°C/W<br>- 150°C             |

| <ul> <li>Lead Temperature (Soldering, 10 sec.)</li> <li>Storage Temperature Range</li> <li>ESD Susceptibility (Note 3)</li> </ul> | - –65°C to 150°C                 |

| HBM (Human Body Mode)<br>MM (Machine Mode)                                                                                        |                                  |

### Recommended Operating Conditions (Note 4)

| Junction Temperature Range | - –40°C to 125°C |

|----------------------------|------------------|

| Ambient Temperature Range  | - –40°C to 85°C  |

#### **Electrical Characteristics**

$(V_{IN} = 5V, T_A = 25^{\circ}C, unless otherwise specified)$

| Parameter                   | Symbol               | Test Conditions  | Min | Тур  | Max | Unit |

|-----------------------------|----------------------|------------------|-----|------|-----|------|

| Power On Reset              |                      |                  |     |      |     |      |

| Rising VIN Threshold        | UVLO                 |                  | 2.5 | 2.7  | 2.9 | V    |

| POR Hysteresis              |                      |                  |     | 100  |     | mV   |

| VIN Bias Current            |                      | When enable      |     | 200  | 600 | μA   |

| Reverse Leakage             | I <sub>LEAKAGE</sub> | As ACIN floating |     | 5    | 10  | μA   |

| Operation Voltage           |                      |                  | 4.3 |      | 6.5 | V    |

| Operation Current           |                      |                  |     |      | 1   | А    |

| Protections                 |                      |                  |     |      |     |      |

| Input OVP Reference Voltage | INOVP                | RT9719           | 6   | 6.25 | 6.5 | V    |

|                             |                      | RT9719A          | 7   | 7.2  | 7.4 | V    |

| Input OVP Hysteresis        |                      |                  |     | 60   | 100 | mV   |

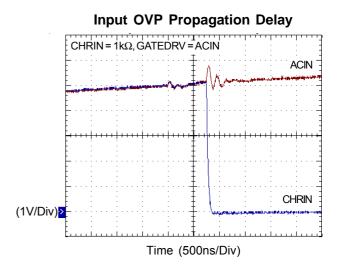

| Input OVP Propagation Delay |                      |                  |     |      | 1   | μS   |

| OTP Rising Thershold        |                      |                  |     | 140  |     | °C   |

| OTP Hysteresis              |                      |                  |     | 20   |     | °C   |

To be continued

## **RT9719**

| Parameter                                     | Symbol                      | Conditions                                      | Min | Тур | Max | Unit |

|-----------------------------------------------|-----------------------------|-------------------------------------------------|-----|-----|-----|------|

| Power MOSFET                                  |                             |                                                 |     |     |     |      |

| R <sub>DS(ON)</sub> Between ACIN to<br>ISENSE | R <sub>DS(ON)</sub> _ISENSE | Measure @ 500mA. 4.3V < V <sub>IN</sub> <<br>6V |     |     | 500 | mΩ   |

| R <sub>DS(ON)</sub> Between ACIN to CHRIN     | Rds(on)_Chrin               | Measure @ 50mA. 4.3V < V <sub>IN</sub> <<br>6V  |     |     | 3   | Ω    |

Note 1. Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- **Note 2.**  $\theta_{JA}$  is measured in the natural convection at  $T_A = 25^{\circ}C$  on a low effective single layer thermal conductivity test board of JEDEC 51-3 thermal measurement standard.

- Note 3. Devices are ESD sensitive. Handling precaution is recommended.

- Note 4. The device is not guaranteed to function outside its operating conditions.

4.7

95 110 125

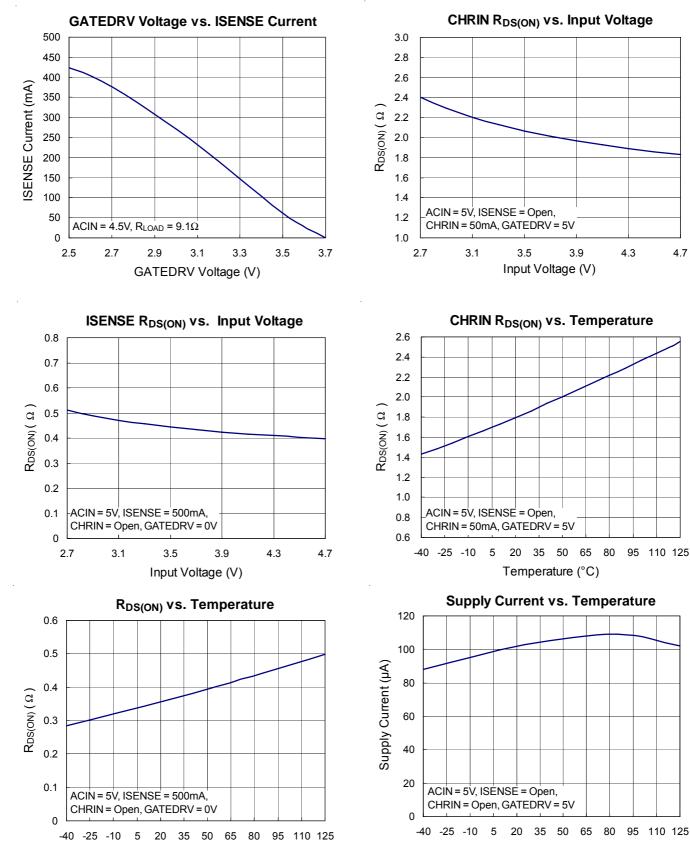

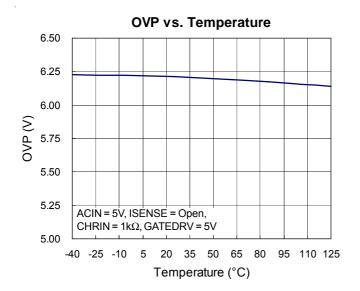

### **Typical Operating Characteristics**

Temperature (°C)

Temperature (°C)

# **RT9719**

#### **Application information**

#### **Operation State**

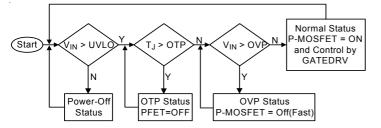

The operation state can be shown as following Figure 1. At power-off state, the RT9719 will check whether V<sub>IN</sub> is > UVLO threshold. If the V<sub>IN</sub> is higher than the UVLO threshold, the RT9719 will check whether the Junction temperature is over the OTP threshold. If the Junction temperature is higher than the OTP threshold, the internal P-MOSFET will be turned off. If the Junction temperature is lower than the OTP threshold, the RT9719 will check whether V<sub>IN</sub> is higher than the OVP threshold or not, if the V<sub>IN</sub> is higher than the OVP threshold, the RT9719 will turn off the internal P-MOSFET immediately within 1us.

And, if all of the checks including  $V_{IN} > UVLO$ ,  $T_J < OTP$ and  $V_{IN} < OVP$  are ok, the IC will operate normally.

Figure 1. Operation State Diagram for OVP Function

#### Input Over Voltage Protection (OVP)

The RT9719 monitors input voltage to prevent the input voltage lead to output system failures. When the input voltage exceeds the threshold, the RT9719 will turn off the power MOSFET within 1us to prevent the high input voltage from damaging the electronics in the handheld system. The hysteresis for the input OVP threshold is 100mV. When the input voltage returns to normal operation voltage range, the RT9719 re-enables the MOSFET. The RT9719 allows the input voltage to rise up to 30V without damaging the IC.

#### **Battery Voltage Monitor**

The RT9719 monitors the battery voltage by the ISENSE pin. When the battery voltage exceeds the voltage level of ( $V_{ACIN} - 0.2V$ ), the RT9719 will turn off the MOSFET and the battery will not be charged. The RT9719 will recharge the battery when the battery voltage is lower than the voltage of ( $V_{ACIN} - 0.2V$ ).

#### **Internal Over Temperature Protection**

The RT9719 monitors its own internal temperature to prevent thermal failures. When the internal temperature reaches 140°C with a built-in hysteresis of 20°C, the IC turns off the power MOSFET. The IC does not resume operation until the internal temperature drops below 120°C.

#### Input Under Voltage Protection (UVLO)

The RT9719 monitors input voltage to prevent the input voltage lead to output system failures. The RT9719 input under voltage protection threshold is set to 2.7V. When the input voltage is under the threshold, the RT9719 will turn off the power MOSFET within 1us. When the input voltage returns to normal operation voltage range, the RT9719 re-enables the MOSFET.

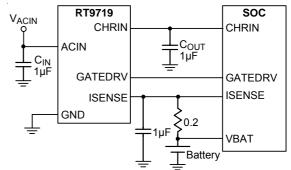

Figure 2. Application Diagram of RT9719 with SOC

Figure 2 shows the connection of RT9719 in a system diagram. The ISENSE pin of the SOC will sense the voltage of the  $0.2\Omega$  sense resistor and the voltage of the VBAT pin. The GATEDRV pin of the SOC can control the MOSFET of the RT9719 to determine the level of the charge current. The power of the SOC is provided by the CHRIN pin of the RT9719. The RT9719 provides OVP function, once the input voltage at the ACIN pin is higher than the OVP level, the RT9719 will be shutdown to prevent the SOC from damaging. If the voltage of the battery connected to the VBAT pin is full, the RT9719 stops charging by turning off the ISENSE pin. Input and output capacitors of 1uF are recommended to place as close to IC as possible.

#### **Thermal Considerations**

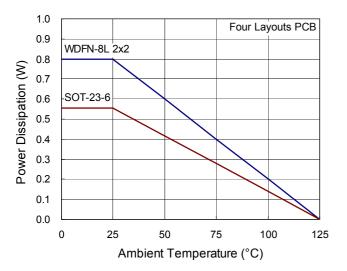

The maximum power dissipation depends on the thermal resistance of IC package, PCB layout, the rate of surroundings airflow and temperature difference between

# **RT9719**

junction to ambient. The maximum power dissipation can be calculated by following formula :

$\mathsf{P}_{\mathsf{D}(\mathsf{MAX})} = (\mathsf{T}_{\mathsf{J}(\mathsf{MAX})} - \mathsf{T}_{\mathsf{A}}) / \theta_{\mathsf{J}\mathsf{A}}$

Where  $T_{J(MAX)}$  is the maximum operation junction temperature,  $T_A$  is the ambient temperature and the  $\theta_{JA}$  is the junction to ambient thermal resistance.

For recommended operating conditions specification of RT9719, where  $T_{J(MAX)}$  is 125°C and  $T_A$  is the operated ambient temperature. The junction to ambient thermal resistance  $\theta_{JA}$  for WDFN-8L 2x2 package is 165°C/W and SOT-23-6 package is 250°C/W on the standard JEDEC 51-3 single-layer thermal test board. The maximum power dissipation at  $T_A$  = 25°C can be calculated by following formula :

$\mathsf{P}_{\mathsf{D}(\mathsf{MAX})}$  = (125°C - 25°C) / (165°C/W) = 0.606 W for WDFN-8L 2x2 packages

$P_{D(MAX)}$  = (125°C - 25°C) / (250°C/W) = 0.400 W for SOT-23-6 packages

The maximum power dissipation depends on operating ambient temperature for fixed  $T_{J(MAX)}$  and thermal resistance  $\theta_{JA}$ . For RT9719 packages, the Figure 3 of derating curves allows the designer to see the effect of rising ambient temperature on the maximum power allowed.

Figure 3. Derating Curves for RT9719 Packages

#### Layout Consideration

The RT9719 is a protection device. Careful PCB layout is necessary. For best performance, place all peripheral components as close to the IC as possible. A short connection is highly recommended. The following guidelines should be strictly followed when designing a PCB layout for the RT9719.

- The exposed pad, GND must be soldered to a large ground plane for heat sinking and noise prevention. The through-hole vias located at the exposed pad is connected to ground plane of internal layer.

- ACIN traces should be wide to minimize inductance and handle the high currents. The trace running from input to chip should be placed carefully and shielded strictly.

- The capacitors must be placed close to the part. The connection between pins and capacitor pads should be copper traces without any through-hole via connection.

Figure 4. PCB Layout Guide

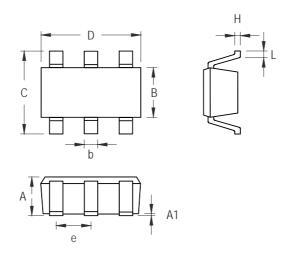

### **Outline Dimension**

| Symbol | Dimensions | n Millimeters | Dimensions In Inches |       |  |

|--------|------------|---------------|----------------------|-------|--|

| Symbol | Min        | Max           | Min                  | Max   |  |

| А      | 0.889      | 1.295         | 0.031                | 0.051 |  |

| A1     | 0.000      | 0.152         | 0.000                | 0.006 |  |

| В      | 1.397      | 1.803         | 0.055                | 0.071 |  |

| b      | 0.250      | 0.560         | 0.010                | 0.022 |  |

| С      | 2.591      | 2.997         | 0.102                | 0.118 |  |

| D      | 2.692      | 3.099         | 0.106                | 0.122 |  |

| е      | 0.838      | 1.041         | 0.033                | 0.041 |  |

| Н      | 0.080      | 0.254         | 0.003                | 0.010 |  |

| L      | 0.300      | 0.610         | 0.012                | 0.024 |  |

SOT-23-6 Surface Mount Package

DETAIL A Pin #1 ID and Tie Bar Mark Options

Note : The configuration of the Pin #1 identifier is optional, but must be located within the zone indicated.

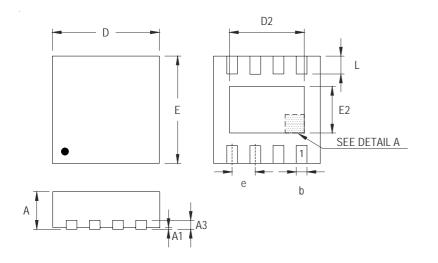

| Symbol | Dimensions | In Millimeters | Dimensions In Inches |       |     |

|--------|------------|----------------|----------------------|-------|-----|

| Symbol | Min        | Max            | Min                  | Max   |     |

| А      | 0.700      | 0.800          | 0.028                | 0.031 |     |

| A1     | 0.000      | 0.050          | 0.000                | 0.002 |     |

| A3     | 0.175      | 0.250          | 0.007                | 0.010 |     |

| b      | 0.200      | 0.300          | 0.008                | 0.012 |     |

| D      | 1.950      | 2.050          | 0.077                | 0.081 |     |

| D2     | 1.000      | 1.250          | 0.039                | 0.049 |     |

| E      | 1.950      | 2.050          | 0.077                | 0.081 |     |

| E2     | 0.400      | 0.650          | 0.016                | 0.026 |     |

| е      | 0.500      |                | 0.500 0.020          |       | )20 |

| L      | 0.300      | 0.400          | 0.012                | 0.016 |     |

W-Type 8L DFN 2x2 Package

#### **Richtek Technology Corporation**

Headquarter 5F, No. 20, Taiyuen Street, Chupei City Hsinchu, Taiwan, R.O.C. Tel: (8863)5526789 Fax: (8863)5526611

#### **Richtek Technology Corporation**

Taipei Office (Marketing) 5F, No. 95, Minchiuan Road, Hsintien City Taipei County, Taiwan, R.O.C. Tel: (8862)86672399 Fax: (8862)86672377 Email: marketing@richtek.com

Information that is provided by Richtek Technology Corporation is believed to be accurate and reliable. Richtek reserves the right to make any change in circuit design, specification or other related things if necessary without notice at any time. No third party intellectual property infringement of the applications should be guaranteed by users when integrating Richtek products into any application. No legal responsibility for any said applications is assumed by Richtek.