### Features

- Two Identical Interface Channels

- Pre-regulated Smoothed Voltage and a Supply Current up to 50 mA for the Sensors

- Data from the Sensors by Current Modulation with a Transmission Rate of 60 kBaud (Transmission Bandwidth 500 kHz)

- TTL-compatible Input Activates the Sensor

- Data Output Can be Directly Connected to a Microcontroller Input

- Operation Supply Voltage Range 5.7 V  $\leq$  V  $_{S}$   $\leq$  40 V

- ESD Protection According to MIL-STD-883C Test Method 3015.7

- High-level EMI Protection

### Benefits

- Simple Wiring Thanks to One Common Line for Supply of the Sensor and Data Transmission from the Sensor to the U6268B

- Current Modulation Provides High Noise Immunity for Data Transfer

### Description

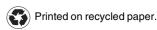

The U6268B is an interface IC for remote automotive sensors. It links the crash sensors in the driver and passenger door with the main airbag unit in the dashboard. Two identical channels supply the external sensors and receive digital information from them via one active wire each. The interface supplies the external sensors with a preregulated smoothed voltage, the external units transmit the digital information back to the interface by current modulation.

As the device is designed for safety-critical applications, the highest data transmission security is mandatory. With high immunity against cross coupling between the two channels, the U6268B is tailored for the harsh automotive environment.

Figure 1. Block Diagram

Side-airbag Sensor Dual Interface

## U6268B

Rev. 4808A-AUTO-06/04

### **Pin Configuration**

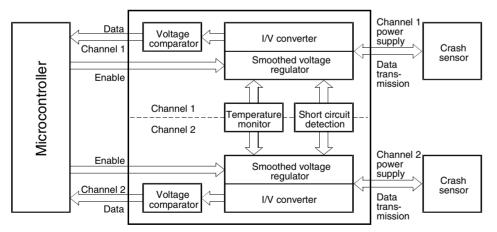

Figure 2. Pinning SO16

### **Pin Description**

| Pin  | Symbol  | Function                                                                                       |  |  |  |

|------|---------|------------------------------------------------------------------------------------------------|--|--|--|

| 1    | GND     | around and reference pin                                                                       |  |  |  |

| 2    | RETURN1 | turn line of the external unit, internally connected to GND via a line-protection transistor   |  |  |  |

| 3    | OUT1    | Voltage-stabilized supply output and current-modulation input                                  |  |  |  |

| 4    | VS      | Supply voltage of the IC                                                                       |  |  |  |

| 5    | OUT2    | Voltage-stabilized supply output and current-modulation input                                  |  |  |  |

| 6    | SC      | Smooth time constant for slow voltage change at both OUT pins                                  |  |  |  |

| 7    | RETURN2 | Return line of the external unit, internally connected to GND via a line-protection transistor |  |  |  |

| 8, 9 | GND     | round and reference pin                                                                        |  |  |  |

| 10   | ENABLE2 | Controls OUT1 voltage<br>ENABLE1 High = OUT1 active, ENABLE1 Low or open = OUT1 switched off   |  |  |  |

| 11   | CLL2    | rent logic level output (low at high OUT2 current, monitoring via OCM2)                        |  |  |  |

| 12   | OCM2    | Analog current output, representing 1/10 current of OUT2                                       |  |  |  |

| 13   | OCM1    | Analog current output, representing 1/10 current of OUT1                                       |  |  |  |

| 14   | CLL1    | Current logic level output (low at high OUT1 current, monitoring via OCM1)                     |  |  |  |

| 15   | ENABLE1 | Controls OUT2 voltage<br>ENABLE2 High = OUT2 active, ENABLE1 Low or open = OUT2 switched off   |  |  |  |

| 16   | GND     | Ground and reference pin                                                                       |  |  |  |

# U6268B

2

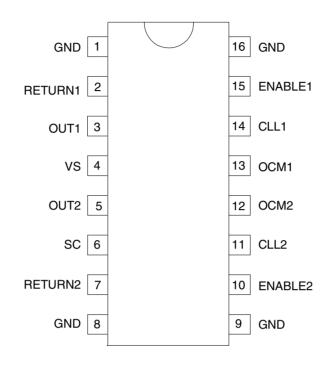

#### Figure 3. Functional Block Diagram

### **Functional Description**

٧s

The IC and the external units are powered via the V<sub>S</sub> pin 4. This pin is connected to the battery via a reverse battery protection diode. An electrolythic capacitor of 22  $\mu$ F smoothes the voltage and absorbes positive and negative transients.

**OUT1, OUT2** OUTx provides a smoothed, very slowly changing supply voltage for the external units and monitors the output current. During normal operating conditions, the OUTx voltage is typically 3 V below V<sub>S</sub>, and changes very slowly with a varying battery voltage in order to suppress disturbances in the data transmission. At low V<sub>S</sub> (5.7 to 8.5 V), the OUTx voltage is typically 0.5 V below V<sub>S</sub>. This voltage difference is reduced in to ensure sufficient supply voltage for the external unit between OUTx and RETURNx. The output current capability is 50 mA. The internal pull-down current at OUTx is typically 3 mA.

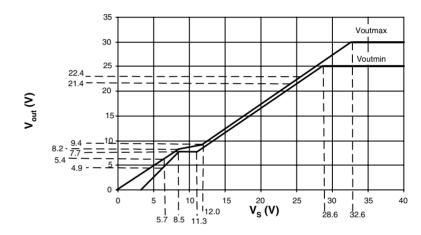

Figure 4. Output Voltage with Tolerances versus Supply Voltage

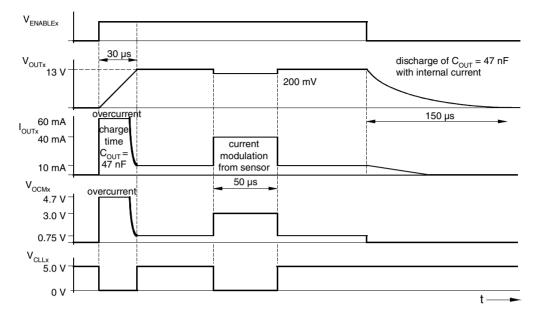

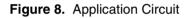

The data transmission from the external unit to the interface IC is carried out on the same line by varying the current level. The quiescent current consumption of the external unit is about 5 to 15 mA. This current level is interpreted as logic high level at the CLL pin. The external unit can switch on an additional current of 30 mA, interpreted by the interface as logic low. The slope time of the current pulse is approximately 1  $\mu$ s which is suitable for a transmission rate up to 60 kBaud. The necessary transmission bandwidth of greater than 500 kHz between OUTx and OCMx is guaranteed (see "Application Circuit" on page 12). To achieve good current transmission behavior, the dynamic resistance of OUTx may not exceed 12  $\Omega$  within the bandwidth range (total of 15  $\Omega$  for OUTx and RETURN).

The OUTx voltage can be switched off by ENABLEx = LOW to reset the external unit and to reduce power dissipation during fault conditions.

The OUT pins are protected against overtemperature and short circuits. A reverse polarity diode at pin V<sub>S</sub> (pin 4) ensures that no current is fed back to the V<sub>Batt</sub> system in the case of a short between OUTx and V<sub>Batt</sub>. A minimum capacity of 33 nF is required at the pins OUTx.

Δ

| ENABLE1, ENABLE2   | ENABLEx is a microcontroller-compatible input which switches the related output on or off.                                                                                                                                                                                                                                                                                                                     |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | <ul> <li>A low or open circuit applied to ENABLEx switches off the related OUTx and<br/>RETURNx (high impedance). A sink current at pin OUTx discharges the capacitive<br/>load.</li> </ul>                                                                                                                                                                                                                    |

|                    | • A high applied to ENABLEx switches on the related OUTx and RETURNx to supply the external unit.                                                                                                                                                                                                                                                                                                              |

| OCM1, OCM2         | The output current of OUTx is monitored with a transmission factor of 0.1 to the OCMx. With a resistor from OCM to GND, the current is converted to a voltage. The electrical characteristics are specified by $R_{OCM}$ = 750 $\Omega$ . The CLL-current threshold, the OUT-current limitation and the OUT-current detection can be changed by varying $R_{OCM}$ in a range of 500 $\Omega$ to 1 k $\Omega$ . |

|                    | Current monitoring enables the device to detect overcurrent conditions at OUTx (short-circuit to GND or RETURNx) and low current conditions at OUTx (short-circuit to $V_{Batt}$ or open load).                                                                                                                                                                                                                |

|                    | The internal pull-down current at OUTx creates no OCMx-current. During ENABLE, the minimum voltage at OCMx is the saturation voltage of an internal NPN-transistor with typically 0.1 V. The maximum voltage at OCM is limited by an internal clamping diode to 5.3 V.                                                                                                                                         |

| CLL1, CLL2         | The current at pin OUTx is evaluated logically and ready to use for a microcontroller input. With this stage, the logic data transmission from the external unit to the interface is completed.                                                                                                                                                                                                                |

|                    | CLLx is the output stage of a comparator with an internal threshold and with the OCMx input. A OCMx voltage higher than 2.4 V creates a logic low at CLLx, and a OCMx voltage lower than 1.43 V creates a logic high at CLLx. The comparator has an internal hysteresis of typically 0.4 V.                                                                                                                    |

|                    | With the pull-down resistor $R_{OCMx} = 750 \ \Omega$ at OCMx, the correct OUTx-current threshold related to the logical output CLLx is ensured. The CLLx is low if the OUTx-current is higher than 27.3 mA, and the CLLx is "high", if the OUTx-current is lower than 19.1 mA. The comparator has an internal hysteresis of typically 5 mA. The tolerance of the ROCM resistor is assumed to be 0%.           |

|                    | The CLL pin is an open-collector output and needs a pull-up resistor of typically 2 k $\Omega$ to the 5-V supply. For ESD protection, a 7-V Zener diode is implemented.                                                                                                                                                                                                                                        |

| RETURN 1, RETURN 2 | The RETURNx pin provides a low-ohmic connection to GND via a switched open-collector NPN-transistor. If ENABLEx is high, RETURNx is switched on with a saturation voltage of less than 0.5 V at $I_{RETURNx} \leq 50$ mA. If ENABLEx is low or open, RETURNx is a current sink with $\leq 2$ mA. RETURNx is current-limited at typically 150 mA.                                                               |

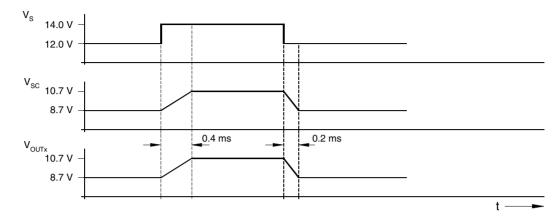

| SC                 | The smooth capacitor is designed to realize the long-time constant for the slow voltage change at OUTx for both interface channels. The capacity is typically 22 nF. At the rising edge of V <sub>Batt</sub> , the maximum slew rate is V <sub>OUTx</sub> = 5 V/ms, and at the falling edge of V <sub>Batt</sub> , the maximum slew rate is V <sub>OUTx</sub> = 10 V/ms.                                       |

# **A**MEL<sub>®</sub>

| GND Pins          | A GND bond from the chip to pin 1 and pin 8 provides high ground breakage security and the lowest voltage drop and ground shift between the IC and circuit ground. The four GND pins and the die pad are directly connected to the copper leadframe, resulting in a very low thermal resistance, $R_{thJC}$ . To also achieve a low ambient thermal resistance ( $R_{thJA}$ ) it is recommended metal parts of the housing be connected in a proper way with the GND pins. |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power Dissipation | Worst case calculation of the supply current I <sub>S</sub> :                                                                                                                                                                                                                                                                                                                                                                                                              |

|                   | $I_{S} = 1,278 \times (I_{OUT1} + I_{OUT2}) + 18 \text{ mA}$                                                                                                                                                                                                                                                                                                                                                                                                               |

|                   | Worst case calculation of the IC's power dissipation $P_{V}$ :                                                                                                                                                                                                                                                                                                                                                                                                             |

|                   | $P_{V} = (V_{S} \times I_{S}) - [(V_{S} - V_{diff} - V_{ret-sat}) \times (I_{OUT1} + I_{OUT2}) + R_{OCM} \times ((I_{OUT1}^{2} + I_{OUT2}^{2})/81)]$                                                                                                                                                                                                                                                                                                                       |

|                   | $V_{S} = Supply \text{ voltage } (5.7 \text{ to } 25 \text{ V})$                                                                                                                                                                                                                                                                                                                                                                                                           |

|                   | $V_{diff} = V_{S}$ to $V_{OUTx}$ voltage difference                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                   | $V_{diff} = 3.6 \text{ V} \text{ at } 12 \text{ V} \le V_{S} \le 25 \text{ V}$                                                                                                                                                                                                                                                                                                                                                                                             |

|                   | $V_{diff} = 0.8 \text{ V at } 5.7 \text{ V} \le V_{S} \le 8.5 \text{ V}$                                                                                                                                                                                                                                                                                                                                                                                                   |

|                   | V <sub>ret-sat</sub> = 0.5 V saturation voltage return                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                   | $I_{OUTx}$ = output current at pin OUTx = 0 to 60 mA                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                   | R <sub>OCM</sub> = resistor at pin OCMx                                                                                                                                                                                                                                                                                                                                                                                                                                    |

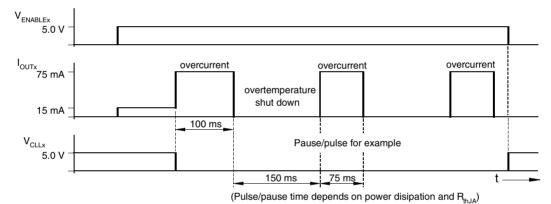

|                   | An integrated overtemperature protection generates a switch-off signal at a chip temper-<br>ature of typically $T_j = 160^{\circ}$ C and a switch-on signal at typically $T_j = 150^{\circ}$ C.                                                                                                                                                                                                                                                                            |

|                   | If overtemperature is detected, only the corresponding channel will be disabled. The other channel stays enabled.                                                                                                                                                                                                                                                                                                                                                          |

|                   | The RETURNx is switched off if the voltage at RETURNx exceeds 2 V (short-circuit comparator threshold) and overtemperature is detected.                                                                                                                                                                                                                                                                                                                                    |

|                   | The OUTx is switched off if the voltage at OCMx is higher than 4.6 V (overcurrent detec-<br>tion level) and overtemperature is detected. The OCM voltage monitors the output<br>current at OUTx via the current ratio of 0.1. The overcurrent-detection level of OUTx can<br>be varied by changing the OCMx resistor. If OUTx is switched off by overtemperature<br>and overcurrent detection, the CLLx output remains a logic low (overcurrent).                          |

|                   | As the IC is only overtemperature-protected against short-circuit conditions at RETURNx or OUTx, it has to be checked in each application that the chip temperature does not exceed $T_{jmax} = 150^{\circ}$ C in normal operation.                                                                                                                                                                                                                                        |

| Test Hint         | The overtemperature signal can be activated by connecting ENABLE1 or ENABLE2 to 9 V/10 mA.                                                                                                                                                                                                                                                                                                                                                                                 |

### **Absolute Maximum Ratings**

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Parameters                                                                                                | Symbol                                    | Min.               | Max.     | Unit     |

|-----------------------------------------------------------------------------------------------------------|-------------------------------------------|--------------------|----------|----------|

| Supply voltage                                                                                            | Vs                                        | -0.6               | 40       | V        |

| Voltage at pins CLL1, CLL2, ENABLE1, ENABLE2                                                              |                                           | -0.3               | 6        | V        |

| Voltage at SC                                                                                             | V <sub>SC</sub>                           | -0.3               | 30       | V        |

| Voltage at OCM1, OCM2                                                                                     | V <sub>OCMx</sub>                         | -0.3               | 6.8      | V        |

| Voltage at RETURN1, RETURN2                                                                               | V <sub>RETURNx</sub>                      | -1                 | 27       | V        |

| Voltage at OUT1, OUT2                                                                                     | V <sub>OUTx</sub>                         | -1                 | 40       | V        |

| Current at supply (both channels OUTx and RETURNx shorted)                                                | ۱ <sub>s</sub>                            |                    | 240      | mA       |

| Current at logical pins: CLL1, CLL2<br>ENABLE1, ENABLE2                                                   | I <sub>CCLx</sub><br>I <sub>ENABLEx</sub> |                    | 3<br>0.1 | mA<br>mA |

| Current at SC (SC related to GND or V <sub>Batt</sub> )                                                   | I <sub>SC</sub>                           | -110               | 220      | μA       |

| Current at pins to external unit<br>OUT1, OUT2, RETURN1, RETURN2                                          |                                           | Internally limited |          |          |

| ESD classification<br>Human body model (100 pF, 1.5 k $\Omega$ )<br>Machine model (200 pF, 0.0 $\Omega$ ) | All pins                                  | ±2000<br>±200      |          | v<br>v   |

| Ambient temperature range                                                                                 | T <sub>amb</sub>                          | -40                | 95       | °C       |

| Junction temperature range                                                                                | Τ <sub>j</sub>                            | -40                | 150      | °C       |

| Storage temperature range                                                                                 | T <sub>stg</sub>                          | -55                | 125      | °C       |

### Thermal Resistance<sup>(1)</sup>

| Parameters    | Symbol            | Value | Unit |

|---------------|-------------------|-------|------|

| Junction case | R <sub>thJC</sub> | 36    | K/W  |

Note: 1. A good ambient thermal resistance junction (R<sub>thJA</sub> = 65 K/W) can be achieved by using a big pad size for ground connection near a metal component (see section "GND Pins" on page 6)

### **Electrical Characteristics**

$T_{amb}$  = -40°C to 95°C and  $T_j$  = -40°C to 150°C, Operation supply-voltage range V<sub>S</sub> = 5.7 to 18 V continuously, V<sub>S</sub> ≤ 25 V for maximum 25 min, V<sub>S</sub> ≤ 40 V for up to 500 ms. The current values are based on R = 750 Ω, 0%-resistor at OCM1/OCM2 pins.

| Parameters                                                     | Test Conditions                                                                                                                                                                                                                                                  | Symbol                                          | Min.                  | Тур. | Max.                 | Unit     |

|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|-----------------------|------|----------------------|----------|

|                                                                | Outputs disabled, $V_S \le 18 V$                                                                                                                                                                                                                                 | ۱ <sub>S</sub>                                  |                       |      | 8                    | mA       |

|                                                                | Outputs disabled, $V_S \le 40 V$                                                                                                                                                                                                                                 | ا <sub>s</sub>                                  |                       |      | 14                   | mA       |

|                                                                | One output enabled, $V_S \le 18 \text{ V}$                                                                                                                                                                                                                       | ۱ <sub>s</sub>                                  |                       |      | 13                   | mA       |

|                                                                | Both outputs enabled, $V_S \le 18 \text{ V}$                                                                                                                                                                                                                     | ا <sub>s</sub>                                  |                       |      | 18                   | mA       |

| Supply Current                                                 | Output load 2 $\times$ 15 mA, V <sub>S</sub> $\leq$ 18 V                                                                                                                                                                                                         | ۱ <sub>s</sub>                                  |                       |      | 56                   | mA       |

| $T_i \ge 125^{\circ}C$                                         | Output load 2 $\times$ 28 mA, V <sub>S</sub> $\leq$ 18 V                                                                                                                                                                                                         | ا <sub>s</sub>                                  |                       |      | 90                   | mA       |

| ,                                                              | Output load 2 $\times$ 50 mA, V <sub>S</sub> $\leq$ 18 V                                                                                                                                                                                                         | ۱ <sub>s</sub>                                  |                       |      | 146                  | mA       |

|                                                                | Output load 2 × 60 mA,<br>V <sub>S</sub> $\leq$ 18 V (T <sub>j</sub> > 125°C)                                                                                                                                                                                    | ۱ <sub>S</sub>                                  |                       |      | 171                  | mA       |

|                                                                | Both channels OUTx and RETURNx shorted, $V_S \le 18$ V                                                                                                                                                                                                           | ۱ <sub>S</sub>                                  |                       |      | 200                  | mA       |

| Function SC                                                    | · ·                                                                                                                                                                                                                                                              |                                                 |                       | •    | •                    |          |

| Voltage at SC                                                  | V <sub>S</sub> = 5.7 V                                                                                                                                                                                                                                           | V <sub>SC</sub>                                 | 5.1                   |      | 5.3                  | V        |

| Voltage at SC                                                  | V <sub>S</sub> = 12.5 V                                                                                                                                                                                                                                          | V <sub>SC</sub>                                 | 9                     |      | 9.4                  | V        |

| Maximal voltage at SC                                          | V <sub>S</sub> = 40 V                                                                                                                                                                                                                                            | V <sub>SCmax</sub>                              |                       |      | 30                   | V        |

| SC-discharge current                                           | Voltage SC = $V_{SC}$ - 3 V<br>5.7 V $\leq V_S \leq 40$ V                                                                                                                                                                                                        | I <sub>SC_dis</sub>                             | 33                    |      | 82                   | μA       |

| SC-charge current                                              | Voltage SC = $V_{SC}$ - 3 V<br>5.7 V $\leq V_S \leq 40$ V                                                                                                                                                                                                        | I <sub>SC_ch</sub>                              | -58                   |      | -20                  | μA       |

| Function OUT1 and OUT2 (See Fig                                | jure 4 on page 4)                                                                                                                                                                                                                                                |                                                 |                       |      |                      |          |

| Voltage difference, $V_S$ to $V_{OUTx}$                        | $I_{OUTx} = 5 \text{ to } 50 \text{ mA}$<br>5.7 V $\le$ V <sub>S</sub> $\le$ 8.5 V<br>12 V $\le$ V <sub>S</sub> $\le$ 25 V                                                                                                                                       | V <sub>diff_low</sub><br>V <sub>diff_high</sub> | 0.3<br>2.6            |      | 0.8<br>3.6           | V<br>V   |

| Output voltage OUTx                                            | 8.5 V ≤ V <sub>S</sub> ≤ 11.3 V                                                                                                                                                                                                                                  | V <sub>OUT_med</sub>                            | 7.7                   |      |                      | V        |

| Maximal voltage at OUTx                                        | V <sub>S</sub> = 40 V                                                                                                                                                                                                                                            | V <sub>OUT_max</sub>                            | 25                    |      | 30                   | V        |

| Current mirror ratio, I <sub>OCMx</sub> /I <sub>OUTx</sub>     | $ \begin{array}{l} V_{S} \leq 40 \text{ V}, \text{ I}_{OUTx} = 5 \text{ to } 15 \text{ mA} \\ V_{S} \leq 25 \text{ V}, \text{ I}_{OUTx} = 15 \text{ to } 50 \text{ mA} \\ V_{S} \leq 40 \text{ V}, \text{ I}_{OUTx} = 15 \text{ to } 50 \text{ mA} \end{array} $ | I <sub>OUT_ratio</sub>                          | 0.09<br>0.10<br>0.097 |      | 0.12<br>0.11<br>0.11 |          |

| Linearity of mirror ratio I <sub>OCMx</sub> /I <sub>OUTx</sub> |                                                                                                                                                                                                                                                                  | Ratio_lin                                       | -5                    |      | 5                    | %        |

| Dynamic resistance OUTx                                        | $V_{S} \le 40 \text{ V}$<br>$I_{OUT} = 15 \text{ to } 50 \text{ mA}$                                                                                                                                                                                             | R <sub>OUT</sub>                                | 2                     |      | 12                   | Ω        |

| Dynamic resistance<br>OUTx + RETURNx                           | $V_{S} \le 40 \text{ V}$<br>$I_{OUT} = 15 \text{ to } 50 \text{ mA}$                                                                                                                                                                                             | $R_Dyn$                                         | 4                     |      | 15                   | Ω        |

| OUTx current limitation<br>(OUTx short to GND)                 | $\begin{array}{c} V_{S} \leq 18 \text{ V} \\ V_{S} \leq 40 \text{ V} \end{array}$                                                                                                                                                                                | I <sub>OUT_lim</sub>                            | -80<br>-105           |      | -60<br>-60           | mA<br>mA |

|                                                                | T <sub>j</sub> < 125°C                                                                                                                                                                                                                                           | I <sub>OUT_det</sub>                            | -70                   |      | -51                  | mA       |

| Overcurrent detection level                                    | $T_j \ge 125^{\circ}C$<br>Always valid: current limitation is<br>higher than overcurrent detection                                                                                                                                                               | I <sub>OUT_det</sub>                            | -60                   |      | -51                  | mA       |

| Maximum OUTx current<br>(OUTx short to GND)                    | $V_{S}$ = 14 V, OCMx shorted to GND                                                                                                                                                                                                                              | I <sub>OUT_max</sub>                            | -140                  |      | -85                  | mA       |

U6268B

### **Electrical Characteristics (Continued)**

$T_{amb}$  = -40°C to 95°C and  $T_j$  = -40°C to 150°C, Operation supply-voltage range V<sub>S</sub> = 5.7 to 18 V continuously, V<sub>S</sub> ≤ 25 V for maximum 25 min, V<sub>S</sub> ≤ 40 V for up to 500 ms. The current values are based on R = 750  $\Omega$ , 0%-resistor at OCM1/OCM2 pins.

| Parameters                                                                     | Test Conditions                                                                                                                | Symbol                                                               | Min.                 | Тур. | Max.                | Unit           |

|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|----------------------|------|---------------------|----------------|

| Leakage current at disabled OUTx                                               | OUTx short to GND, $V_S \le 25 V$<br>OUTx short to GND, $V_S \le 38.5 V$                                                       | I <sub>OUT_leak</sub>                                                | -0.02<br>-12         |      |                     | mA<br>mA       |

| Leakage voltage at disabled OUTx                                               | OUTx open, V <sub>S</sub> ≤38.5 V                                                                                              | V <sub>OUT_leak</sub>                                                |                      |      | 4.3                 | V              |

| Internal pull-down current                                                     | $V_{S} \le 18 V$<br>$V_{S} \le 40 V$                                                                                           | I <sub>OUT_sink</sub>                                                | 1.8<br>2.5           |      | 4<br>4.5            | mA<br>mA       |

| Supply rejection ratio                                                         | V <sub>SC</sub> = 7.6 V                                                                                                        | V <sub>rej_mV</sub>                                                  |                      |      | 80                  | mV             |

| Supply rejection ratio                                                         | Variation of V <sub>S</sub> = 8.4 V to 40 V<br>in 10 ms                                                                        | V <sub>rej_dB</sub>                                                  | 51.9                 |      |                     | dB             |

| Minimum capacity at OUTx for phase margin                                      |                                                                                                                                | C <sub>OUT_min</sub>                                                 | 33                   |      |                     | nF             |

| Delay time with $C_{out} = 47 \text{ nF}$                                      | Switching on ENABLE = 1 to 90%<br>$V_{OUT}$ reached<br>Switching off ENABLE = 0 to 10%                                         | Enable_on<br>Enable_off                                              | 3<br>30              |      | 30<br>100           | µs<br>µs       |

|                                                                                | V <sub>OUT</sub> reached                                                                                                       |                                                                      |                      |      |                     |                |

| Function OCM1, OCM2                                                            |                                                                                                                                |                                                                      |                      |      |                     |                |

| Voltage threshold CLL-comparator                                               | CLLx low-level voltage threshold<br>CLLx high-level voltage threshold<br>Voltage hysteresis                                    | V <sub>CLL_L</sub><br>V <sub>CLL_H</sub><br>V <sub>CLL_hys</sub>     | 1.75<br>1.43<br>0.26 |      | 2.4<br>1.9<br>0.6   | V<br>V<br>V    |

| Minimum voltage at OCMx                                                        | I <sub>OUT</sub> = 0 to 5 mA                                                                                                   | V <sub>OCM_min</sub>                                                 |                      |      | 0.5                 | V              |

| Current-limitation level                                                       | $V_{S} \le 40$ V, OUTx short to GND                                                                                            | V <sub>OCM_lim</sub>                                                 | 4.3                  |      | 5.3                 | V              |

| Overcurrent-detection level                                                    | V <sub>S</sub> ≤40 V                                                                                                           | V <sub>OCM_det</sub>                                                 | 4.2                  |      | 4.9                 | V              |

| Current limitation minus overcurrent detection                                 | V <sub>OCM_lim</sub> - V <sub>OCM_over</sub>                                                                                   | $\Delta_{\text{lim}}_{\text{OCM}}$                                   | 0.15                 |      | 0.5                 | V              |

| Internal pull-down current                                                     |                                                                                                                                | I <sub>OCM_sink</sub>                                                | 0.1                  |      | 0.45                | mA             |

| Function RETURN1, RETURN2                                                      |                                                                                                                                | L.                                                                   |                      |      |                     |                |

| Enable high saturation voltage                                                 | I <sub>RETURN</sub> = 50 mA                                                                                                    | V <sub>ret_sat</sub>                                                 |                      |      | 0.5                 | V              |

| Dynamic resistance                                                             | dI ≥ 10 mA                                                                                                                     | R <sub>ret</sub>                                                     | 2                    |      | 8                   | Ω              |

| Current limitation<br>RETURNx is always higher than<br>current limitation OUTx | Enable high, V <sub>RETURNx</sub> = 2 V<br>Enable high, V <sub>RETURNx</sub> ≤ 18 V<br>Enable low, V <sub>RETURNx</sub> ≤ 18 V | I <sub>ret_lim</sub><br>I <sub>ret_lim</sub><br>I <sub>ret_low</sub> | 60<br>70<br>0.8      |      | 150<br>200<br>2     | mA<br>mA<br>mA |

| Overcurrent-detection level                                                    | Threshold comparator,<br>switch-off return<br>Threshold comparator,                                                            | V <sub>ret_low</sub><br>V <sub>ret_high</sub>                        | 1.4<br>1.1           |      | 2<br>1.5            | v<br>v         |

|                                                                                | switch-on return<br>Hysteresis                                                                                                 | V <sub>ret_hys</sub>                                                 | 0.2                  |      | 0.7                 | v              |

| Delay time<br>C <sub>RETURN</sub> = 47 nF                                      | Switching on I <sub>RETURN</sub> at 50 mA<br>Switching off I <sub>RETURN</sub> at 1 mA                                         | t <sub>dRet_on</sub><br>t <sub>dRet_off</sub>                        | 3<br>30              |      | 30<br>90            | μs<br>μs       |

| Function CLL1, CLL2 (CLLx with 2 k                                             | $\Omega$ to 5 V)                                                                                                               | •                                                                    |                      | -    |                     |                |

| I <sub>OUT</sub> threshold CLL comparator                                      | $R_{OCM} = 750 \Omega$<br>CLL low-level threshold<br>CLL high-level threshold<br>Hysteresis                                    | I <sub>CLL_L</sub><br>I <sub>CLL_H</sub><br>I <sub>CLL_hys</sub>     | 23.3<br>19.1<br>3.5  |      | 27.3<br>22.3<br>8.2 | mA<br>mA<br>mA |

| CLL saturation voltage                                                         | I <sub>CLL</sub> ≤2.5 mA                                                                                                       | V <sub>CLL_sat</sub>                                                 |                      |      | 0.4                 | V              |

|  | l |

|--|---|

|  |   |

|  |   |

|  |   |

|  | R |

### **Electrical Characteristics (Continued)**

$T_{amb}$  = -40°C to 95°C and  $T_j$  = -40°C to 150°C, Operation supply-voltage range V<sub>S</sub> = 5.7 to 18 V continuously, V<sub>S</sub>≤25 V for maximum 25 min, V<sub>S</sub>≤40 V for up to 500 ms. The current values are based on R = 750 Ω, 0%-resistor at OCM1/OCM2 pins.

| Parameters                                                                                                     | Test Conditions                                                                                                                                                                                                                   | Symbol                                                                      | Min.            | Тур. | Max.             | Unit           |

|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------|------|------------------|----------------|

| CLL leakage current                                                                                            | $V_{CLL} \leq 6.5 V$                                                                                                                                                                                                              | I <sub>CLL_leak</sub>                                                       |                 |      | 1                | μA             |

| Response time to current change                                                                                | I <sub>OUT</sub> to CLL rise<br>I <sub>OUT</sub> to CLL fall<br>Maximum difference between rise and<br>fall time                                                                                                                  | t <sub>CII_rise</sub><br>t <sub>CII_fall</sub><br>t <sub>∆</sub> -rise-fall | 0.1<br>0.1      |      | 2<br>2<br>1      | μs<br>μs<br>μs |

| CLL output switching speed                                                                                     | Rise<br>Fall                                                                                                                                                                                                                      | t <sub>CLL_rise</sub><br>t <sub>CLL-fall</sub>                              |                 |      | 1<br>1           | μs<br>μs       |

| Current transmission rate                                                                                      |                                                                                                                                                                                                                                   |                                                                             | 60              |      |                  | kHz            |

| Current transmission 3 dB bandwidth                                                                            |                                                                                                                                                                                                                                   |                                                                             | 500             |      |                  | kHz            |

| Function ENABLE1, ENABLE2                                                                                      |                                                                                                                                                                                                                                   |                                                                             | 1               | 1    | 1                | 1              |

| Enable high-level threshold                                                                                    |                                                                                                                                                                                                                                   | $V_{\text{Enable_on}}$                                                      | 2               |      | 6.5              | V              |

| Enable low-level threshold                                                                                     |                                                                                                                                                                                                                                   | V <sub>Enable_off</sub>                                                     | -0.3            |      | 0.8              | V              |

| Enable input pull-down current<br>(to ensure output disabled during<br>power-off and reset of microcontroller) |                                                                                                                                                                                                                                   | I <sub>Enable</sub>                                                         | 10              |      | 100              | μA             |

| Power Dissipation                                                                                              |                                                                                                                                                                                                                                   |                                                                             | 1               | 1    | 1                | 1              |

| Power dissipation 1<br>$T_j \ge 125^{\circ}C$                                                                  | $\begin{split} V_{S} &= 18 \text{ V}, \\ I_{OUT1} &= 28 \text{ mA}, \\ I_{OUT2} \text{ at overcurrent detection level} \\ \text{or} \\ I_{OUT2} &= 28 \text{ mA}, \\ I_{OUT1} \text{ at overcurrent detection level} \end{split}$ | P <sub>dis1</sub>                                                           |                 |      | 1                | w              |

| Power dissipation 2<br>$T_j \ge 125^{\circ}C$                                                                  | $V_{\rm S}$ = 18 V,<br>$I_{\rm OUT1}$ = $I_{\rm OUT2}$ = 28 mA                                                                                                                                                                    | P <sub>dis2</sub>                                                           |                 |      | 0.75             | W              |

| Selective Overtemperature Protection                                                                           | in .                                                                                                                                                                                                                              |                                                                             |                 |      |                  |                |

| Logic AND connected with overcurrent detection (RETURNx, OUTx)                                                 | Switch off<br>Switch on<br>Hysteresis                                                                                                                                                                                             | Temp_off<br>Temp_on<br>Temp_hys                                             | 155<br>145<br>5 |      | 165<br>155<br>20 | ℃<br>℃<br>℃    |

| Time delay until overtemperature shut-down                                                                     | $V_{S} = 25 V$ , $T_{amb} = 125^{\circ}C$<br>OUT1 = OUT2 = GND                                                                                                                                                                    | t <sub>del</sub>                                                            | 100             |      |                  | ms             |

### **Timing Diagrams**

Figure 5. Variation of Power Supply

#### Figure 6. Overcurrent Protection

#### Figure 7. Data Transmission

### **Ordering Information**

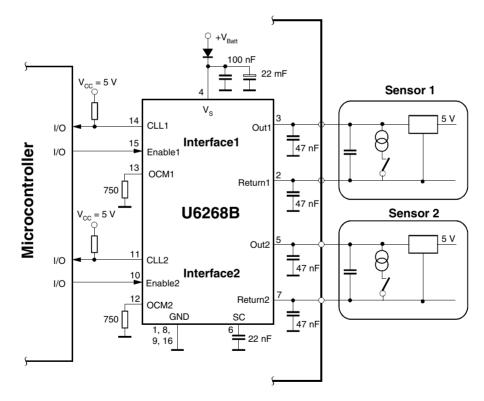

| Extended Type Number | Package | Remarks |

|----------------------|---------|---------|

| U6268B-FP            | SO16    | _       |

### **Package Information**

#### **Atmel Corporation**

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

#### **Regional Headquarters**

#### Europe

Atmel Sarl Route des Arsenaux 41 Case Postale 80 CH-1705 Fribourg Switzerland Tel: (41) 26-426-5555 Fax: (41) 26-426-5500

#### Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong Kong Tel: (852) 2721-9778 Fax: (852) 2722-1369

#### Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

#### **Atmel Operations**

*Memory* 2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

#### Microcontrollers

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

La Chantrerie BP 70602 44306 Nantes Cedex 3, France Tel: (33) 2-40-18-18-18 Fax: (33) 2-40-18-19-60

#### ASIC/ASSP/Smart Cards

Zone Industrielle 13106 Rousset Cedex, France Tel: (33) 4-42-53-60-00 Fax: (33) 4-42-53-60-01

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

Scottish Enterprise Technology Park Maxwell Building East Kilbride G75 0QR, Scotland Tel: (44) 1355-803-000 Fax: (44) 1355-242-743

#### **RF**/Automotive

Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany Tel: (49) 71-31-67-0 Fax: (49) 71-31-67-2340

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

#### Biometrics/Imaging/Hi-Rel MPU/ High Speed Converters/RF Datacom Avenue de Rochepleine BP 123 38521 Saint-Egreve Cedex, France Tel: (33) 4-76-58-30-00 Fax: (33) 4-76-58-34-80

*Literature Requests* www.atmel.com/literature

**Disclaimer:** Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in Atmel's Terms and Conditions located on the Company's web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel's products are not authorized for use as critical components in life support devices or systems.

#### © Atmel Corporation 2004. All rights reserved.

Atmel® and combinations thereof are the registered trademarks of Atmel Corporation or its subsidiaries.

Other terms and product names may be the trademarks of others.